Устройство для моделирования сетевого графика

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

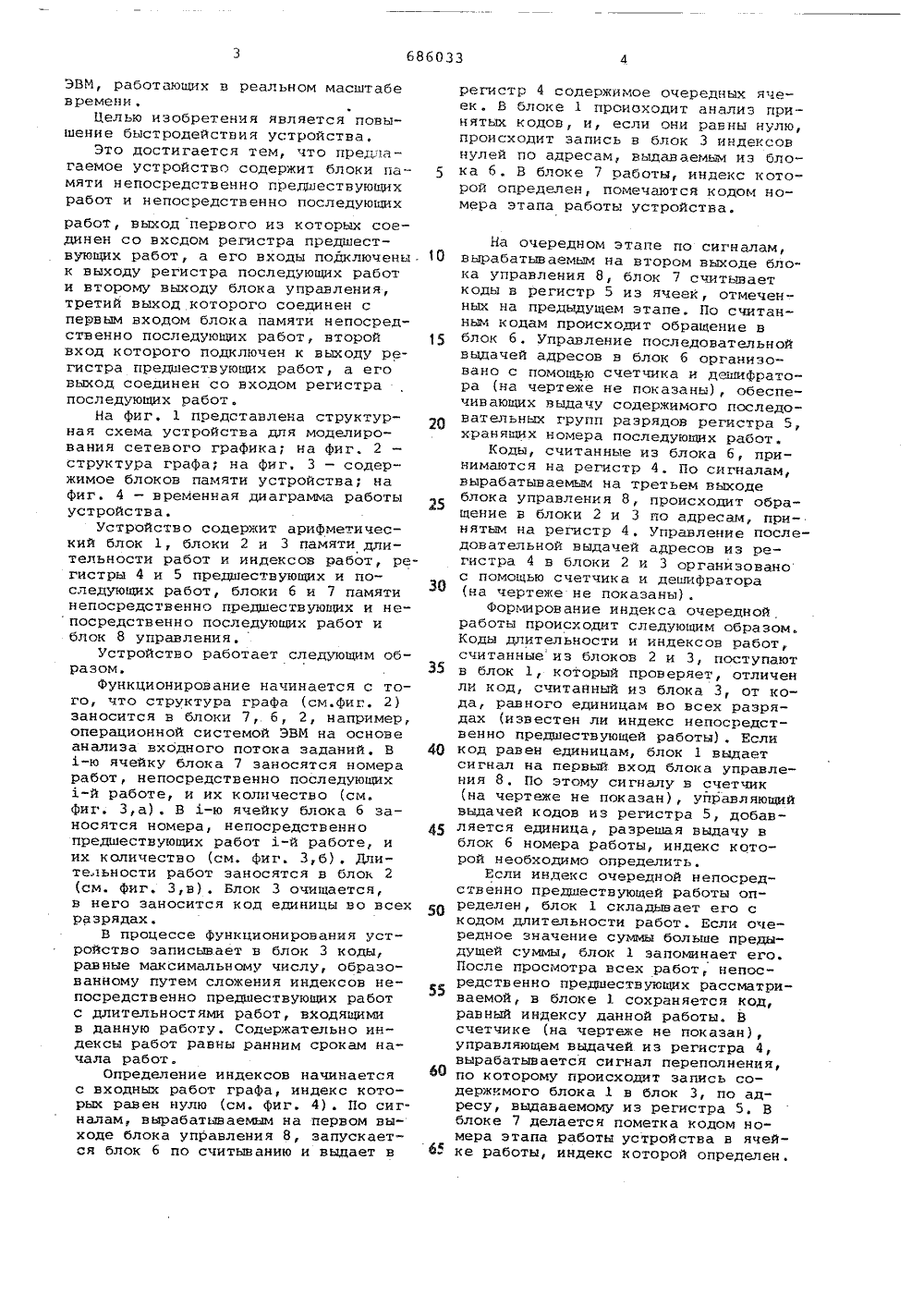

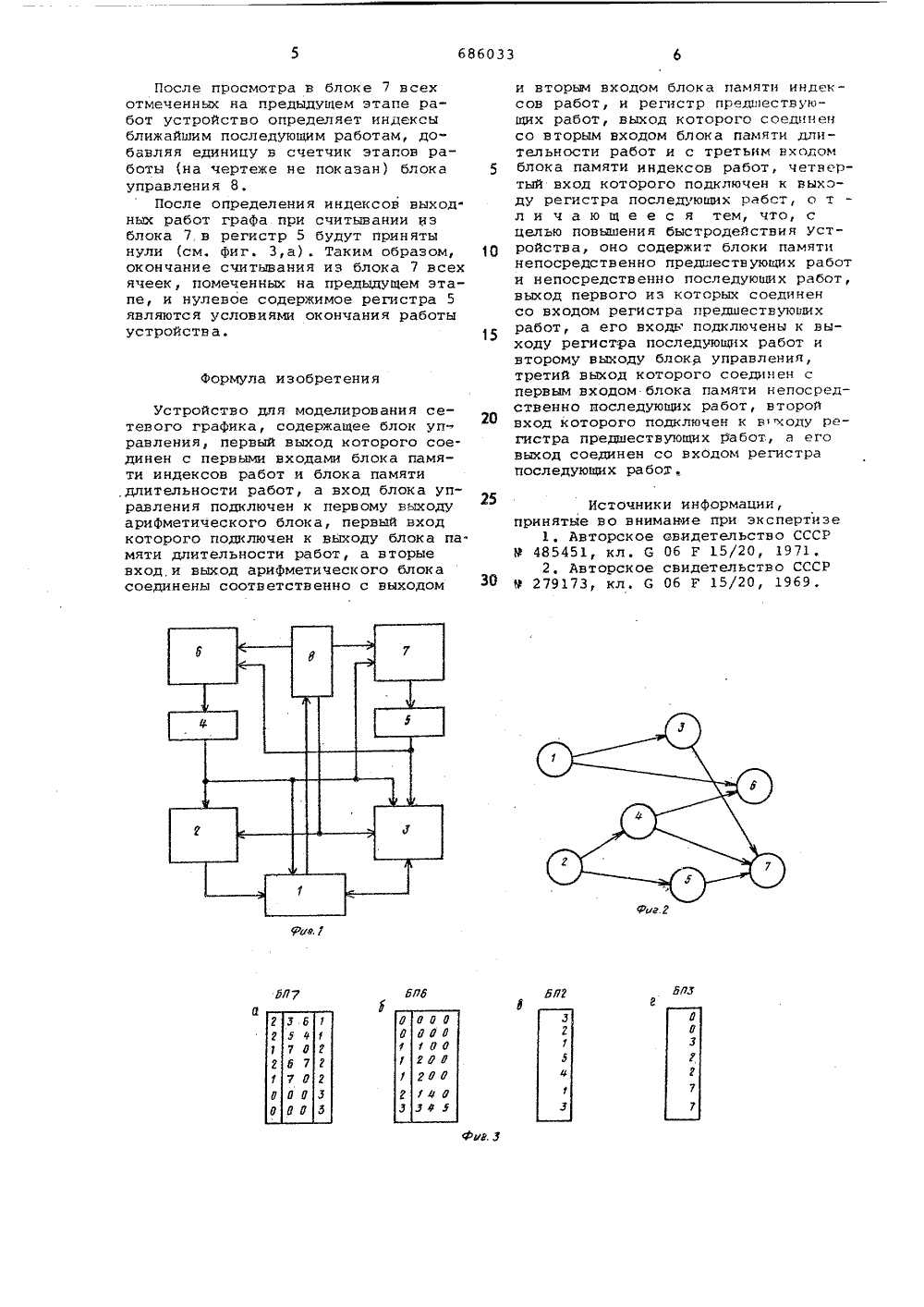

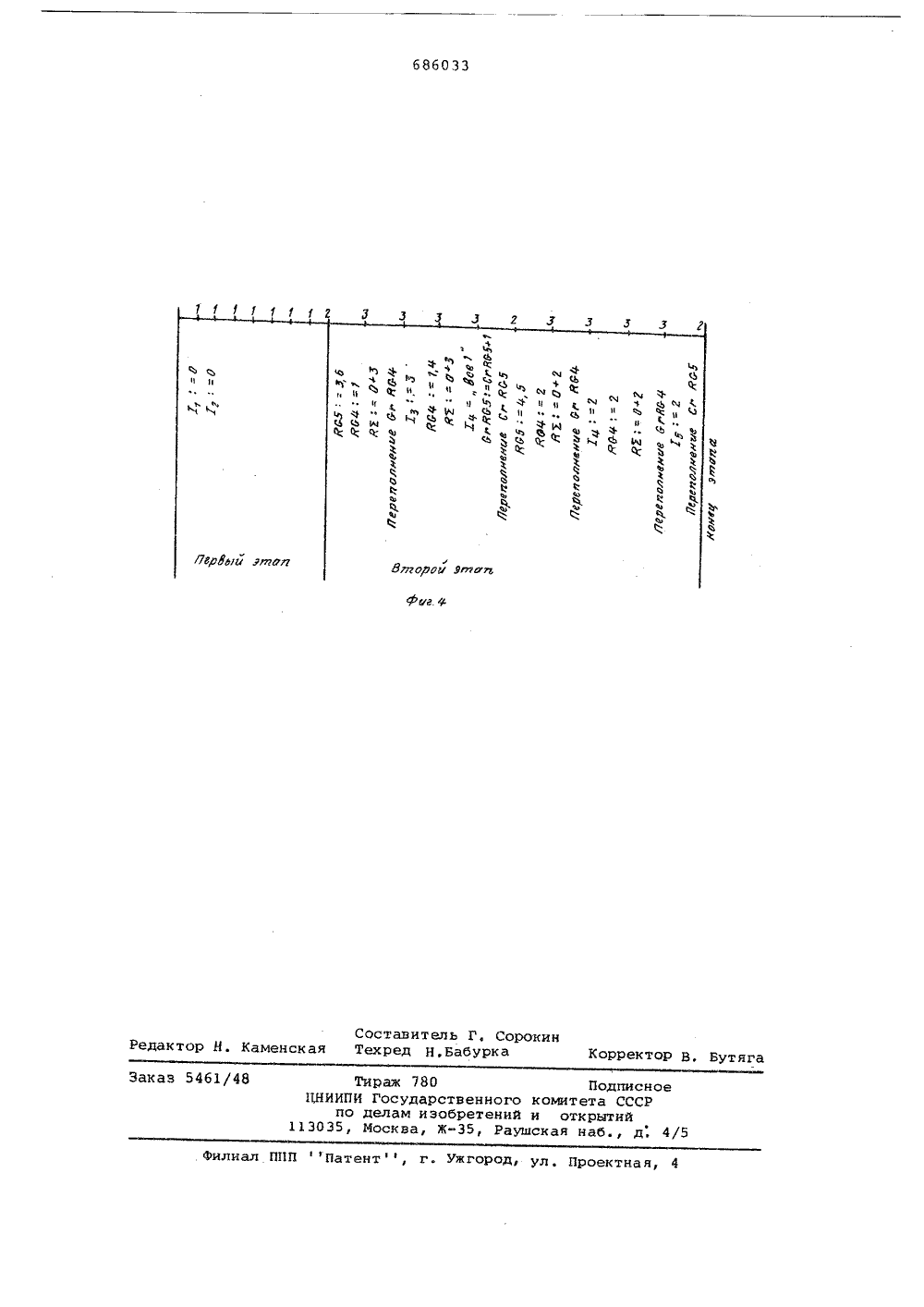

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ТОРСКО ИДЕТЕЛЬСТВУ(61) Доп ельное к авт. сеид-ву -2) 3 леио 1005.77 (21) 2483177/18 присоединением эаеаки М осударстаеииый комитет СССР по делам изобретеии и открытий.А, Поля ВиТЭЛ 54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СЕТЕВОГО ГРА Изобреычислителснользовельньщ пых ЭВМ. 5 ро- со 20 ение относится к областиьной техники и может быть для управления вычислиессом в многопроцессорИзвестно устройство для модели вания кратчайших. путей в графах, держащее блок автоматического фор рования топологии, блок управления, модели ветвей 1. Для повышения надежности и быстродействия устройства выход блока автоматического формирования топологии соединен с блоком управления, Предварительно в формирователи адресов заносятся длительности ветвей, а в счетчики - адреса узлов. Триггеры блокировки моделей и триггеры формирования топологии устанавливаются в единичное состояние, разрешая прохождение измерительных импульсов через разрешенные модели работ и измерительное устройство, Однако подсоединение блока автоматического формирования топологии к формирователю временных интервалов не позволяет автоматизировать процесс ввода данных в формирователи, счетчики, управляющие триггеры устройства. Наиболее близким техническим решением к данному изобретению являет ся устройство для моделирования сетевого графика, содержащее блок управления, первьа выход которого соединен с первыми входаья блока памяти индексов работ и блока памяти длительности работ, а вход блока управления подключен к первому выходу арифметического блока, первый вход которого подключен к выходу блока памяти длительности работ, а вторые вход и выход арифметического блока соединены соответственно с выходом и втооым входом блока памяти индексов работ, и регистр предшествующих работ, выход которого соединен совторым входом блока памяти длительности работ и с третьим входом блока памяти индексов работ, четвертый вход которого подключен к вьмоду регистра последующих работ 21. Однако это устройство имеет низкое быстродействие. Значительное время ввода данных в устройство, обусловленное необходимостью перекоммутации свяэей на наборном поле, не позволяет применять подобные устройства в це" лях расчета сроков начала выполнения программ в многопроцессорныхЭВИ, работающих в реальном масштабевремени,Целью изобретения является повышение быстродействия устройства,Это достигается тем, что предлагаемое устройство содержит блоки памяти непосредственно предшествующихработ и непосредственно последующих работ, выход первого из которых соединен со входом регистра предшествующих работ, а его входы подключены .к выходу регистра последующих работи второму выходу блока управления,третий выход которого соединен спервым входом блока памяти непосредственно последующих работ, второйвход которого подключен к выходу регистра предшествующих работ, а еговыход соединен со входом регистрапоследующих работ.На фиг, 1 представлена структурная схема устройства для моделирования сетевого графика; на фиг. 2структура графа; на фиг. 3 - содержимое блоков памяти устройства; нафиг. 4 - временная диаграмма работыустройства.Устройство содержит арифметический блок 1, блоки 2 и 3 памяти длительности работ и индексов работ, регистры 4 и 5 предшествующих и последующих работ, блоки б и 7 памятинепосредственно предшествующих и непосредственно последующих работ иблок 8 управления,Устройство работает следующим образом.Функционирование начинается с того, что структура графа (см.фиг 2)заносится в блоки 7, б, 2, например,операционной системой ЭВМ на основеанализа входного потока заданий. В1-ю ячейку блока 7 заносятся номераработ, непосредственно последующих-й работе, и их количество (см.фиг, З,а) . В -ю ячейку блока 6 заносятся номера, непосредственнопредшествующих работ -й работе, иих количество (см. фиг. З,б), Длите.1 ьности работ заносятся в блок 2(см. фиг, З,в) . Блок 3 очищается,в него заносится код единицы во всехразрядах.В процессе функционирования устройство записывает в блок 3 коды,равные максимальному числу, образованному путем сложения индексов непосредственно предшествующих работс длительностями работ, входящимив данную работу. Содержательно индексы работ равны ранним срокам начала работ.Определение индексов начинаетсяс входных работ графа, индекс которых равен нулю (см. фиг. 4). По сигналам, вырабатываемым на первом выходе блока управления 8, запускается блок б по считыванию и выдает в 1 О 15 2 О 25 ЗО 35 40 45 5 О 55 60 у регистр 4 содержимое очередных ячеек. В блоке 1 происходит анализ принятых кодов и, если они равны кулю,происходит запись в блок 3 индексовнулей по адресам, выдаваемым иэ блока б. В блоке 7 работы, индекс которой определен, помечаются кодом номера этапа работы устройства. Яа очередк ом этапе по сиги алам, вырабатываемым ка втором выходе блока управления 8, блок 7 считывает коды в регистр 5 из ячеек, отмеченных на предыдущем этапе. По считанным кодам происходит обращение в блок б, Управление последовательной выдачей адресов в блок б организовано с помощью счетчика и дешифратора (на чертеже не показаны), обеспечивающих выдачу содержимого последовательных групп разрядов регистра 5, хранящих номера последующих работ.Коды, считанные из блока б, прикимаются на регистр 4. По сигналам, вырабатываемым ка третьем выходе блока управления 8, происходит обращение в блоки 2 и 3 по адресам, принятым на регистр 4. Управление последовательной выдачей адресов из регистра 4 в блоки 2 и 3 организовано с помощью счетчика и дешифратора (на чертеже не показаны) .Формиров ание индекса очередной, работы происходит следующим образом. Коды длительности и индексов работ, считанные из блоков 2 и 3, поступают в блок 1, который проверяет, отличен ли код, считанный из блока 3, от кода, равного единицам во всех разрядах (известен ли индекс непосредственно предшествующей работы) . Если код равен единицам, блок 1 выдает сигнал на первый вход блока управления 8. По этому сигналу в счетчик (на чертеже не показан), управляющий выдачей кодов из регистра 5, добавляется единица, разрешая выдачу в блок 6 номера работы, индекс которой необходимо определить.Если индекс очередной непосредственно предшествующей работы определен, блок 1 складывает его с кодом длительности работ. Если очередное значение суммы больше предыдущей суммы, блок 1 запоминает его. После просмотра всех работ, непосредственно предшествующих рассматриваемой, в блоке 1 сохраняется код, равный индексу данной работы. В счетчике (на чертеже ке показан), управляющем выдачей иэ регистра 4, вырабатывается сигнал переполнения, по которому происходит запись содержимого блока 1 в блок 3, по адресу, выдаваемому иэ регистра 5. В блоке 7 делается пометка кодом номера этапа работы устройства в ячейке работы, индекс которой определен,686033 г.2 БЮ БПБ БП После просмотра в блоке 7 всех отмеченных на предыдущем этапе работ устройство определяет индексы ближайшим последующим работам, добавляя единицу в счетчик этапов работы (на чертеже не показан) блока управления 8.После определения индексов выход. ных работ граФа при считывании из блока 7.в регистр 5 будут приняты нули (см. фиг. З,а) . Таким образом, окончание считывания из блока 7 всех ячеек, помеченных на предыдущем этапе, и нулевое содержимое регистра 5 являются условиями окончания работы устройства. Формула изобретения Устройство для моделирования сетевого граФика, содержащее блок управления, первый выход которого соединен с первьми входами блока памяти индексов работ и блока памяти ,длительности работ, а вход блока управления подключен к первому выходу арифметического блока, первый вход которого подключен к выходу блока памяти длительности работ, а вторые вход,и выход ариФметического блока соединены соответственно с выходом и вторым входом блока памяти индексов работ, и регистр предшествующих работ, выход которого соединенсо вторым входом блока памяти длительности работ и с третьим входомблока памяти индексов работ, четвертый вход которого подключен к выходу регистра последующих рабст, о тл и ч а ю щ е е с я тем, что, сцелью повышения быстродействия устройства, оно содержит блоки памятинепосредственно предшествующих работи непосредственно последующих работ,выход первого из которых соединенсо входом регистра предшествующихработ, а его входк подключены к выходу регистра последующих работ ивторому выходу блока управления,третий выход которого соединен спервым входом блока памяти непосредственно последующих работ, второйвход которого подключен к в 1 ходу регистра предшествующих работ., а еговыход соединен со входом регистрапоследующих работ,Источники информации,принятые во внимание при экспертизе 1, Авторское овидетельство СССР Р 485451, кл, 6 06 Г 15/20, 1971,2, Авторское свидетельство СССР Ч 279173, кл, С 06 Г 15/20, 1969,686033 Фиг Составитель Г, СорокинТехред Н,Бабурка Коррект актор Н. Каменска Бутяга акав 5461/4 Тираж 780 ПодписноеИ Государственного комитета СССРделам изобретений и открытийМосква, ЖРаушская наб., д, 4/ 1 НИ 3035 Фили ПП Патент, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2483177, 10.05.1977

ВОЕННАЯ ИНЖЕНЕРНАЯ РАДИОТЕХНИЧЕСКАЯ ОРДЕНА ОТЕЧЕСТВЕННОЙ ВОЙНЫ АКАДЕМИЯ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА ГОВОРОВА Л. А

ШУТИЛОВ АЛЕКСАНДР ИУСТИНОВИЧ, ПОЛЯКОВ ГЕННАДИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 15/173

Метки: графика, моделирования, сетевого

Опубликовано: 15.09.1979

Код ссылки

<a href="https://patents.su/4-686033-ustrojjstvo-dlya-modelirovaniya-setevogo-grafika.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования сетевого графика</a>

Предыдущий патент: Устройство для контроля отклонений длительности импульсов от номинальных значений

Следующий патент: Многоканальное цифровое сглаживающее устройство

Случайный патент: Устройство для управления работой электрохолодильника