Логическое программное устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

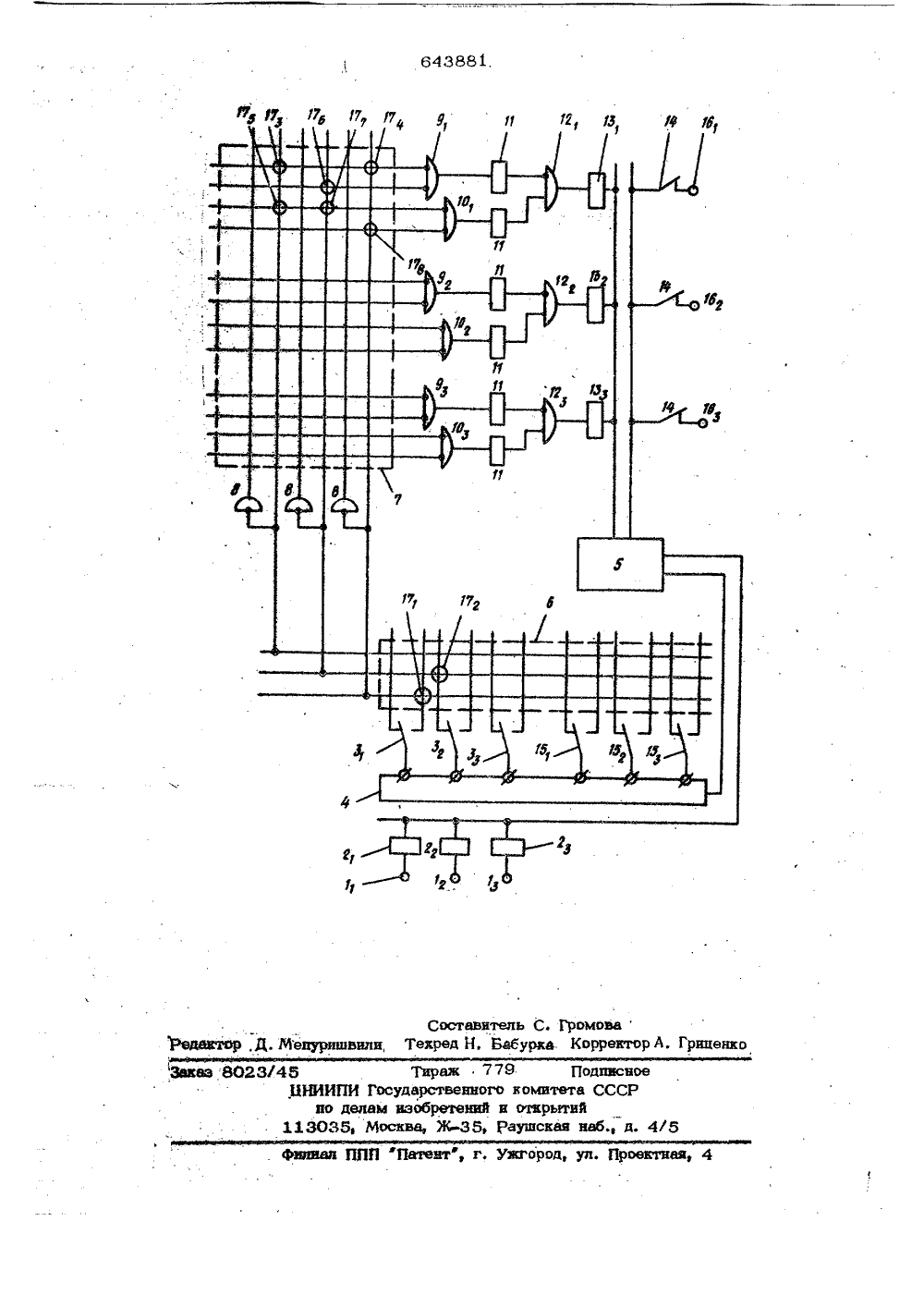

ОПИСАНИЕ ИЗОВРЕТЕЙ ИЯ К АВТОРСКОМУ СВИДФТЮЛЬСВУ Союз СоветееаСоциавктмцеовзРаспублмм 1 . 643881(22) ЗаЯвлено 17.02.76(21) 2325247/18-24с присоединением заявки ударатвенна 1 л квнатет СССР ва делам маабретве и вткрмтлй(23) Приоритет Опубликовано 25.01.79,Бюллетень 3 Дата опубликования описания 28.01.7(54) ЛОГИЧЕСКОЕ ПРОГРАММНОЕ УСТРОЙСТВО Йзобретение относится к автоматике и вычислительной технике и может бытьиспользовано в качестве логического устройства в автоматизированных системах управления.Известно логическое дрограммное устройство, содержащее усилнтелн-формирователи импульсов тока, матрицу ло гических базисов, входные и выходные реле, генератор импульсов считывания 11 .Однако, известное устройство требует болыпих аппаратурных затрат - для считывания информации с базисов, определения фазы сигнала, исключения помех требуется сложная аппаратура. Кроме этого информационная емкость таких устройств (сумма входных и выходных сигналов) ие превышает 100-150 сит- валов, так как с увеличением информационной емкости устройства матрица увеличивается по квадратичной зависн мосей. Наиболее близким техническим репе пнем к,данному изобретению является ло: гическое программное устройство, содержащее матричный дешифратор, выполненныйв виде матрицы на двухотверст ных трансфлюксорах, большие отверстия которых прошиты горизонтальными и вертикальнымн шинами, подключенными к источнику постоянного тока, а малые отверстия прошиты вертикальными шинами, подключенными к источндку напряжения считывания через группу вход ных переключательных элементов и через группу выходных переключательных элементов, и горизонтальными шинами, усилители считываиия, диоды 2 .Однако, на построение этого устрой ства требуются значвгельные аппаратурные затраты.Целью изобретения является сокра щенке аппаратурных затрат.,Эта пель достигается тем, что вред ложенное программное логическое уст ройство содерацфт матричный шифратор 1группу элементов НЕ, две группы элементов, ЗАПРЕТ, группу элзментов задержки и коммутатор, входы которого соединены с соответствующими выходами группы входных цереключательных 5 элементов, а выходы - с соответствующими входами матричного шифратора, ,.выходы которого через группу элементов НЕ подключены ко входам матрич-ного дешифратора, выходы которого сое . 10 динены через первук 1 группу элементов ЗАПРЕТ, группу элементов задержки, вто- рую группу элементов ЗАПРЕТ- со входами группы выходных нереключательных элементов. 15На чертеже приведена структурная блок-схема устройства (для примера на. три входа и на трн выхода).Устройство содержит; входные клеммы- 1 ф группу входных переключатель нйх элементов,. в которую входят обмотки входных реле 2 - 2 , перекидные контакты входных реле 3- 3 , комму 3 татор 4, источник питания 5, матричный шифратор 6, матричный дешифратор 7, группу элементов НЕ 8, две группы элементов ЗАПРЕТ 94- 93 ф 101 103 ф ,(введенных дополнйтельно),группу элементов задержки 11, элементы ЗАПРЕТ 12 - 12, группу выходных переключа 30тельных элементов, в которую входят обмотки выходных реле 13 - 13, замы кающие контакты Выходных реле 14, перекидные контакты выходных реле 15- 15, выходные клеммы 16 - 16,(вы 35 ходйые сигналы "х)элементы 17 - 178 матриц, в которых записано состояниеУ 1 ФВходные клеммы 1,- 15 соединены с обмотками входных реле 2 - 2 (повто 401ряющими входные переменные а - а ), другой вывод обмоток -оединен с источником йитания Б, Подвижные контакты .перекидных контактных групп .3 - 3и45 15 - 15 входных и выходных реле сое 3динены с контактами коммутатора 4, а неподвижныо - сс входами матричного шифратора 6. Выходы матричного шифратора 6 соединены с прямыми веЬтикаль 50 ными шинами матричного дешифратора 7 и со входами элементов НЕ 8, выходы которых соединены с инверсными вертикальными шинами дешнфратора. Горизонтальные г,ины матричного дешиф 55 ратора соединены со входами элементов ЗАПРЕТ, при этом одна пара шин соединена с элементами ЗАПРЕТ 9- 9 а другая - с элементами ЗАПРЕТ 1 С 10 . Выходы элементов ЗАПРЕТ соединены через элементы задержки 11 со входами элементов ЗАПРЕТ 12, выходы которых соединены с обмотками выходных реле 13 - 13 . Замыкающие кои 3такты 14 выходных реле соединены с источяиком питания 5 и с выходными клеммами устройства 16 - 16ЭУстройство функционирует следующим образом.,1" В соответствии с заданным алгорит- мом функционирования производится запись слов в Матричный шифратор 6 и матричный дешифратор 7. Запускается коммутатор 4, Начинается последова- тельное считывание слов, записанных на вертикальных шинах шифратора 6.При этом, если входное (выходное) реле обесточено, то есть если отсутствует входная переменная фа" (или выходная переменная х), то считывание производится только с шин, соединенных с нормал ьно-замкнутыми контактами реле, если Входное (в 11 ходное) реле сработало, то есть если подается вход-" ной "а" (выходной "х"), сигнал то счи- : тывание производится только с шин, соединенных с нормально-разомкнутымн контактамн реле.Таким образом, последовательный набор слов, считываемый с шифратора, является функцией входных ("а") и выходных ("х) переменных. Слова последовательно засыпаются в матричный дешифратор 7, выходы которого построены на двух горизонтальных шйнах, элементе ЗАПРЕТ и элементе задержки. При совпадении входного слова с записанным на соответствующем выходе дешифратора образуется сигнал, который удлиняется с помощью элемента задержки 11 на время, большее времени одного. цикла работы коммутатора. Если при последующих циклах данное слово продолжает засылаться в дешифратор, то на выходе последнего будет присутствовать постоянный сигнал.Таким образом достигается програм мная связь между входами шифратора, представленного входными и выходными переменными и выходами дешифратора, представленного выходными переменными. На входе и выходе устройства установлены логические элементы, данное устройство реализует булевы функции в логическом базисе ЗАПРЕТ -ИЛИ-НЕ Например, для реализации произвольной функции х 1 а 1 2(х 1 1611 15 64 Зй а - 1 ) необходимо в элементы 17,Л17 матриц шифратора и дешнфратора записать 1". При этом схема работает следующим образом. С помощьго элемента 17 образуется слово 001 (1), с по мощью элемента 17 - слово 010 (2).2Первая выходная пара дешифратора 9, настроена нв слово 010, вторая 10- на слово 001. При нвлкчии сигналов и4 ;"а," и "а срабатывают реле 2 и 21 3 7 поэтому считывается только одно слово. Это слово регистрируетсяф нв втором выходе 1; подакицем сигнал на прямой вход элемента 1213 АПРЕТ срабатывает выходное реле 13, замй- ф .каются контакты 14 выходного реле, выдается "сигнал "х , Если сигнал а отсутствует, отсутствует н сигнал на прямом входе элемента ЗАПРЕТ; если ,отсутствует сигнал ато при считы- Э2 1ванин информации с шифратора в дешифратор засылается слово 010, которое ".создает сигнал на запретном входе элемента 12, ф в обоих случаях сигнал ".х",отсутствует.1Остальныебулевы функции реализуются аналогичным образом, Обратнаясвязь (выходные сигналы на входе) введена в устройство для получения функции 36 ПАМЯТЬ С ЗАПРЕТОМ, применения принципа суперпозиции функций и тому подобное.Данное устроВ:тво требует матрицуразмер которой.в несколько раз мень 81 6ше матрицы прототипа, поэтому информационная емкость устройства увеличивает-.ся до нескольких сотен сигналов. формула изобретения Логическое программное устройство, содержащее матричный дешифратор, группу входных переключательных элементов и группу выходных переключатель ных элементов, о т л и ч а ю щ е е с я тем, что, с целью сокращения вп аратурных затрат, оно содержит матричный шифратор, группу элементов НЕ, две группы элементов ЗАПРЕТ, группу элементов задержки и коммутатор, входы которого соединены с соответствующими выходами группы модных переключательных элементов, а выходы - с соответстВующйми входами матричного шифратора, выходы которого через группу элементов НЕ подключены ко входам матричного дешифратора, выходы которого соединены через первую группу элементов ЗАПРЕТ группу элементов; .-задержки, вторую группу элементов ЗАПРЕТ - со входами группы выходных переключательных эле ментов.Иатпчникь информации, принятые во внимание при экспертизе:1. Авторское свндегельство СССР Ю 808018, кл. (3 06 Р 18/20, 1974.2. Авторское свидетельство СССР Ь 822822, кл. 6 11 С 11/08, 1974..БНИИПИ Гос но делам 113035 Москва, Филиал ППЙ Патент, г. Ужгород, ул. М 6 ктФф, Д, Яенуришвилн, Техред Н, уркЗакю 8023/46 Тираж 779 Подпнсударственного комитета СССизобретений н открытийЖ 335, аувскаи наб.,А. Грин

СмотретьЗаявка

2325247, 17.02.1976

ПРЕДПРИЯТИЕ ПЯ В-2572

КАРАШТИН ВЛАДИМИР МИХАЙЛОВИЧ, НОВИКОВ ИГОРЬ АНДРЕЕВИЧ, ШАЦИЛЛО СТАНИСЛАВ АНТОНОВИЧ

МПК / Метки

МПК: G06F 17/10, G06F 9/00

Метки: логическое, программное

Опубликовано: 25.01.1979

Код ссылки

<a href="https://patents.su/4-643881-logicheskoe-programmnoe-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Логическое программное устройство</a>

Предыдущий патент: Устройство для исследования графов

Следующий патент: Устройство для измерения характеристик фотографических систем

Случайный патент: Устройство для циркуляционного вакуумирования металла