Микропроцессорное вычислительное устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 643879

Авторы: Бондарович, Корниенко, Корчак, Окунев

Текст

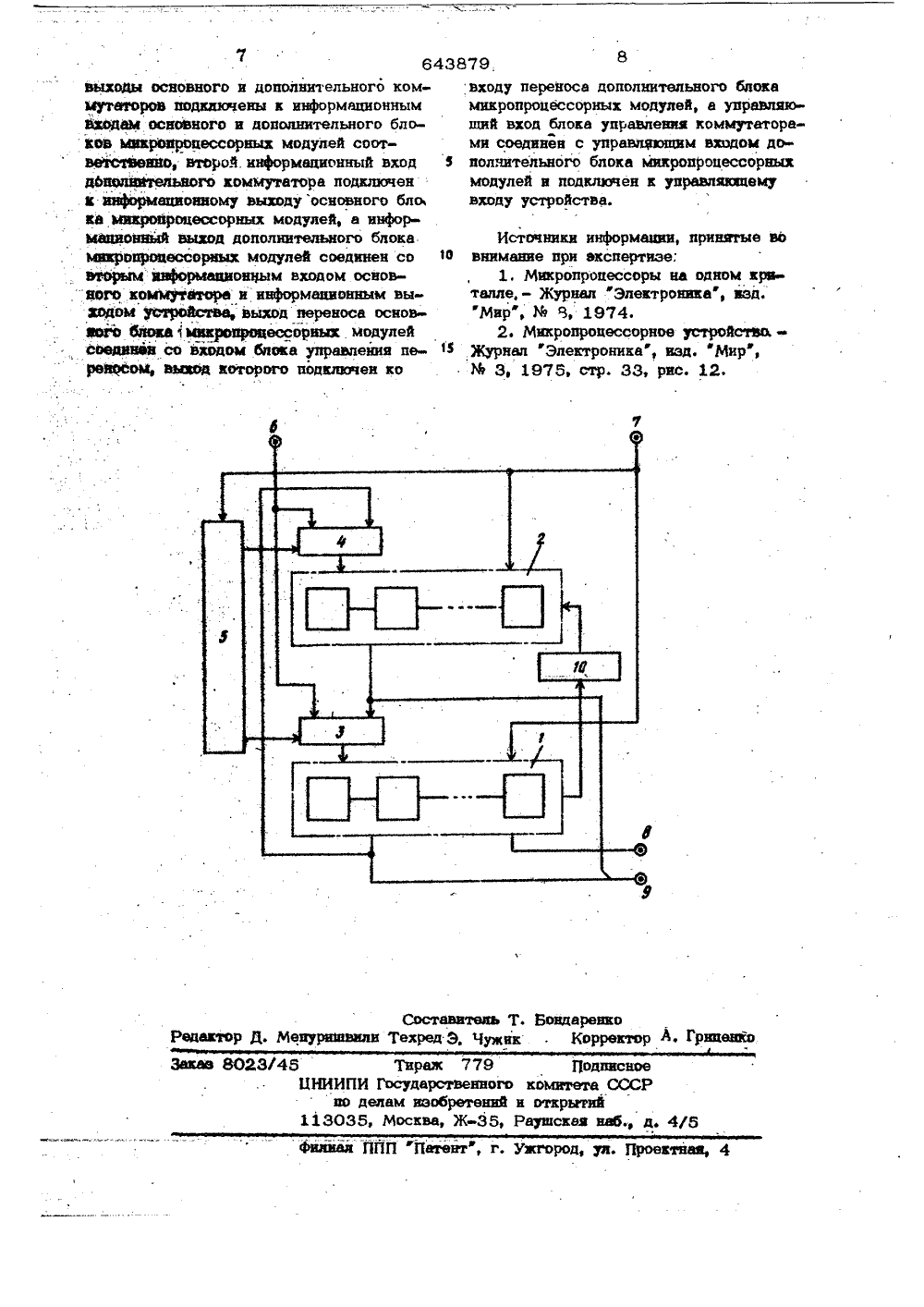

Своз СоеатеваСвралистнекааРеспублик и 643879 ОП ИСАНИ ЕИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДВТВЛЬСТВУ(6) Дополнительное к авт, сеид-в 21) 2435571/18-2 1) М. Кл. 22) Заявлено 27,12 15/16 рнсоеднненнем заявки Я Гесудеуствае емет СССР ю дэяан азбуэй а окрютай(73) Заявитель БАньТЕЕЛ 54) МИКРОПРОЦЕССОРНОЕ ВЫЧИСЛИТЕЛЬНОЕ уст РОистВОамя тигаетси тем, дополнительх модулей коммутаторы, и блок управый й второй ю является ельное устав Основной блок , управляюн к управ нонной и дополнительны ок управления переносом ния коммутаторами, пер Предлагаемое изобретение относигся и области вычислительной техники и мо-жет быть нспольэовано в многопроцес сорных вычислительных комплексах для обработки цифровой информации.Известны микропроцессорные устройства 1, содержашие арифметнко логический блок, устройство управления,встроенную сверхоперативную память, рабочие и вспомогательные регистры, ко торые объединены между собой внутренними шинами;Недостатком известных микроцроиеосорных устройств являетси малый обьем встроенной сверхоперативной памяти, а также невозможность увеличения разра- ности, что ограничивает область применения устройств.есквм решееНаиболее близким технич иием к данному иэобретени микропроцессорное вычислит ройство 2, содержащее микропроцессорных модулей шнй вход которого подключе ликацему входу устройства, информаци ящый выход основного блока микропро цессорных модулей подключен к инфор мационному выходу устройства, адресный выход основного блока микропроцессорф ных модулей соединен с адресным выходом устройства.Недостатком известного микропроцессорного вычислительного устройстваявлнетсй малый обьем встроенной свара оперегивной и ти, а также увелйчение времени выполнения операций при разрядности входных данных болыцей, чем разрядность микроцропессорного вычиолнтельного устройства, что снижает.быст1 ф родействие устройства.Целью настоящего изобретения является повышение быстродействии.Поставленная цель досчто в устройство введеныный блок мнкропроцессорнывыходы которого подключены к управляющим входам основного и дополнительно- го коммутаторов соответственно, первые информационные входы которых подключены к информационному входу уст ройства, а выходы основного н дополнительного коммутаторов подключены к ин,формационным входам основного и дополнительного блоков микропроцессорных модулей соответственно,"второй ннформаци онный вход доголнительного коммутаторе подключен к информационному выходу основного блока микропроцессорных модулей, а информационный выход дополни-. тельного блока микропроцессорных моду лей соединен, со вторым информационным входом ОсиоьнотО коммутатора и информационным выходом устройства, выход переноса основного блока микропро цессорных модулей соединен со входом О блока управлении переносомвыход которого подключен ко входу переноса доцолнительиого бежа микропроцессорных модулей, а управляющий вход блока,управления коммутаторами .соединен с управлаапим входом дополнительного блока микропроцессорных модулей и подключен к уцравлаощему входу устройства.На чертеже представлена функциональиаи схема микропроцессорного вычислительного устройства.Микропроцессорное вычислительное устройство содержит; основной блок 1 Микропроцессорных модулей, донолнительный блок 2 микропроцессорных модулей, Основной коммутатор 3, дополнительный коммутатор 4, блок 5 управления коммутаторами, информационный вход 6 устройства; уЩювиязОкий Вхбд 7 у адресный. ВМход 8 у информационный выход 9 ф блОк 4 ф 10 управления переносом.Управлявшие входы блока 5 управления коммутаторами подключены к управляющему входу 7 устройства, а вы ходы блока 5 управления коммутаторами 45 подключены к управляющим входам основного коммутатора 3 и дополнительного коммутатора 4, первые информационные входы которых подключены к информационному входу 6 устройства, а выходы 50 соответственно подключены к информационным входам основного блока 1 микропроцессорных модулей и дополнительного блока 2 микропроцессорных модулей, уп 15 равпиюаие входы которых подключены к управляющемувходу 7 устройства. Информационный выход основного блока 1 микропроцессорных модулей и дополжтельного блока 2 соединены с. информационным выходом 9 устройства. Кроме того, ннформацйонный выход основного блока 1 микропроцессорных модулей подключен ко второму информационному вхо ду дополнительного коммутатора 4, а информационный выход дополнительного блока 2 микропроцессорных модулей подключен ко второму информационному входу основного коммутатора 3. Выход аД- реса основного блока 1 микропроцессорных модулей соединен с адресным выходом 8, а выход переноса подключен ко входу блока 10 управления переносом, выход которого подключен ко входу переноса дополнительного блока 2 микропро пессорных модулей.Работу микропроцессорного вычислительного устройства рассмотрим, например, при выполнении, короткой операции типа сложение, При выполнении операции в формате регистр-регистр" (согласно системе команд ЕС ЭВМ) допустим, что первый операнд (адрес Й 1 ) находится в основном блоке 1, а второй операнд (адрес й 2) - и дополнительном блоке 2. В этом случае выполнение операции происходит в том блоке микропроцессорных модулей, где находится первый операнд ( 3 Ц ). Поэтому второй операнд ( Я 2 ) необходимо переслать в основной блок 1 микропроцессорных модулей.На управляющий вход 7 устройства посгупает последовательность микрокоманд, Первая микрокоманде подается на дополнительный блок 2 микропроцессорных модулей и на управлпощие входы блока 5 управления коммутаторами. На управляюший вход основного блока 1 мик ропроцессорных модулей со входа 7 устройства подается холостая команда. При этом происходит передача второго операнда ( Йй )на выход дополнительного блока 2 мйкропроцессорных модулей и далее - иа второй информационный вход оснЬвного коммутатора 3. На выходе бло ка 5 управления коммутаторами появля ется управлвоший сигнал, который раэре шает прохождение второго операнда ( Я 2) через основной коммутатор 3 на информациоийый вход основного блока 1 микропроцессорных модулей. При подаче. следукяией микрокоманды происходит выпол- нение операции и резулвгат операции остается в основном блоке 1 микропроцес. сорных модулей (согласно системе кЬ манд ЕС ЭВМ).ного слова на информационный вход основного блока 1 микропроцессорных модулей через основной коммутатор 3, а старшей части 2 И -разрядного сномна информационный вход дополнительного блока 2 микропроцессорных модулей через дополнительный коммутатор 4. При подаче следующей микрокоманды происходит выполнение операции. По окончании операции, если появляется перенос из младшей части 2 ррзряднго ова в старшую аь, то он поступает с выхода переноса основного блока 1 микропроцессорных модулей через блок 10 управления переносом на вход переноса дополнительного блока 2 микропроцессорных модулей, где по очередной микрокоманде, формируется окончательный результат операции.Увеличение встроенной сверхоператив ной памяти путем введения дополнительного блока микропроцессорных модулей основного и дополнительного коммутато ров,блоков управления переносом и коммутаторами позволило расширить функци опальные возможности микропроцессорного вычислительного устройства, л также увеличить быстродействие более, чвм в 1,5 раза путем уменьшения времени обработки 2 И - разрядной информации. Формула изобретения Микропроцессорное вычислитвльнов устройство, содержащее основной блок микропроцессорных модулей, управляющий вход которого подключен к управляющему входу устройства, информационный выход основного блока микропроцес-, сорных модулей подключен к информационному выходу устройства, адресный выход, основного блока микропроцессорных мо дулей соединен с адресным выходом устройства, о т л и ч а ю щ е е с а тем, что, с целью повышения быстродействия, в него введены дополнительный блок микропроцессорных модулей, основной и дополнительный коммутаторы, блок управления переносом и блок управления коммутаторами, первый и второй выходы которого подключены к управляющим входам основного и дополнительного коммутаторов соответственно, первые информационные входы которых подключены к информационному входу устройства, а с 643879Если первый операнд ( Я 1) находится в дополнительном блоке 2 микропроцессорных Модулей, а второй операнд ( Я 2 ) - в основном блоке 1, то .абота, устройства происходит аналогичным об-разом, только операция выполняется в дополнительном блоке 2 микропроцессорных модулей.При выполнении операции в формате "регистр-память (согласно системе ко манд ЕС ЭБМ из внешней памяти на информационный вход устройства подается И -разрядное слово (Х) на первые информационные входы основного коммутатора 3 и дополнительного коммутатора 4. Лопустим, что первый операнд ( Й 1 ) находится в дополнительном бло ке 2 микропроцессорных модулей. На вход 7 устройства подается последова- тельность микрокоманд. Первая микроко ф манда поступает на управляющие входы блока 5 управления коммутаторамч и обеспечивает появление на его выходе управляющего сигнала, который разрешает прохождение И -разрядного слова (Х) на информационный вход дополнительного блока 2 микропроцессорных модулей через дополнительный коммутатор 4. При подаче следующей микрокоманды происходит выполнение операции. ЗйЕсли первый операнд ( В 1 ) находится в основном блоке 1 микропроцессорных модулей, то работа устройства происходят аналогичным образом, только5 операция выполняется и основном блоке 2 микропроцессорных модулей.При работе с 2 И -разрядными словами в основном блоке 1 микропроцессорных модулей находитса младшая часть 2 И - разрядного слова, а в дополнитель-О ном блоке 2 микропроцессорных модулейстаршая часть 2 И -разрядного слова. Иэ внешней памяти 2 О - разрядной магистрали на вход устройства 6 подается 2 И -разрядное слово на первые информационные входы основного комщтатора 3 и дополнительного коммутатора 4. На управляющий вход 7 поступает последовательность микрокомеи, которая подаетса на управляющие входы блока 5 управлению коммутаторами и на управляющие входы основного блока 1 и дополнительного блока 2 микропроцессорных модулей. Первая микрокоманда обеспечивает цоявление на выходе блока55 5 управления коммутаторами управляющего сигнала, который разрешает прохождение младшей части 2 И -разрад/48 Тираж 779 Подпис БНИИПИ Государственного комитета по делам иэобретенвй и открытий 113035, Москва, Ж, Рауювскаи вабСССР 4/5 филиал "ППП Патейт, г. Ужгород, уа. Прое 6 выходы основного и дополнительного комЮтеторов подключены к информационным ЙвдЬМ ОсноВного и дополнительного блоков микрароцессорных модулей соотВетст 99 Вноу второй. Информационный вход дбаелнвтельного коммутатора подключен В информааонному выходуосновного бло ка микройроцессорных модулей, а внфорМационнйй выход дополнительного блока микропроцессорных модулей соединен со юэрым йвформацноиымкого коммутатора и информационным вызодом устройства, выход переноса основ- веГЬ блокамикропроцессорных модулей сеедиаа са ващем блока управлении пеРеВФом 3 ВаМ которого подключен ко 43879,8входу переноса дополнительного блока микропроцессорных модулей, а управлиющий вход блока управлении коммутаторами соединен с упраюцоощим входом до волнительного блока микроцроцессорныхмодулей и подключен и управлаацему входу устройства. Источники информации, привитые ио 10 внимание при экспертиэе:1. Микропроцессоры на одном криталле, - Журнал Электроника, юд.Мир, Ж Ч, 1974.2. Микропроцессорное устройства 15 журнал фЭлектроника, изд. Мир

СмотретьЗаявка

2435571, 27.12.1976

ПРЕДПРИЯТИЕ ПЯ А-7160

БОНДАРОВИЧ АНАТОЛИЙ ВСЕВОЛОДОВИЧ, КОРНИЕНКО ИВАН ИОСИФОВИЧ, КОРЧАК ЭДУАРД НИКОЛАЕВИЧ, ОКУНЕВ ВЛАДИМИР ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: вычислительное, микропроцессорное

Опубликовано: 25.01.1979

Код ссылки

<a href="https://patents.su/4-643879-mikroprocessornoe-vychislitelnoe-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессорное вычислительное устройство</a>

Предыдущий патент: Устройство для связи запоминающего и арифметического устройств

Следующий патент: Устройство для исследования графов

Случайный патент: Многорядная хлопкоуборочная машина