Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 640294

Автор: Скляров

Текст

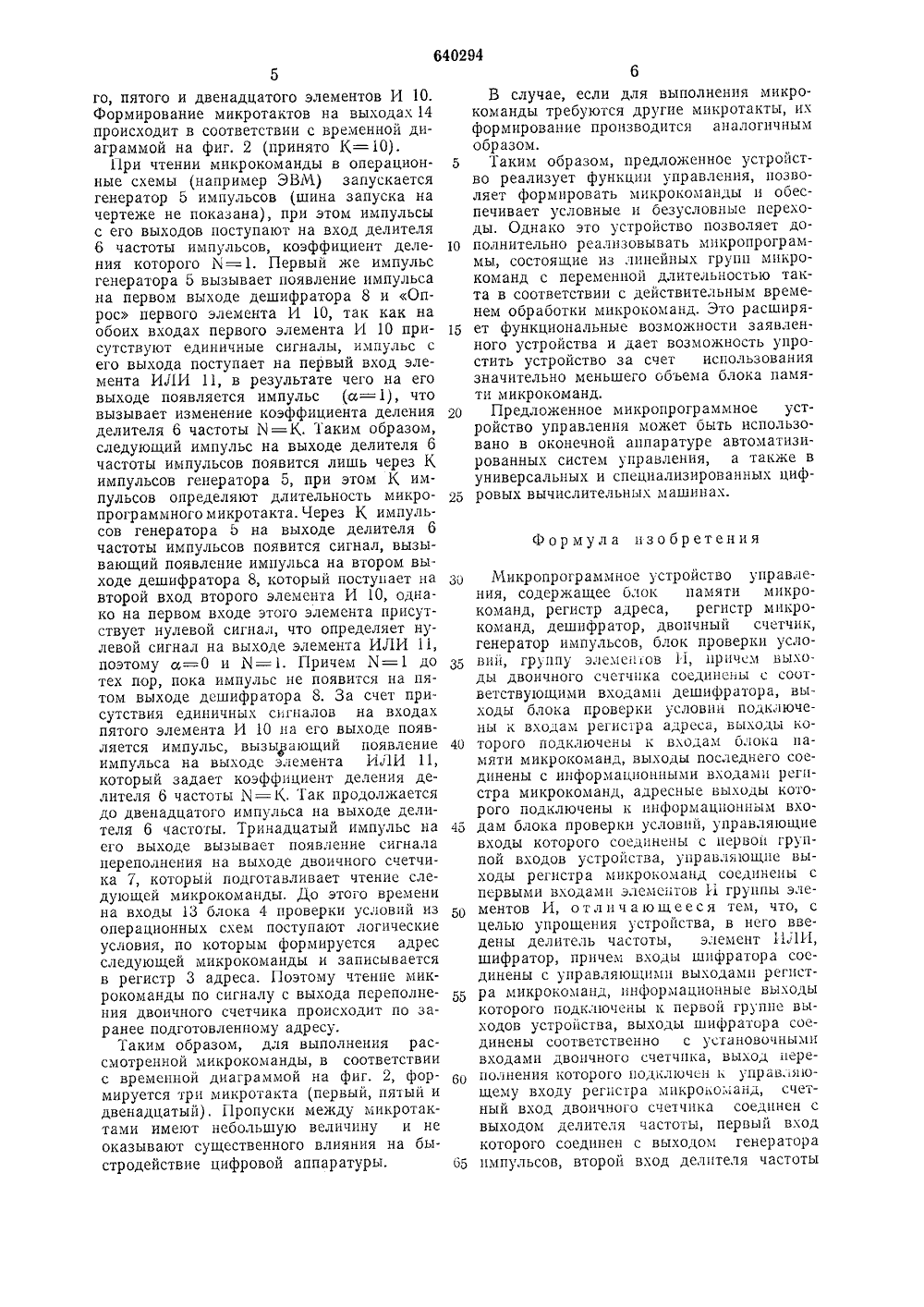

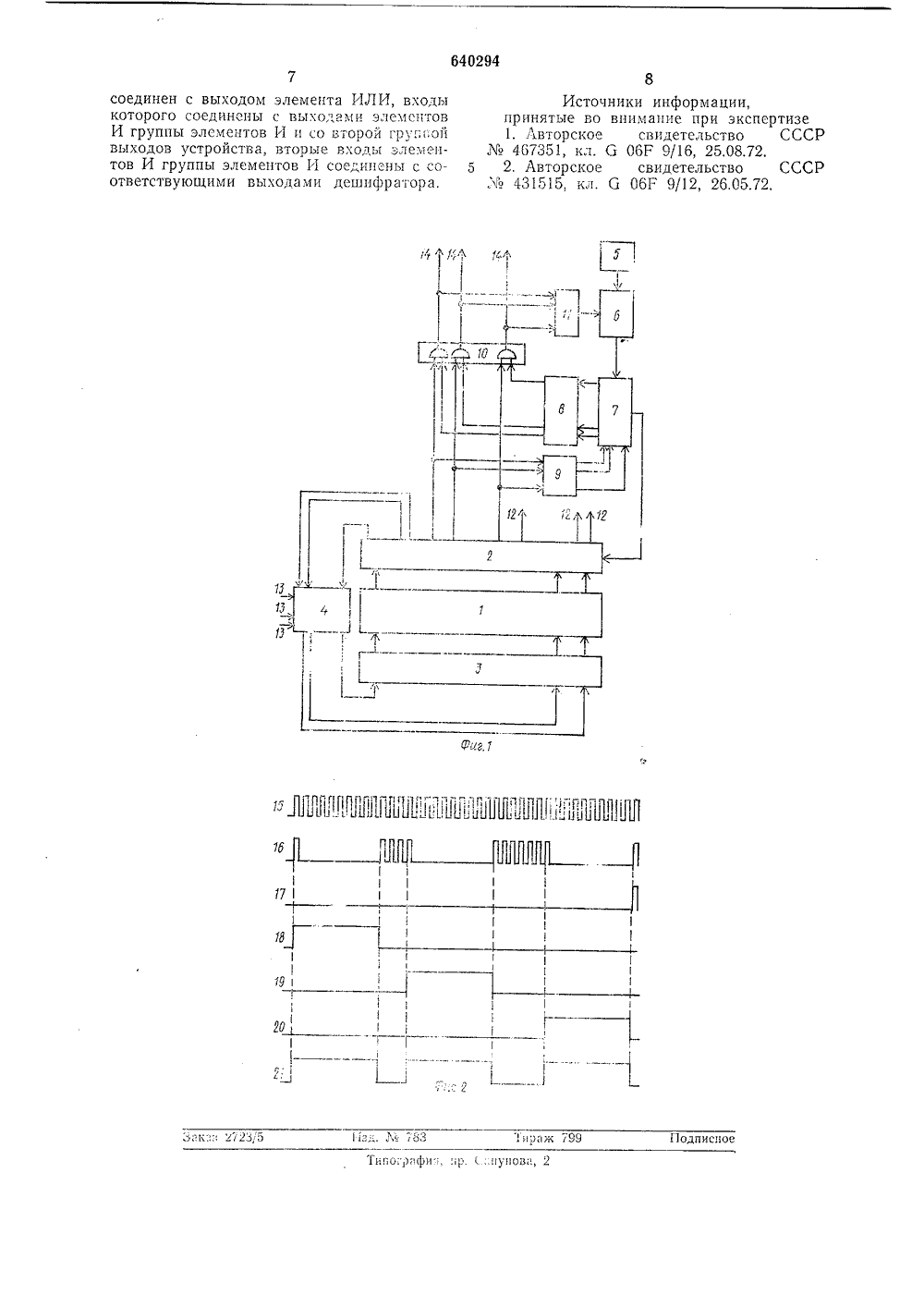

оДля ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союе СоветскиСодиалистн .е;. о; Республик) Дополнитель к авт, свид-ву 2) Заявлено 05,08.76 (21) 2393456/18-2 1) М Кл.С 06 Г 9/16 присоединением заявки Государственный комите СССР(088,8) делам изобретений открыт 45) Дата опубликования описан 2.7) Заявител КРО П РО ГРАМЧ НО Е УСТРОЙ СТВО УП РА Вл Е Н 54 Изобретение относится к ооласти автоматики и вычислительной техники и может быть использовано в оконечной аппаратуре автоматизированных систем управления, а также в универсальных и специализированных цифровых вычислительных машинахх,Известно микропрограммное устройство управления 11, содержащее блок памяти микропрограмм, выходы и входы которого подключены соответственно к входам регистра микрокоманд и к выходам регистра адреса, соединенного с выходом блока управления длительностью микропрограммного такта и через элемент НЕ со входоз секционной линии задержки, выходы которой подключены к одним входам блока управления длительностью микропрограммного такта, другие входы которого соединены с выходами дешифратора поля, входы которого подключены к выходам регистра микрокоманд.Известное устройство позволяет изменять длительность микропрограммного такта путем увеличения ее на линии задержки. Однако в этом устройстве не формируются сигналы, управляющие выполнением микрокоманды в операционных схемах, а длительность микропрограммного такта определяется приближенно по значению кода,записанного в блоке памяти микропрограмм. Кроме того, это устройство требует специально изготовленных секционных линий задержки, время распространения сиг налов, через которые определяется вычисленными интервалами времени, необходимыми для выполнения микрокоманды в операционных схемах. Это ограничивает область применения и функциональные воз можности известного устройства,Наиболее близким техническим решением к изобретению является микропрограммное устройство управления 2, содержащее блок памяти микрокоманд, регистр 15 адреса, регистр микрокоманд, дешифратор,двоичный счетчик, генератор импульсов, блок проверки условий, группу элементов И, причем выходы двоичного счетчика соединены с соответствующими входами дешнфратора, выходы блока проверки условий подключены к входам регистра адреса, выходы которого подключены к входам блока памяти микрокоманд, выходы которого соединены с информационными входа мн Регистра мпкрокоманд, адресные Выходы которого подключены к информационным входам блока проверки условий, управляющие входы которого соединены с первой группой входов устройства, управля ющие выходы регистра микрокоманд сое1, при я=.О; К, при а=1 20 3динены с первыми входами элементов Игруппы элементов.Недостатком известного устройства является его сложный и большой объем оборудования, за счет того, что оно, во-первых,не позволяет формировать длительностьмикропрограммного такта в соответствиис действительным временем выполнениямикрокоманды в операционных схемах и неимеет возможности реализовывать микропрограммы, состоящие из линейных группмикрокоманд с переменной длительностьютакта,Цель изобретения - упрощение устройства.Поставленная цель достигается тем, чтов предлагаемое устройство введены делитель частоты, элемент ИЛИ, шифратор,причем входы шифратора соединены с управляющими выходами регистра микрокоманд, информационные выходы которогоподключены к первой группе выходов устройства, выходы шифратора соединены соответственно с установленными входамисчетчика, выход переполнения которогоподключен к управляющему входу регистрамикрокоманд, счетный вход счетчика соединен с выходом делителя частоты, первыйвход которого соединен с выходом генератора импульсов, второй вход делителя частоты соединен с выходом элемента ИЛИ,входы которого соединены с выходами элементов И группы элементов И и со второйгруппой выходов устройства, вторые входыэлементов И группы элементов И соединены с соответствующими выходами дешифратор а,На фиг. 1 изображено предлагаемоемикропрограммное устройство управления;на фиг. 2 - временная диаграмма его работы.Устройство содержит блок 1 памятимикрокоманд, регистр 2 микрокоманд, регистр 3 адреса, блок 4 проверки условий,генератор 5 импульсов, делитель 6 частоты,двоичный счетчик 7, дешифратор 8, шифратор 9, элементы И 10, элемент ИЛИ 11,первая группа выходов устройства 12, первая группа 13 входов устройства, втораягруппа 14 выходов устройства.Выходы блока 1 памяти микрокомандподключены к входам регистра 2 микрокоманд, а входы - к выходам регистра 3адреса, входы которого соединены с выходами блока 4 проверки условий. Входыблока 4 проверки условий подключены кадресным выходам регистра микрокоманд,на которые подается адресная часть микрокоманды регистра. Управляющие выходырегистра 2 микрокоманд несут информацию о номерах микротактов, которые необходимы для обработки микрокоманды воперационных схемах. Эти выходы подключены к первым входам элементов И 10 ико входам шифратора 9, выходы которого 25 30 35 40 45 50 55 60 05 подключены ко входам двоичного счетчика 7. Выходы разрядов двоичного счетчика 7 подключены ко входам дешифратора 8, выходы которого подключены ко вторым входам элементов И 10. Выходы элементов И 10 подключены ко входам элемента ИЛИ 11, выход которого соединен со вторым входом делителя 6 частоты, первый вход которого подключен к выходу генератора 5 импульсов, а выход - к счетному входу двоичного счетчика 7, выход переполнения которого подключен к управляющему входу регистра 2 микрокоманд.Делитель 6 частоты предназначен для управления подачей тактовых сигналов на вход двоичного счетчика 7. Он имеет два коэффициента деления - М, первый Я=1, второй г 1 = К (К = 10 - 100) . Причем на выходе элемента где а - сигналИЛИ 11.Счетчик 7 и дешифратор 8 представляют собой распределитель импульсов и предназначены для последовательного опроса элементов И 10. Шифратор 9 предназначен для изменения коэффициента пересчета двоичного счетчика 7. Он представляет собой преобразователь номера последнего такта, необходимого для обработки микро- команды, в двоичный код.Принцип действия остальных элементов и узлов либо такой же, как и в прототипе, либо соответствует их функциональному назначению,На фиг. 2 цифры обозначают следующие сигналы: 15 - импульсы на выходе генератора 5 импульсов, 16 - импульсы на выходе делителя 6 частоты, 17 - импульс на выходе переполнения двоичного счетчика, 18 - 20 - соответственно импульсы на выходе первого, пятого и двенадцатого элементов И, 21 - импульсы на выходе элемента ИЛИ 11.Принцип работы устройства заключается в следующем,Пусть из блока 1 памяти микрокоманд читается микрокоманда, для выполнения которой в операционных схемах необходим первый, пятый и двенадцатый микротакты. При этом с информационных выходов регистра 2 микрокоманд операционная часть микрокоманды поступает на первую группу выходов устройства, а на выходах управляющих регистра 2 микрокоманд с порядковыми номерами 1, 5 и 12 будет присутствовать единичный сигнал (на остальных управляющих выходах будет нулевой сигнал). Единичные сигналы с управляющих выходов поступают на вход шифратора 9, в результате чего на его выходах формируется код 1100 (число 12 в двоичной системе счисления). Кроме того, эти сигналы поступают на первые входы перво 5го, пятого и двенадцатого элементов И 10. Формирование микротактов на выходах 14 происходит в соответствии с временной диаграммойй на фиг. 2 (принято К= 10) .При чтении микрокоманды в операционные схемы (например ЭВМ) запускается генератор 5 импульсов (шина запуска на чертеже не показана), при этом импульсы с его выходов поступают на вход делителя б частоты импульсов, коэффициент деления которого =1, Первыи же импульс генератора 5 вызывает появление импульса на первом выходе дешифратора 8 и Опрос первого элемента И 10, так как на обоих входах первого элемента И 10 присутствуют единичные сигналы, импульс с его выхода поступает на первый вход элемента ИЛИ 11, в результате чего на его выходе появляется импульс (а=1), что вызывает изменение коэффициента деления делителя б частоты 1=К. Таким образом, следующий импульс на выходе делителя б частоты импульсов появится лишь через К импульсов генератора 5, при этом К импульсов определяют длительность микропрограммного микротакта. Через К импульсов генератора Ь на выходе делителя б частоты импульсов появится сигнал, вызывающий появление импульса на втором выходе дешифратора 8, который поступает на второй вход второго элемента И 10, однако на первом входе этого элемента присутствует нулевой сигнал, что определяет нулевой сигнал на выходе элемента ИЛИ 11, поэтому а=0 и =1. Причем И=1 до тех пор, пока импульс не появится на пятом выходе дсшифратора 8, За счет присутствия единичных сигналов на входах пятого элемента И 10 на его выходе появляется импульс, вызывающий появление импульса на выходе элемента ИЛИ 11, который задает коэффициент деления делителя б частоты 1=К. Так продолжается до двенадцатого импульса на выходе делителя б частоты, Тринадцатый импульс на его выходе вызывает появление сигнала переполнения на выходе двоичного счетчика 7, который подготавливает чтение следующей микрокоманды, До этого времени на входы 13 блока 4 проверки условий из операционных схем поступают логические условия, по которым формируется адрес следующей микрокоманды и записывается в регистр 3 адреса. Поэтому чтение микрокоманды по сигналу с выхода переполнения двоичного счетчика происходит по заранее подготовленному адресу.Таким образом, для выполнения рассмотренной микрокоманды, в соответствии с временной диаграммой на фиг. 2, формируется три микротакта (первый, пятый и двенадцатый), Пропуски между. микротактами имеют небольшую величину и не оказывают существенного влияния на быстродействие цифровой аппаратуры, 640294 Микропрограммное устройство управления, содержащее блок памяти микро- команд, регистр адреса, регистр микро- команд, дешифратор, двоичный счетчик, генератор импульсов, блок проверки условий, группу элеменгов И, причем выходы двоичного счетчика соед 1 шены с соответству 1 ощими входами дешифратора, выходы блока проверки условии подключены к входам регистра адреса, выходы которого подключены к входам Олока памяти микрокоманд, выходы последнего соединены с информационными входами регистра микрокоманд, адресные выходы которого подключены к информационным входам блока проверки условий, управляющие входы которого соединены с первои группой входов устройства, управляющие выходы регистра микрокоманд соединены с первыми входами элементов И группы элементов И, отличающееся тем, что, с целью упрощения устройства, в него введены делитель частоты, элемент 11 Л 11, шифратор, причем входы шифратора сосдинены с управляющими выходами регистра микрокоманд, информационные выходы которого подключены и первой группе выходов устройства, выходы шифратора соединены соответственно с установочными входами двоичного счетчика, выход переполнения которого под 1"л 1 очен 1 1 правл 1110- щему входу регистра микроко анд, счетный вход двоичного счетчика соединен с выходом делителя частоты, первый вход которого соединен с выходом генератора импульсов, второй вход делителя частоты 5 10 15 20 25 30 35 40 45 50 55 60 65 В случае, если для выполнения микро- команды требуются другие микротакты, их формирование производится аналогичным образом.Таким образом, предложенное устройство реализует функции управления, позволяет формировать микрокоманды и обеспечивает условные и безусловные переходы. Однако это устройство позволяет дополнительно реализовывать микропрограммы, состоящие из линейных групп микро- команд с переменной длительностью такта в соответствии с действительным временем обработки микрокоманд. Это расширяет функциональные возможности заявленного устройства и дает возможность упростить устройство за счет использования значительно меньшего объема блока памяти микрокоманд.Предложенное микропрограммное устройство управления может быть использовано в оконечной аппаратуре автоматизированных систем управления, а также в универсальных и специализированных цифровых вычислительных машинах. Формула изобретения, дух ;л 71 1 ч" РВдписно 3;1 к:", Л/2 з,З Таво;рофи,:;р. с,.пунодг., 2 соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И группы элементов И и со второй группой выходов устройства, вторые входы элементов И группы элементов И соединены с соответствующими выходами дсшифратора,Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР467351, кл. 6 06 Р 9/16, 25,08.72.5 2. Авторское свидетельство СССР431515 кл. 6 06 Г 9/12, 26,05.72.

СмотретьЗаявка

2393456, 05.08.1976

ПРЕДПРИЯТИЕ ПЯ А-3327

СКЛЯРОВ ВАЛЕРИЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 9/16

Метки: микропрограммное

Опубликовано: 30.12.1978

Код ссылки

<a href="https://patents.su/4-640294-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для деления -разрядных чисел

Следующий патент: Устройство приоритета”

Случайный патент: Способ автоматического регу-лирования процессом приготовлениясуспензий