Вычислительная система для обработки чисел и многомерных векторов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

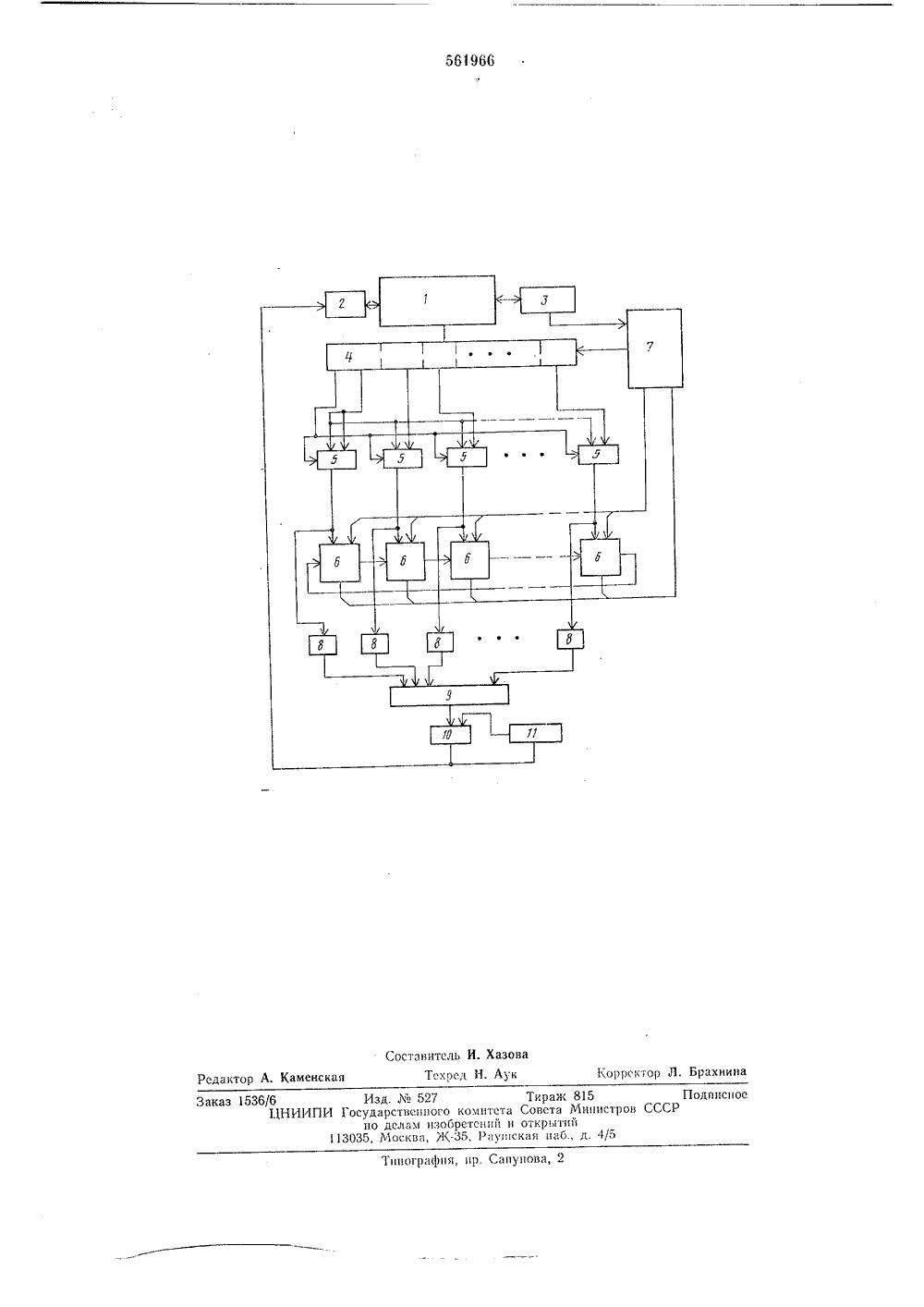

М. ФФее Ф м 1" т:. х ":".:. яез Нм е е :е-хИ Й Союз Советских Социалистических Республик(23) Приорите Опубликовано осударственныи комите Совета Министров СССР ае делам изооретеннй 53) УДК 681.325(088.8 ллетень " 5,06.77 и открыти ата опубликования оппсаипя 03.08.77(71) Заявитель 4) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ОБРАБОТК 1 ЧИСЕЛ И МНОГОМЕРНЫХ ВЕКТОРОВИзобретение относится к вычислительнои технике.Известкова вычислительная система для обработки чисел и многомерных векторов 11, содержащая устройство управления, соединенное двусторонними связями с блоком пуска и регистром адреса, регистр инструкций, разделенный на У групп разрядов, Х коммутаторов, У вычислительных устройств и запоминающее устройство, причем первый выход первой группы разрядов регистра инструкций соединен с первыми информационными входами всех коммутаторов, первые вход н выход запоминающего устройства соединены соответственно с первыми выходами и входами 1 - Л вычислительных устройств, причем второй выход каждого числительного устройства соединен со вгорым входом последующего, выходы каждого коммутатора соединены с третьими входами соответствующих вычислительных устройств, выход устройства управления соединен с первым входом регистра инструкций, второй вход которого соединен со вторым выходом запоминающего устройства, второй вход которого соединен с 25 выходом регистра адреса. Недостатком известной вычислительной системы является то, что выполнение операций, при которых в вычислительное устрой- ЗО ство один операнд поступает из запоминающего устройства, а другой - из соседнего вычислительного устройства, занимает время, равное сумме времен выполнения операций в каждом вычислительном устройстве.Наиболее близким техническим решением является вычислительная система для обработкн чисел и многомерных векторов 2, содержащая устройство управления, соединенное двусторонними связямп с блоком пуска и регистром адреса, регистр инструкций, разделенный на Л групп разрядов, Л коммутаторов, Л вычислительных устройств и запоминающее устройство, причем первый выход первой группы разрядов регистра инструкций соединен с первыми информационными входами всех коммутаторов, вторые информационные входы которых соединены соответственно с 1 - Л 7 группами разрядов регистра инструкций, а управляющие входы всех коммутаторов соединены с выходом режим работы первой группы разрядов регистра инструкций, первые вход и выход запоминающего устройства соединены соответственно с первыми выходами и входами 1 - Л вычислительных устройств, причем второй выход каждого вычислительного устройства соединен со вторым входом последующего, а второй выход Л-го вычислительного устройства соединен со вторым входом первого вычислительного устройства, веяходы каждого коммутатора соединены с третьими входамн соот 56196655 ветствующих вычислительных устройсгв, выход устройства управления соединен с первым входом регистра инструкций, второй вход которого соединен со вторым выходом запоминающего устройства, второй вход которого соединен с выходом регистра адреса.В известных вычислительных системах определение момента окончания обработки производится с помощью схем, обнаруживающих момент окончания переходного процесса, протекающего при выполнении какой-либо операции, при этом для каждой операции необходима отдельная схема, учитывающая специфику выполнения этой операциси. В связи с этим для обеспечения возможности определения момента окончания операции необходимо большое количество оборудования.Цель изобретения - уменьшение количсства оборудования.Это достигается тем, что предлагаемая вычислительная система содержит Л дешифраторов, суммирующий блок, блок сравнения и счетчик тактов, причем выходы коммутаторов соединены со входами соответствующих дешифраторов, выходы которых соединены с соответствующими входами суммирующего блока, выход которого соединен с первым входом блока сравнения, второй вход которого соединен с выходом счетчика тактов, а выход - со входом блока пуска и входом счетчика тактов.На чертеже показана схема предлагаемой вычислительной системы.Вычислительная система содержит устройство управлен 1 ия 1, соединенное двусторонними связями с блоком пуска 2 и регистром адреса 3, регистр инструкций 4, разделенный на Л групп разрядов, У коммутаторов 5, Ж вычислительных устройств 6 и запоминающее устройство 7, причем первый выход первой группы разрядов регистра инструкций 4 соединен с первыми информационными входами всех коммутаторов 5, вторые информационные входы которых соединены соответственно с 1 - Л группами разрядов регистра инструкций 4. Управляющие входы всех коммутаторов 5 соединены с выходом режим работы первой группы разрядов регистра инструкций 4, первые вход и выход запоминающего устройства 7 соединены соответственно с первыми выходами и входами 1 - У вычислительных устройств б, причем второй выход каждого вычислительного устройства 6 соединен со вторым входом последующего, а ,второй выход У-го вычислительного устройства б соединен со вторым, входом первого вычислительного устройства б, выходы каждого коммутатора 5 соединены с третьими входами соответствующих вычислительных устройств б, выход устройства управления 1 соединен с первым входом регистра инструкций 4, второй вход которого соединен со вторым выходом запоминающего устройства 7, второй вход которого соединен с выходом регистра адреса 3. 5 1 О 15 2 о 25 зо 35 4 О 45 50 1(роме того, вычислительная система содержит Л" дешифраторов 8, суммирующий блок 9, блок сравнения 10 и счетчик тактов 11, ,причем выходы коммутаторов 5 соединены со входами, соответствующих дешифраторов 8, выходы которых соединены с соответствующими входами суммирующего блока 9, выход которого соединен с первым входом блока сравнения 10, второй вход которого соединен с выходом счетчика тактов 11, а выход - со входом блока пуска 2 и входом счетчика тактов 11.Вычислительная система работает следующим образом,Начало каждого цикла обработки отмечается блоком пуска 2, разрешающего работу устройства управления 1, Инструкция, выполняемая в данном цикле, считывается из запоминающего устройства 7 по адресам регистра адреса 3 и принимается в регистр инструкций 4 при наличии соответствующих сигналов устройства управления 1.Содериимое регистра инструкций 4 через коммутаторы 5 поступаст во все вычислительные у стройства 6. При этом в зависимости от значения разряда режим работы, входящего в состав регистра инструкций 4, на входы;вычислительных устройств б пропускается либо код первой группы разрядов регистра инструкций 4, либо код нз той группы разрядов, номер которой совпадает с номером,вычислительного устройства 6.В соответствии с полученными инструкциями вычислительные устройства 6 выполняют операции над операндами, один из которых поступает из за)пожинающего устройства 7, а другой - из соседнего вычислительного устройства б.Таким образом, вычислительная система производит последовательную обработку Л операндов, причем результат операции, выполняемой в каждом вычислительном устройстве б, является одним из операндов для операции, выполняемой в соседнем вычислительном устройстве 6.Ввиду того, что длительность различных операций не одинакова, вовремя обработки вычислительной системы групп из У операндов также не одинаково, так как содержимое всех У групп разрядов в регистре инструкций 4 может быть различным.Для определения момента окончания обработки содержимое каждой группы разрядов регистра инструкций 4 (инструкция 1 вычислительного устройства 6) с коммутаторов 5 поступает на соответствующий дешифратор 8. Дешифраторы 8 производят преобразование кода числа, изображающего инструкцию вычислительного устройства б, в код числа,изображающего длительность выполняемой по этой инструкции операции в единицах времени, принятых для данной системы 1 например в долях такта).Эти числа поступают в суммирующий блок 9, в качестве которого может быть использован сумматор Л чисел, где подсчитывается с ммарное время необх 5 диОе для Выполне ния данной операции. Число с выхода суммирующего блока 9 поступает в блок сравнения 10, в этот же блок подается сигнал с выхода счетчика тактов 11, подсчитывающего число тактов, прошедших с момента начала обработки группы операндов.Когда число, поступающее из счетчика тактов 11 на входы блока сравнения 10, становится больше (или равно) числа, поступающего из суммирующего блока 9, на выходе блока сравнения 10 возникает сигнал окончания обработки, который поступает в блок пуска 2. После этого блок пуска 2 может формировать сигнал начала нового цикла обработки для устройства управления 1.Реализация предложенной вычислительной системы позволяет обеспечить высокое быстродействис системы при уменьшении количества оборудования, необходимого для выполнения блока окончания операций. Уменьшение ооорудования достигается за счет того, что вместо узлов, индицирующих момент окончания операции в каждом вычислительном устройствеприменены дешифраторы 8, соединенные с выходами коммутаторов 5,Формула изобретенияВычислительная систсма для обработки чисел и многомерных векторов, содержащая устройство управления, соединенное двусторонними связями с блоком пуска и регистром адреса, регистр инструкций, разделенный на Ю групп разрядов, У коммутаторов, Л вычислительных устройств и запоминающее устройство, причем первый выход первой группы разрядов регистра инструкций соединен с первыми информационными входами всех коммутаторов, вторые информационные входы которых соединены соответственно с 1 - Х группами разрядов регистра инструкций, а управляющие входы всех коммутаторов соединены с выходом режим работы первой 5 группы разрядов регистра инструкций, первые,вход и выход запоминающего устройства соединены соответственно с первыми выходами и входами 1 - Х вычислительных устройств, причем второй выход каждого вычис лительного устройства соединен со вторымвходом последующего, а второй выход Ж-го вычислительного устройства соединен со вторым входом первого вычислительного устройства, выходы каждого коммутатора соедине ны с третьими входами соответствующих вычислительных устройств, выход устройства управления соединен с первым входом регистра инструкций, второй вход которого соединен со вторым выходом запоминающего 20 устройства, второй вход которого соединенс выходом регистра адреса, отличающаяс я тем, что, с целью уменьшения количества оборудования, она содержит М дешифраторов, суммирующий блок, блок сравнения и 25 счетчик тактов, причем, выходы коммутаторовсоединены со входами соответствующих денгнфраторов, выходы которых соединены с соответствующими входами суммирующего блока, выход которого соединен с перовым входом З 0 блока сравнения, второй вход которого соединен с выходом счетчика тактов, а выход- со входом блока пуска и входом счетчика тактов.Источники информации, принятые во вниЗ 5 мание при экспертизе:1. Авторское свидетельство СССР М 330450,М. Кл, 6 ОбГ, 738, 03.0 б,70.2. Л. Н. Преснухнн, П. В. Нестеров, Цифровые вычислительные машины, Высшая шко ла, 1974, стр. 149 - 150 (прототип).Составитель И. Хазовадактор А. Каменскап Тскосд И, Аук Коррскт каз 1536/6ЦНИ ииографя, ир. Сапунова,Изд М 527 И Государственного по делам изоб 113035, Москва, )К Тираж 815комитета Совета Министров Сстсиий и открытий5, 1 аушская иаб., д. 4/5 рахнинаодписп

СмотретьЗаявка

2092245, 03.01.1975

ПРЕДПРИЯТИЕ ПЯ М-5489

БРИК ВЛАДИМИР АРКАДЬЕВИЧ, КАРЦЕВ МИХАИЛ АЛЕКСАНДРОВИЧ, ЛУШПИН ЛЕОНИД ИВАНОВИЧ, ПАХУНОВ ВЛАДИМИР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: векторов, вычислительная, многомерных, чисел

Опубликовано: 15.06.1977

Код ссылки

<a href="https://patents.su/4-561966-vychislitelnaya-sistema-dlya-obrabotki-chisel-i-mnogomernykh-vektorov.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительная система для обработки чисел и многомерных векторов</a>

Предыдущий патент: Устройство для обнаружения неисправностей цифровых систем

Следующий патент: Устройство для автоматического контроля сложных объектов

Случайный патент: Способ нарезания зубьев на рейках на зубодолбежных станках обкаткой