Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 509871

Авторы: Аспатуров, Бостанджян, Елисеев, Кондратьев, Мальцев

Текст

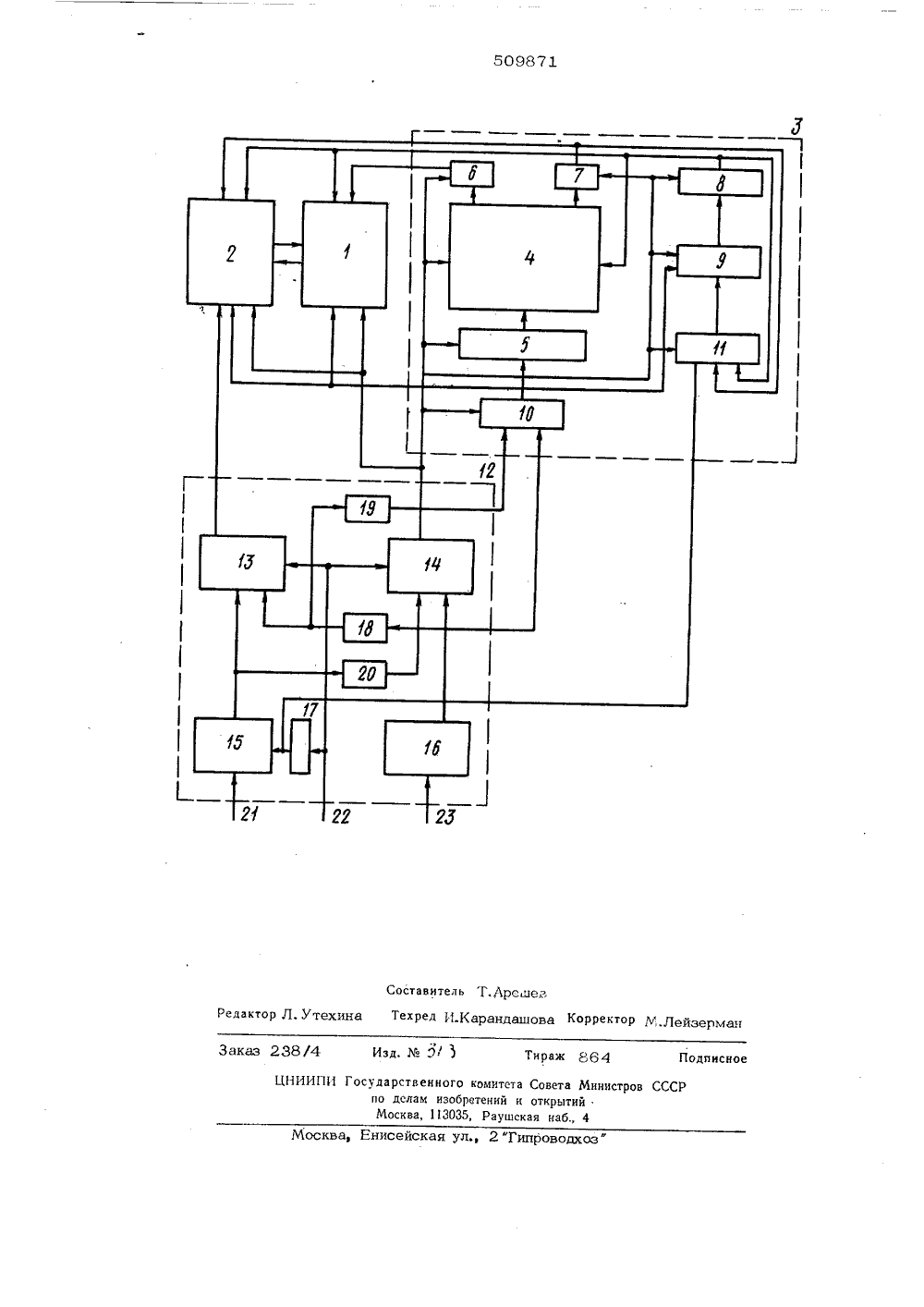

О П И С А Н И Е (11) 509871ИЗОБРЕТЕН ИЯ Союз СоветскихСоциалистическихРеспублик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ) Дополнительно ) Заявлено 03,05 авт. свид-в л. С 06 Г 15/002 1) 1913363/18-24 (51) присоединением заявки3) ПриоритетГосударственный комитет Совета Министров СССР по делам изобретений и открытий(45) Дата опублик ния описания 31, 08.7) Заявитель 4) ПРОЦЕССО Изоб з-за ных тение относится к области вычислхники и может быть применено М, атак ключени е из-запитания прператив . пе- бло ержашиеский блокя, содершифратор ы, сод метиче цик лом жаш 1авлен вляется повышени ть тивно ния оп м бло рм ом, узе атор синхроимпульсов, 10тором, узел выработки блок электропитания,ппаратного гашения иодержаший узел питаамяти, узел выработапряжений, узел управ я генераторов токаи стандартныхления отключениемия включением питатояния первичной питания, узел управлен ния и узел анализа со сети,Недстоит оцессоров сочении электропи 20аварийного состоючение одной статок из том, что стнь при отклю тан оцессора в случаеети (отксети илиения) инфо ия рвичнои первичной из з недопустимые рмация располоти процессора,изменеженная ия напряжв операт и памя тельнои тев ЭВМ,Известны процессор ративную память, ариф микропрограммного уп микропрограммную пам микроопераций управле мятью и арифметическ рования адреса, генер узел управления генера может быть искажена процессов в узлах ЭВ того, чтоаварийное о исходит несинхронно ной памяти,Целью изобретени надежности процессора.Для достижения этой цели в процессор введены узел анализа конца цнкла памяти и три элемента задержки. Вход первого эле мента задержки соединен с выходом узла управления включением питания, а выход . с третьим входом узла питания генераторов тока памяти и со входом второго элемента задержки, выход которого соединен с третьим входом узла выработки аппаратного гашения. Вход третьего элемента задержк соединен с выходом узла управления откл чением питания, а выход - с третьим вхо дом узла выработки стандартных напряжений, выход которого соединен с первым входом узла анализа конца цикла памяти, второй, третий и четвертый входы которого соединены соответственно с выходом генератора синхроимпульсов, с выходомдешифратора микроопераций управленияоперативной памятью и с выходом узлаанализа состояния первичной сети, а выходсоединен с одним из входов узла управлениягенератором, 5функциональная схема процессорапредставлена на чертеже,Процессор содержит арифметическийблок 1, оперативную память 2, блок микропрограммного управления 3, включающий 10микропрограммную память 4, узел формирования адреса 5, дешифратор 6 микроопераций управления арифметическим блоком,дешифратор 7 микроопераций управленияоперативной памятью, генератор синхроим 15пульсов 8, узел 9 управления генератором,узел 1 0 выработки аппаратного гашения иузел .11 анализа конца цикла памяти, Про;цессор содержит блок электропитания 12,состоящий из узла 13 питания генераторовтока памяти, узла 14 выработки стандартныхнапряжений узла 15 управления отключением питания, узла 16 управления включением питания, узла 17 анализа состоянияпервичной сети, первого 18, второго 1 9и третьего 20 элементов задержки, Процессор содержит также вход отключения пи тания 21, сетевой вход 22 и вход включения питания 23, 30Устройство работает следующим образом.Управление работой оперативной памяти 2 осуществляется дешифратором 7, который вырабатывает микрооперации чтения из оперативной памяти 2 или записи в оперативную память 2 в соответствии с микроко мандами, находящимися в микропрограммной памяти 4.В каждом машинном такте генератор синхроимпульсов 8 вырабатывает серию синхроимпульсов, стробирующих работу в оперативной памяти 2, арифметического блока 1 и микропрограммной памяти 4,При аварийном состоянии первичной се тп узел 17 вырабатывает сигнал о неис правности, поступающий в узлы 15 и 11. Еслн фиксация аварийного состояния первичной сети произошла после записи в оперативную память 2, но перед чтением из нее, то в конце текущего машинного такта 50 узел 11 выдает сигнал останова генера тора синхроимпульсов 8 в узел 9 управления генератором, Узел 15 при этом формирует сигнал отключения питания генераторов тока оперативной памяти 2, поступающий 55 в узел 13. Через время задержки на элементе задержки 20 формируется сигнал отключения стандартных напряжений, кс торый подается в узел 14. Если фиксация аварийного состояния первичной сети про 60 исходит при обращении к оперативной памяти 2, т, е. внутри цикла чтения записи оперативной памяти 2, то узел 11 выдает сигнал останова генератора синхрсимпульсов 8 только после того, как полностью отработается ,машинный такт, вкотором присутствует микрооперация записив оперативную память 2.Сигнал включения питания, поступающийв узел 16 приводит к тому, что к первичной сети подключаются узел 14 и 10,По потенциалу гашения происходитсброс в исходное состояние триггерныхсхем, которые могли бы вызвать непредусмотренное обращение к оперативной памяти2 в момент подачи питающих напряжений нагенераторы тока оперативной памяти 2,После установки потенциала гашения черезвремя задержки на элементе задержки 18происходит подключение первичной сети кузлу 13 и выдача питающих напряжений нагенераторы тока, Продолжительность выработки потенциала гашения определяетсясуммарным временем задержки элементов задержки 18 и 19, По сбросу потенциалагашения узел 5 подготавливает адрес первой микрокоманды микропрограммы гашения, а узел 9 запускает генераторсинхроимпульсов 8, после чего начинается выполнение микропрограммы гашения. В результате выполнения микропрограммы гашения сбрасываются в исходноесостояние те элементы процессора, которые не сброшены аппаратным гашением,но могут вызвать непредусмотренное обращение к оперативной памяти 2 ( а, следовательно, искажение информации в памяти)при работающем генераторе синхроимпульсов 8,формула изобретенияПроцессор, содержащий оперативную память, арифметический блок, блок микропрограммного управления, содержащий мик ропрограммную память, дешифраторы микроопераций управления оперативной памя тью и арифметическим блоком, узел формирования адреса, генератор синхроимпульсов, узел управления генератором, узел выработки аппаратного гашения, и блок электропитания, содержащий узел питания генераторов тока памяти, узел выработки стандартных напряжений, узел управления отключением питания, узел управления включением питания, узел анализа состояния первичной сети, причем первый вход узла управления отключением питания соединен со входом отключения питанияпроцессора, второй вход - с выходом узла анализа состояния первичной сети, авыход - с первым входом узла питаниягенераторов тока памяти, второй вход которого соединен с первым входом узла выработки стандартных напряжений, со входом узла анализа состояния первичной сети и ссетевым входом процессора, а выход соединен с первым входом оперативной памяти,второй вход которой соединен с первыми ц)входами арифметического блока, узла управления генератором, узла формирования адреса и с выходом узла выработки аппаратногогашения, первый вход которого соединен спервыми входами дешифраторов микроопераций управления оперативной памятью иарифметическим блоком, генератора синхроимпульсов, микропрограммной памяти, совторыми входами арифметического блока,узла формирования адреса, узла управления 20генератором, с третьим входом оперативнойпамяти и с выходом узла выработки стандартных напряжений, второй вход которогосоединен со вторыд входом узла выработкиаппаратного гашения и с выходом узла управления включением питания, вход которогосоединен со входом включения питания процессора, второй вход микропрограммной памяти соединен с выходом узла формирования адреса, первый выход соединен со вторым 30входом дешифратора микроопераций управленияарифметическим блоком, выход которого соединен с третьим входом арифметического блока, выход генератора синхроимпульсов соединен с четвертыми входами оперативнойпамяти и арифметического блока, с третьимвходом микропрограммной памяти, второйвыход которой соединен со вторым входомдешифратора микроопераций управленияоперативной памятью, выход которого соединен с пятым входом оперативной памяти,выход которой соединен с пятым входомарифметического блока, выход которого соединен с шестым входом оперативной памяти,о т л и ч а ю ш и й с я тем, что, с целью повышения надежности процессора, ондополнительно содержит узел анализа концацикла памяти и три элемента задержкипричем вход первого элемента задержки соединен с выходом узла управления включением питания, а выход - с третьим входомузла питания генераторОв тока памяти исо входом второго элемента задержки, выход которого соединен с третьим входомузла выработки аппаратного гашения; входтретьего элемента задержки соединен свыходом узла управления отключением питания, а выход - с третьим входом узлавыработки стандартных напряжений, выходкоторого соединен с первым входом узлаанализа конца цикла памяти, второй, третий,и четвертый входы которого соединенысоответственно с выходом генератора синхроимпульсов, с выходом дещифратора микроопераций управления оперативной памятьюи с выходом узла анализа состояния первичной сети, а выход соединен с третьимвходом узла управления генератором, 509871Составитель Т.ЛрсшевРедактор Л. Утехина Техред И.Карандашова корректор Х.Лейзерман Заказ 238/4 Изд. Ы 5/ 1 Тираж 864 ПодлисноеЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий Москва, 113035, Раушская наб., 4 Москва, Енисейская ул., 2 "Гипроводхоз"

СмотретьЗаявка

1913363, 03.05.1973

ПРЕДПРИЯТИЕ ПЯ М-5339

АСПАТУРОВ РУБЕН МИХАЙЛОВИЧ, БОСТАНДЖЯН ЮРИЙ ГРИГОРЬЕВИЧ, ЕЛИСЕЕВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ, КОНДРАТЬЕВ АНАТОЛИЙ ПАВЛОВИЧ, МАЛЬЦЕВ НИКОЛАЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: процессор

Опубликовано: 05.04.1976

Код ссылки

<a href="https://patents.su/4-509871-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Арифметико-логическое устройство

Следующий патент: Устройство для быстрого преобразова-ния фурье последовательности с нулевы-ми элементами

Случайный патент: Рабочий орган дреноукладчика