Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

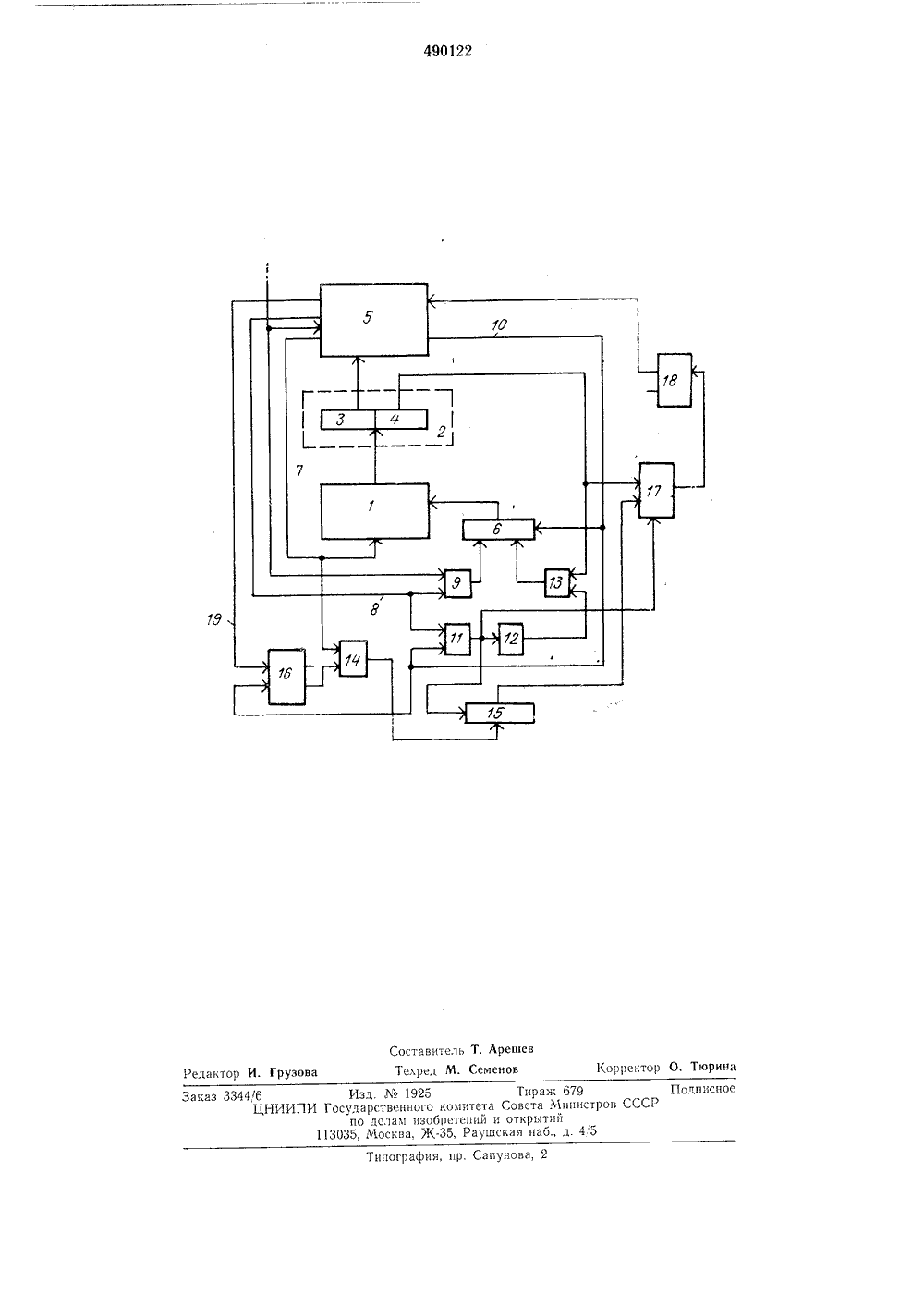

ОПИСХНИ ИЗОБРЕТЕН И К АВТОРСКОМУ СВИДЕТЕЛЬСТВ ц 49022 Союз Советских Социалистических Республик(51) М. Кл. 6 061 9/1 с присоединением заявки23) Государственнын комитет Совета Министров СССР)3)Д 1 х 681 326(088 Опубликовано 30.10.75. Бюллетень4 Дата опубликования описания 27.01.7 б о делам изобретен и открытий(34) МИКРО ычислительной роектированию Изобрегение относится к втехнике и, в частности, к ппроцессоров с контролем.Известны микропрограммные процессоры, содержащие операционный блок, блок памяти 5 микрокоманд, регистр микр оком анд, регистр адреса микрокоманд, счетчик микрокоманд, схему сравнения, триггер фиксации сбоя, два элемента И, элементы ИЛИ и НЕ.Первый выход операционного блока соеди нен шиной чтения микрокоманд с первым входом блока памяти микрокоманд, выход блока памяти микрокоманд - с входом регистра микрокоманд, первый выход которого подключен к первому входу операционного блока. Второй 1 о выход операционного блока соединен шиной начала операции с первым входом элемента ИЛИ и с первым входом первого элемента И. Второй вход первого элемента И связан с входом процессора, а выход этого эле мента И - с первым входом регистра адреса микрокоманд. Выход регистра адреса микрокоманд подключен к второму входу блока памяти микрокоманд, Третий выход операционного блока соединен шиной конца операции 2 с вторым входом регистра адреса микрокоманд и с вторым входом элемента ИЛИ, выход которого подключен к первому входу счетчика микрокоманд, первому входу схемы сравнения и через элемент НЕ к первому 3 входу второго элемента И. Второй вход второго элемента И соединен с вторым выходом регистра мнкрокома яд, выход - с третьим входом регистра адреса микрокоманд, а выход схемы сравнения - с входом триггера фиксации сбоя, выход которого под. ключен к второму входу операционного блока.Однако в известных процессорах контроль микропрограммных последовательностей требует значительных затрат оборудования и дополнительного времени для выборки проверочных чисел из оперативной памяти,Цель изобретения - упрощение процессора и повышение его быстродействия.Это достигается тем, что он дополнительно содержит триггер блокировки и третий элемент И, причем четвертый выход операционного блока соединен шиной блокировки счета с входом установки триггера блокировки, вход гашения которого связан шиной конца операции с третьим выходом операционного блока, а выход триггера блокировки подключен к первому входу третьего элемента И, второй вход которого соединен шиной чтения микрокоманд с первым выходом операционного блока, Выход третьего элемента И подсоединен к второму входу счетчика микрокоманд. Выход счетчика связан с вторым входом схемы сравнения, третий вход схемысравнения - -с вторым выходом регистра микрокоманд.Функциональная схема микропрограммногопроцессора приведена на чертеже, где 1 -блок памяти микрокоманд; 2 - регистр микрокоманд; 3 - поле микрокомапды регистрамикрокоманд; 4 - адресное поле регистра микрокоманд; 5 - операционный блок; б - адресный регистр микрокоманд; 7 - шина чтения микрокоманд; 8 - шина начала операции;9 - первый элемент И; 10 - шина концаоперации; 11 - элемент ИЛИ; 12 - элементНЕ; 13, 14 - второй и третий элементыИ; 15 - счетчик микрокоманд; 16 - триггерблокировки счета; 17 - схема сравнения; 18 -триггер фиксации сбоя; 19 - шина блокировки счета.Микрокоманды выбираются из блока 1 памяти микрокоманд в регистр 2 микрокоманд,Поле 3 микрокоманды управляет работой операционного блока 5. Адресное поле 4 определяет адрес следующей микрокоманды и передается после выполнения текущей микрокоманды в адресный регистр б микрокоманд,управляющий выборкой из блока памяти микрокоманд,Выборка микрокоманды управляется операционным блоком 5 с помощью передачисигналов по шине 7 чтения микрокоманд вблок 1 памяти микрокоманд. Операционныйблок осуществляет арифметические и логические преобразования информации и контролирует правильность их выполнения.Правильность считывания информации изпамяти микрокоманд в регистр 2 микрокоманд также контролируется по четности операционным блоком.Выполнение команды раздслепо па два цикла: цикл выборки команды из оперативнойпамяти и адресных преобразований и циклисполнения команды в СООГВстсГВИИ с кодо.;операции. Цикл выборки команды и адрсспГпхпреобразований является общим для всех команд, цикл исполнения командь Включаетразличные микропрограммы для разных команд.В конце цикла выборки команды и адресныхпреобразований операционный блок с контролем возбуждает сигнал на шине 8 началаоперации. При этом код операции командычерез элемент И 9 передается в старшиеразряды адресного регистра б и начинает выполняться микропрограмма цикла исполнениякоманды.В конце микропрограммы исполнения команды операционный блок 5 возблкдает сигнал на шине 10 конца операции, которыйгасит адресный регистр б и осуществляет переход к выполнению микропрограммы циклавыборки следующей команды.В ходе выполнения микропрограмм сигналына шинах начала 8 и конца 10 операции операционного блока отсутствуют, При этом Выход элемента ИЛИ 11 имеет нулевое значение, а выход элемента НЕ 12 - единичное50 ДД 60 65 Схема 17 сравнивает состояние счетчика микрокоманд с адресным ГГолем регистра микрокомапды и возбуждает сигнал на выходе при несовпадении информации на входах. При нормальной работе про Гессора в моменты появления сигналов на выходе элемента ИЛИ 11 выход схемы сравнения должен иметь значение О.При сбоях в последовательностях микро- команд в результате сбоев адресного регистра или схем возбуждения памяти микрокоманд Выход схемы сравнения имеет значение 1 в момент появления сигнала на выходе элемента ИЛИ 11, Триггер 18 фиксации сбоя, соединенный с Входом операционного блока, устанавливается в единичное состояние. 5 10 15 20 25 30 35 40 45 значение н элемсн 1 13 Осущсс ГВл 5 Гет ГРсредачу адреса очере Гной микрокоманды РГзадресно;о поля 4 р Гистра 2 мпкрокоманд Вадресный регистр б,Прп наг РНР с гнала на шине начала операции или шипе конца операции выход элемента ИЛИ Г 1 имеет сдишРчное значение,выход элемента 11 Е 12 - нулевое значениеи элемент И 13 закрывается.В работе микропрограммного процессоравесьма ва 5 кньРх является контроль работы адресного регистра и схем управления выборкойпам 5 Рти микро:,оманд, тРк как сбои этой аппаратуры могут привести к нарушениям гослсдоВатсльпости мРРкроГРрограхРхР, которые не обнаружены схемами коГ роля считывания информации из памяти микрокоманд,1(онтроль этой аппаратуры осущсствл яотследующим образом.Каждая микропрограмма исполнения команд, цикл Выоорки команды и адресных преобразований имеют определенное число микрокомапд, Аппаратура процессора подсчитывает число микрокоманд, выполняемых в цикле ВВРОорки н в цикле исполнения командьР, исраВниВает его с заданным, При несОВпадснии фиксируется сбой.При выполнении микрокоманд, формирующих сигналы па шинах начала операции иконца Операции ОГРерациОПРРО 0 бГГОка, элемснтИ 13 закрыт и адресное поле 4 ре:истрамикрокомапды свооодно, в эти моменты вре.лени адрес следующей микрокоманды определяется нс адресным полем регистра микрокоманд, а содс 1)РИРРхГВГх регистра кода Операции операционного блока или полем микрокоыандь. В эти мохснты Времен: Оно исполь 3 етс 5 д.5 кон 1)ол 5 прРРВильпости РОследоВательРРости микрокоманд.В м;РкрскомаПах, записаншГ х В конГ,е циклов Выборки команды и циклов;сполнения команд, записывается число мпкрокомапд, выполняемых В данном цикле, Прп чтешРН каждоймикрокомян.Гы сигРал с шРРпысни 5 микрокомандь. через элемент И 14 поступает насчетный вход счетчика 15 микрокоманд, еслитриггер 16 блоРи 1 Овки счета усРановлен в положение О.В конце цикла выборки команды и цикла исполнения команды сигнал с выхода элемента ИЛИ 11 передается на вход гашения счетчика 15 микрокоманд и с началом нового цикла снова проводится подсчет микрокоманд. При выполнении некоторых команд количество микрокоманд в микропрограмме не постоянно, а зависит от дополнительных условий выполнения команды. В этом случае в конце последовательности микрокоманд, которая постоянна для данной команды, подается микрокоманда, возбуждающая сигнал на шине блокировки счета операционного блока, который устанавливает в 1 триггер блокировки счета. При этом элемент И 14 закрывается и добавление 1 к счетчику микрокоманд прекращается.В этом случае в адресном поле последней микрокоманды данной команды записывается число микрокоманд, которое выполняется до момента исполнения микрокоманды блокировки счета, и, независимо от количества выполняемых микрокоманд в последующей переменной части выполняемой команды, содержимое счетчика микрокоманд должно быть равно содержимому адресного поля последней микрокоманды. В таком режиме работы также осуществляется контроль правильности последовательности микрокоманд, так как при сбое в адресном регистре или схемах возбуждения памяти микрокоманд начинает выполняться другая микропрограмма и содержимое счетчика микрокоманд не совпадает с содержимым адресного поля последней микрокоманды,Предмет изобретенияМикропрограммный процессор, содержащий операционный блок, блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, счетчик микрокоманд, схему сравнения, триггер фиксации сбоя, два элемента И, элементы ИЛИ и НЕ, причем первый выход операционного блока соединен 5 10 15 20 25 ЗЭ 35 40 шиной чтения микрокоманд с первым входом блока памяти микрокоманд, выход которого соединен с входом регистра микрокоманд, первый выход которого соединен с первым входом операционного блока, второй выход которого соединен шиной начала операции с первым входом элемента ИЛИ и с первым входом первого элемента И, второй вход которого соединен с входом процессора, а выход первого элемента И соединен с первым входом регистра адреса микрокоманд, выход которого соединен с вторым входом блока памяти микрокоманд, третий выход операционного блока соединен шиной конца операции с вторым входом регистра адреса микрокоманд и с вторым входом элемента ИЛИ, выход которого соединен с первым входом счетчика микрокоманд, первым входом схемы сравнения и через элемент НЕ с первым входом второго элемента И, второй вход которого соединен с вторым выходом регистра микро- команд, а выход - с третьим входом регистра адреса микрокоманд, выход схемы сравнения соединен с входом триггера фиксации сбоя, выход которого соединен с вторым входом операционного блока, отличающийся тем, что, с целью упрощения процессора и увеличения его быстродействия, он дополнительно содержит триггер блокировки и третий элемент И, причем четвертый выход операционного блока соединен шиной блокировки счета с входом установки триггера блокировки, вход гашения которого соединен шиной конца операции с третьим выходом операционного блока, а выход триггера блокировки соединен с первым входом третьего элемента И, второй вход которого соединен шиной чтения микрокоманд с первым выходом операционного блока, а выход третьего элемента И соединен с вторым входом счетчика микрокоманд, выход которого соединен с вторым входом схемы сравнения, третий вход которой соединен с вторым выходом регистра микро- команд.490122 оставитель Т. Арешев екред М. Сем ен ов Корректор О. Тюрина Редактор И. Грузо ПодписноСР аказ 33446 Типография, пр. Сапунова,Изл. М 1925 1 ИИПИ Государственного по делам изо 113035, Москва. Ж

СмотретьЗаявка

1915977, 07.05.1973

ПРЕДПРИЯТИЕ ПЯ Г-4128

УЛЬЯНОВА ЕЛЕНА КОНСТАНТИНОВНА, МАСЛОВА ЖАННА РОБЕРТОВНА, СТЕПАНОВ ВИКТОР НИКОЛАЕВИЧ, ЕВДОЛЮК ЮРИЙ МАКСИМОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммный, процессор

Опубликовано: 30.10.1975

Код ссылки

<a href="https://patents.su/4-490122-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Устройство для обнаружения неисправностей в электрическом монтаже

Случайный патент: Способ получения ионитов