Система передачи бинарных сообщений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

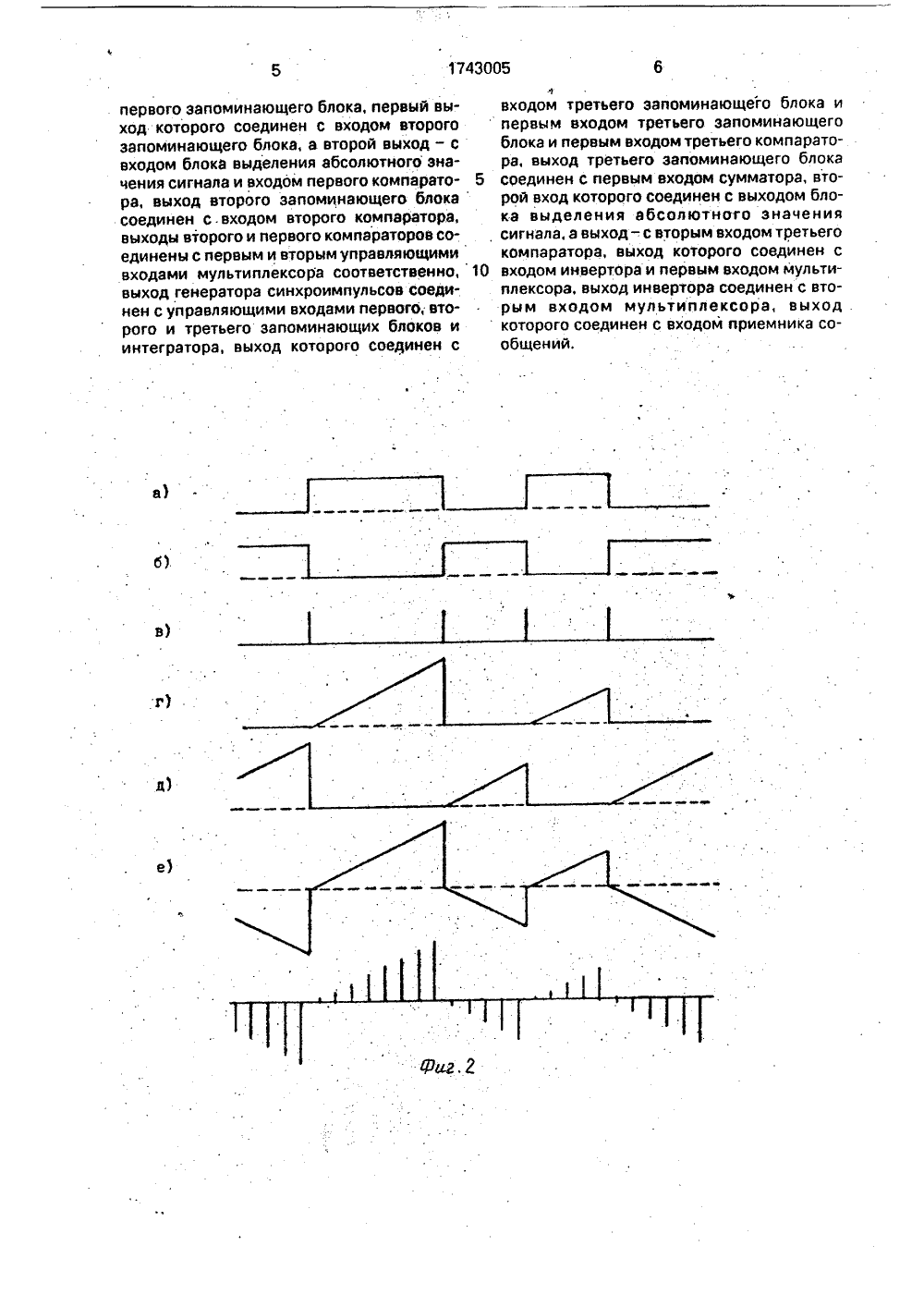

(19 5 Н 04 В 1/ НИЯ 2 ехническийКазаков статут ация и 81,ИНАРН е.при ет 1980 АЧИ 1 Х СОтения; система стороне источн два интеграто содерк 1 соа.3 и 6,ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ.ПРИ ГКНТ СССР ОПИСАНИЕ И ЗОБ Р ВТОРСКОМУ СВИДЕТЕЛЬСТВУ(57) Сущность изобрежит на передающейобщений, инвертор 2,блок 4 выделенияфронтов импульсов, сумматор 5, дискретизатор 7, канал 8 связи, на приемной стороне: три запоминающих бло- . " ков 9, 10 и 16, три компаратора 11, 13 и 18, . блок 12 выделенияабсолютного значения сигнала, мультиплексор 14, генератор 15 синхроимпульсов, интегратор 17, сумматор 19, инвертор 20, сумматор 19, инвертор 20, приемник 21 соотношений. 1-3 - .5-7-8-.9- 10-11-13 - 14-,21, 1 - 4 - 3, 1-2-6-5, 4-6, 15 - 9- 11-14, 9 - 12-19 - 18-20.-14, 15-17-16-19, 15-16, 17-18-14, 15-10,3 ил,Изобретение относится к системам передачи информации.Цель изобретения - повышение точности передачи бинарного случайного процесса,На фиг.1 изображена электрическаясхема системы; на фиг.2 и 3 - временныедиаграммы передающей и приемной сторон, поясняющее работу.Система содержит на передающей стороне источник 1 сообщений, инвертор 2,первый интегратор 3, блок 4 выделенияфронтов импульсов, сумматор 5, второй интегратор 6,.дискретизатор 7, канал 8 связи,на приемной стороне - первый, второй запоминающие блоки 9 и 10, первый компаратор 11, блок 12 выделения абсолютногозначения сигнала, второй компаратор. 13,мультиплексор 14, генератор 15 синхроимпульсов, третий запоминающий блок 16, ин.тегратор 17, третий компаратор 18,.сумматор 19, инвертор 20,Система работает следующим образом,Бинарный случайный процесс (фиг,2 а),а также. инверсный процесс на выходе инвертора 2 (фиг,2 б) интегрируются интеграторами 3 и 6 (фиг.2 г,д). Постоянные времениинтеграторов одинаковы и выбраны достаточно большими, так что напряжения на их. выходах можно считать линейно изменяющимися. Схема выделения фронтов импульсов 4 формирует сбросовые импульсы дляинтеграторов (фиг.2 в) по каждому фронту(как переднему. так и заднему) импульсоввходного процесса. Сумматор 5 объединяетвыходные сигналы интеграторов (фиг.2 е), адискретиэатор 7 формирует последовательность дискретных .амплитудно-модулированных импульсов, которая подается вканал 8 связи, Временные диаграммы; поясняющие работу системы на приемной сто, роне, приведены на фиг,З в несколькобольшем масштабеВовремя появления импульса на выходе канала связи(фиг.За) генератор синхроимпульсов 15 формирует тактовый импульс(фиг;Зб) по которому происходит фиксациятекущей выборки в запоминающем блоке 9(фиг.Зг), предыдущей выборки в запоминаю. щем блоке 10 (фиг,Зд), а также осуществляется сброс интегратора 17 формирующегопилообразное напряжение (фиг.Зв) и имеющего постоянную времени, равную постоянным интеграторов 3 и 6, запоминаниеамплитуды пилы в запоминающем блоке 16,Величина напряжения на входе интегратора17 равна амплитуде импульсов бинарного. процесса на входе системы передачи. Компараторы 11 и 13 производят сравнениевходных сигналов запоминающих блоков 9 и 10 с нулевым значением (фиг.Зе,ж) и осуществляют управление мультиплексором 14.Сумматор 19 формирует разность 5 (фиг.Зи) между выходной величиной запоминающего блока 16 и выходной величиной схемы выделения абсолютного значения сигнала 12 (фиг.Зв). Компаратор 18 производит сравнение пилообразного напряжения 10 с интегратора 17 и сигнала с сумматора 19(фиг.Зл). Логика работы мультиплексора 14 такова: если на обоих его управляющих входах. присутствуют нули с компараторов (такая ситуация возможна, если две 15 предыдущие выборки отрицательныпо амплитуде, т,е, на входе системы передачи. - ноль, то он подключает вход приемника сообщений 21 к своему первому входу, соединенному с нулем, а если на обоих 20 управляющих входах единичные значения:сигнала, он выдает приемнику сообщений единичное значение с четвертого входа. Если же две последние выборки имеют противоположные знаки (т,е; на предыдущем 25 интервале дискретизации произошел скачок входного бинарного процесса), то в за- висимости от направления перепада и соответственно выходных сигналов кОмпараторов 11 и 13 по входу приемника сооб щений подключается либо выходной сигналс компаратора 18 (фиг.Зн) при положительном перепаде, либо сигнал.с инвертора.20 (фиг.Зм) при отрицательном перепаде,Формул а и зо бр ете нияСистема передачи бинарных сообщений, содержащая на передающей стороне источник сообщений и дискретизатор, вы ход которого соединен с входом канала свя.зи, а.на приемной стороне - приемник .сообщений,отл ича юща я с я тем,что, с целью повышения точности передачи, введены на передающей стороне инвертор, два 45 интегратора, сумматор. и блок выделенияфронтов импульсов, причем выход источника сообщений соединен с входами первого интегратора, инвертора и блока выделения фронтов импульсов, выход которого соеди нен с управляющими входами первого и второго интеграторов, выходы которых соединены с входами сумматора, выход которого соединен с входом дискретиэатора, выход инвертора соединен с входом второго 55 интегратора, а на приемной стороне - генератор синхроимпульсов, интегратор, три запоминающих блока, три компаратора, блок выделения абсолютного значения сигнала, сумматор, инвертор и мультиплексор, причем выход канала связи соединен с входомпервого запоминающего блока, первый выход которого соединен с входом второго запоминающего блока, а второй выход - с входом блока выделения абсолютного значения сигнала и входом первого компаратора, выход второго запоминающего блока соединен с.входом второго компаратора, выходы второго и первого компараторов соединены с первым и вторым управляющими входами мультиплексора соответственно, выход генератора синхроимпульсов соединен с управляющими входами первого; второго и третьего запоминающих блоков и интегратора, выход которого соединен с входом третьего запоминающего блока и первым входом третьего запоминающего блока и первым входом третьего компаратора, выход третьего запоминающего блока 5 соединен с первым входом сумматора, второй вход которого соединен с выходом блока выделения абсолютного значения сигнала, а выход- с вторым входом третьего компаратора, выход которого соединен с 10 входом инвертора и первым входом мультиплексора, выход инвертора соединен с вторым входом мультиплексора, выход.которого соединен с входом приемника сообщений.5 Тир ПИ Государственного113035,итета по и ква, Ж,Подписноеретениям и открытиям при ГКНТ СССРшская наб., 4/5

СмотретьЗаявка

4885260, 26.11.1990

РЯЗАНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

БЕЛЯЕВ МИХАИЛ АНАТОЛЬЕВИЧ, КАЗАКОВ ВЛАДИМИР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H04B 1/62

Метки: бинарных, передачи, сообщений

Опубликовано: 23.06.1992

Код ссылки

<a href="https://patents.su/4-1743005-sistema-peredachi-binarnykh-soobshhenijj.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи бинарных сообщений</a>

Предыдущий патент: Устройство для приема, регенерации и передачи относительного биимпульсного сигнала

Следующий патент: Устройство защиты кабельной линии связи

Случайный патент: Измерительное акустическое устройство