Формирователь сигналов с амплитудной и угловой модуляцией

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1672551

Автор: Аввакумов

Текст

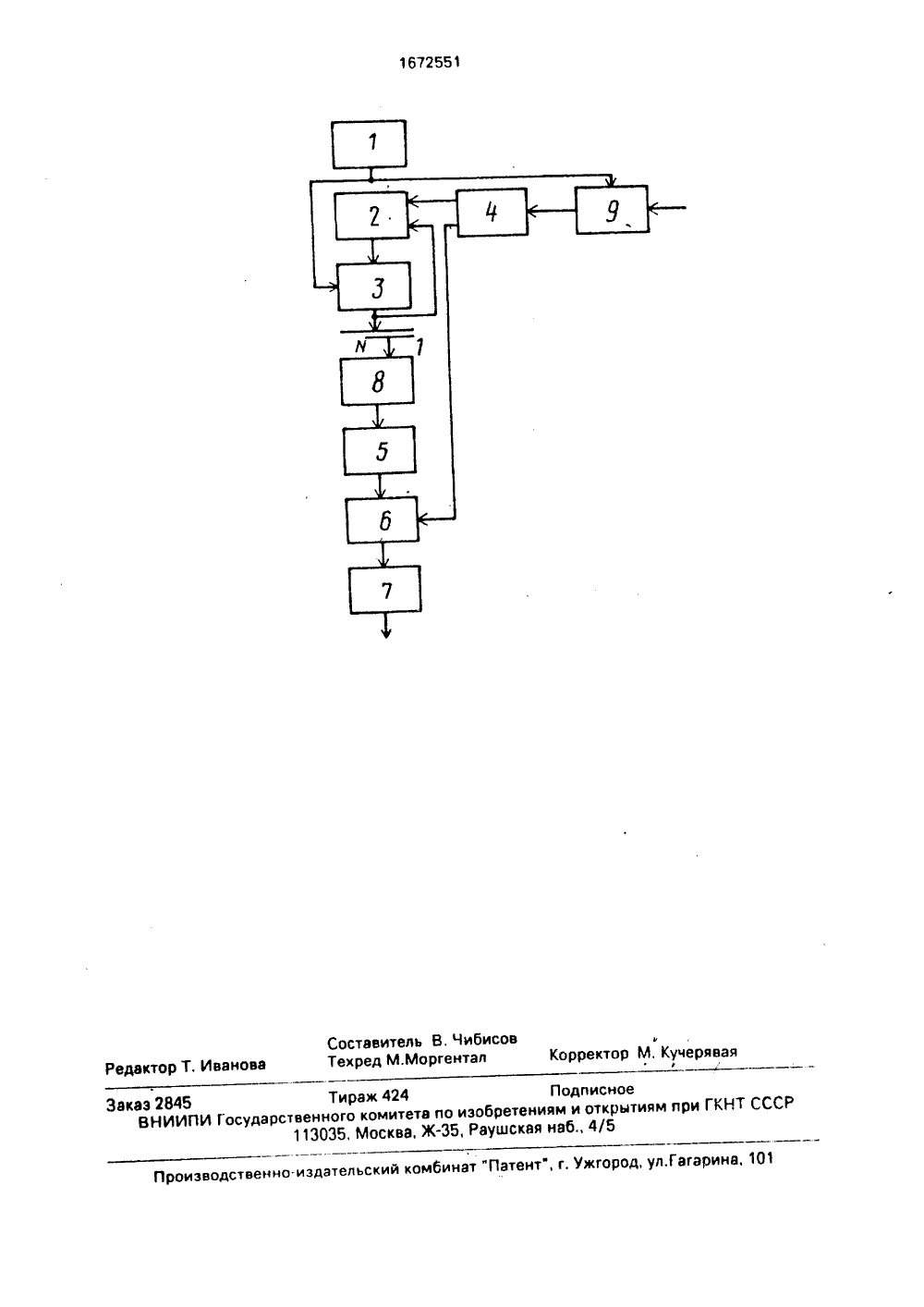

(57) Изобретение относится ки может использоваться в сисчи сигналов с амплитудной иляцией, Цель изобретения -диапазона частот формируеФормирователь сигчалов с эугловой модуляцией содержитактовых импульсов, двоичньпервый регистр 3 памяи, ппостояннои памяти, цифроанобразователь 5, второй реги Изобретможет и ние отсосится к радиотехнике пользоваться -:, сис емах алов с лмплитуднои и угловой передачи сигнмодуля цией.Цель изобзона ча"тог ф етения - расцсирение диармируем, о сигнала,На чертеже представлена электрическая схесла предложенного формирователя,Формировател. сигналов с амплитудной и угловой модул цией содержитонерагор 1 тактовых импульсов. двоичный сук матор , первый регистрпамяти. персзый блок 4 посточнной памяти, цифроаналоговый преобразо атель 5, пеоемножающий цифроаналоговый преобразователь б,ГОСУДАРСТВЕННЬСй КОМИС ЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР С ГР985НАЛОВ С АМОДУЛЯЦИЕЙ радиотехнике темах передаугловой лодурас лирение мого сигнала,мплитуд;ой и т генераор с й сумматор 2,ервый блок 4 злоговы й и рестр 9 памяти,Цель достигается введением перемножающе"о цифроаналоговосо преобразователя 6, фильтра 7 нижних частот, второго блока 8 постоянной памяти. Сумматор 2 и регистр 3 образуют накопительный сумматор, который используется в качестве делителя частоты с дробно-переменным коэффициентом деления. На выходе блока 8 появгяется код амплитуды синусоидального колебания, соответствующий текущей фазе формируемого сигнала, Преобразователь 5 преобразует его в н;пряжение, которое постпает на преобразователь 6 на цифровос вход которосо с второ; о аыода блока 4 поступает код тек, дего значения амплитуды формируемого сигнала Фильтр 7 нижних частот очищает спектр формируемого сигнала от помех кгсдчтования с частотой, равчой частоте следования импульсов с вьслода гесератор:, 1., илгр 7 нижн стоянчои пам,ст Формирова образом Мод/лиру сиГнальчый вхо и запи"ьвается вход синхрониз нератооа 1 такт чиеает синхро ИсЗ 3 ИМГсУЛЬ тактовых импу можность сбое сигналов с ам ляцией из-за го сигнала наих частот, второй блол 8 пои и второй региср 9 пас.яти, тель работает следующим ющий сигнал поступает на д второго регистра 9 памятив него по приходу на его ации импульса с выхода сеодых имоульсоч. Это обеспенизац,сю модул ируюсцего сами с,.ыхода сепаратора 1 льсов, чем ус.ранчется воза в работе формирователя плитудной и у ловои моду. изменения модулирующеинтервале времени междуприходом соседних импульсов с выходагенератора 1 тактовых импупьсое.С выхода второго регистра 9 памятимодулирующий сигнал поступает на адресный вход первого бпока 4 постоянной памяти, в котором в двоичном коде хранятсячисленные значения приращения фазы формируемого сигнала за период частоты следования импульсов с выхода генератора 1тактовых импульсов и численные значениятекущей амплитуды формируемого сигналана интервале между приходом соседних импульсов с выхода генератора 1 тактовых импульсов. Законы изменения численныхзначений приращения фазы и текущей амплитуды формируемого сигнала в соответствии с модулирующим сигналом выбирают,исходя из требований получения минимального уровня внеполосового излучения,С первого выхода первого блока 4 кодприращения фазы поступает на первыйвход двоичного сумматора 2. Выход двоич, ного сумматора 2 соединен с сигнальнымвходом первого регистра 3 памяти, в котором хранится код текущего значения фазыформируемого сигнала, Сигналы с выходоввсех разрядов первого регистра 3 памятипоступают на второй вход двоичного сумматора 2, Таким образом, на выходе двоичногосумматора 2 присутствует код вновь вычисленного значения фазы формируемого сигнала, равный сумме кода текущего значенияфазы формируемого сигнала с выхода первого регистра 3 памяти и кода приращенияфазы формируемого сигнала с первого выхода первого блока 4. По приходу каждогоимпульса с выхода генератора 1 тактовыхимпульсов на вход синхронизации первогорегистра 3 памяти в него записываетсявновь вычисленное значение кода фазыформируемого сигнала, которое после этого становится текущим значением кода фазы формируемого сигнала,Таким образом, двоичный сумматор 2 ипервый регистр 3 памяти образует так называемый накопительный сумматор, который в данном случае используется вкачестве делителя частоты с дробно-переменным коэффициентом деления. Частота Е формируемого сигнала, получаемогос помощью этого делителя, определяетсяпо формулеЕ=РО (1)2 Мгде Г - частота формируемого сигнала;РО - частота следования импульсов свыхода генератора 1 тактовых импульсов;В - код приращения фазы формируемого сигнала;10 15 ОР - число двоичных разрядов двоичного сумматора 2 и первого регистра 3 памяти.Минимально возможное изменение частоты формируемоо сигнала (шаг сетки частот ЛР) получается при изменении кодаВ приращения фазы на единицу младшегоразряда и определяется по формулеог (2)ГОПри необходимости в течение одного периода частоты следования импульсов с выхода генератора 2 тактовых импульсов изменить фазу формируемого сигнала на величину Лр производят изменение кода приращения фазы формируемого сиг 20 25 30 35 40 45 50 55 нала на величину Л В, определяемую по формулеЛВ=-2 , (3)360Сигналы с выходов М старших разрядов первого регистра 3 памяти поступают на адресный вход второго блока 8 постоянной памяти, в котором хранятся численные значения выборов одного периода синусоидального колебания. При поступлении на адресный вход второго блока 8 постоянней памяти текущего значения кода фазы формируемого сигнала с выходов М старших разрядов первого регистра 3 памяти на вы. ходе второго блока 8 постоянной паМяти появляется код ампли гуды синусоидального колебания, соответствующий текущей фазе формируемого сигнала, Этст код поступает на цифровой вход цифроаналогового преобразователя 5, с помощью которого он преобразуется в аналоговое напряжение.С выхода цифроаналогового преобразователя 5 аналоговый синусоидапьньй сигнал с постоянной амплитудой поступает на вход опорного напряжения перемножающе о цифроаналогового преобразователя б, на цифровой вход которого с второго выхода первого блока 4 постоянной памяти поступает код АТ текущего значения амплитуды формируемого сигнала. Амплитуда А сигнала на выходе перемножающего цифроаналогового преобразователя б определяется по формулеА=АО ", (4)2где Л - амплитуда формируемого сигнаа на выходе перемножающего цифроаналогового преобразователя 6;АО - амплитуда сигнала на выходе цифроаналогового преобразователя 5;АТ - код текущего значения амплитуды формируемого сигнала, 1572551ОА - число двоичных разрядов цифоового входа перемножэющего цифроаналогового преобразователя 6.Аналоговый сигнал с выхода перемножающего цифроаналогового преобраэователя б поступает на фильтр 7 нижних частот,который служит для очищения спектра фоомируемого сигнала от помех квантования счастотой, равной частоте следования импульсов с выхода генератора 1 тактовых импульсов,Таким образом, на выходе фильтра 7нижних частот присутствует аналоговыйсинусоидальный сигнал с амплитудой,определяемой по формуле (4), и частотой, 15определяемой по формуле (1). Причем шагЛГ сетки частот формируемого сигнала на выходе предложенного формирователя сигналов с амплитудной и угловой модуляциямизначительно меньше, чем в известном формирователе сигналов с амплитудной и угловой модуляциями при одинаковом объемепервого блока 4 постоянной памяти. Этообъясняется тем, что для формированиясигнала с постоянными амплитудой, частотой и фазой, т,е. элементарного сигнала, иэнабора которых можно сформироватьтребуемый закон изменения амплитуды, частоты или фазы, в предложенном формироват-ле с 1 ггналсв с ампли удной и угловой ддмодуляциями требуется хранение в первомблоке 4 пост янн;й памяти только о;.ногомногоразрядного;. ова, сэстояще о из кодаБ приращения фаза и из кода АТ текущеРамплитуды формируемо о сигнала. При 35этом число ОР ячеек памяти в первом блоке4 постоянной памяти, требуемых для хранения информации о сип але с постоянными амплитудой, частотой и фазой определяе 1- ся по формулеОР = ОГ+ ОА, (5)Формула изобретения Формирователь сиг алов с амплитудной и угловой модуляцией, содержащий цифроаналоговый преобразователь и генератор тактовых импульсов, выход которого подключен к синхронизационным входам первого регистра памяти, выходы разрядов которого соединены с первым входом двоичного сумматора, и второго регистра памяти, выход которого подключен к адресному входу первого блока постоянной памяти, при этом сигнальный вход второго регистра памяти является модулирующим входом формирователя, о т л и ч а ю щ и й с я тем, что, с целью расширения диапазона частот формируемого сигнала, в него введены второй блок постоянной памяти и последовательно соединенные перемножающий цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом формирователя, причем первый и второй выходы первого блока постоянной памяти подключены соответственно к второму входу двоичного сумматора, выход которого соединен с сигнальным входом первого регистра памяти, и к цифрое чу входу перемножвющего цгброан.;- логового г;реобрэзоввтеля, опорный вход которого соединен с выходом цифроаналогово, о преобразователя, к входу которого подключен выход второго блока постоянной памяти, адресный вход которого .:оединен с выходами старших разрядов пере го ре.истра памят 1,Гагарина, 101 роизводственно-издательский ент, г. Ужго кээ 2845 Тираж 424 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4689234, 05.05.1989

ПРЕДПРИЯТИЕ ПЯ А-1307

АВВАКУМОВ ЯРОСЛАВ ОЛЕГОВИЧ

МПК / Метки

МПК: H03C 5/00

Метки: амплитудной, модуляцией, сигналов, угловой, формирователь

Опубликовано: 23.08.1991

Код ссылки

<a href="https://patents.su/4-1672551-formirovatel-signalov-s-amplitudnojj-i-uglovojj-modulyaciejj.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь сигналов с амплитудной и угловой модуляцией</a>

Предыдущий патент: Многоканальный генератор случайных сигналов

Следующий патент: Амплитудный детектор

Случайный патент: Малогабаритная чесальная машина