Устройство для вычисления систем булевых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1631537

Автор: Беляков

Текст

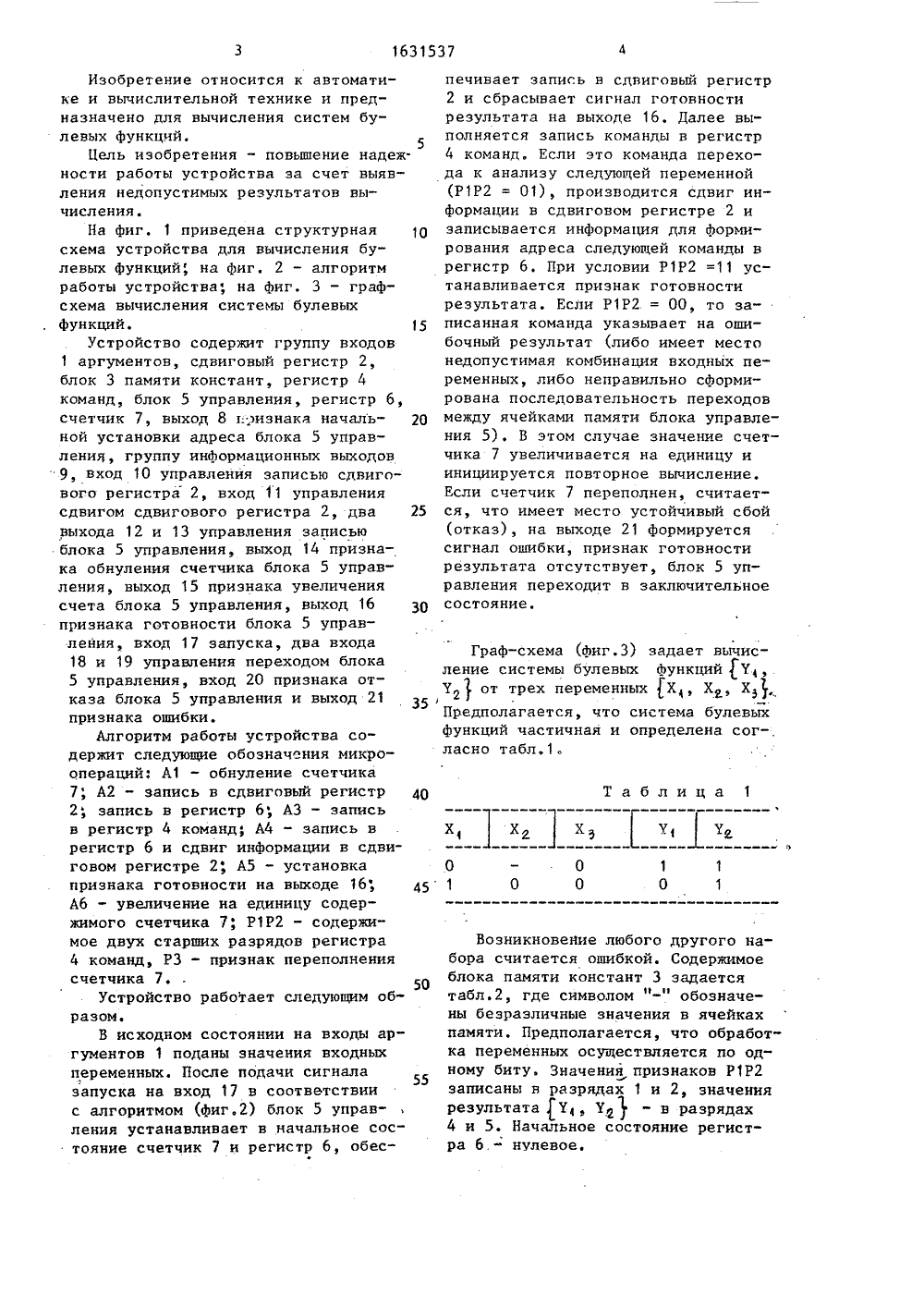

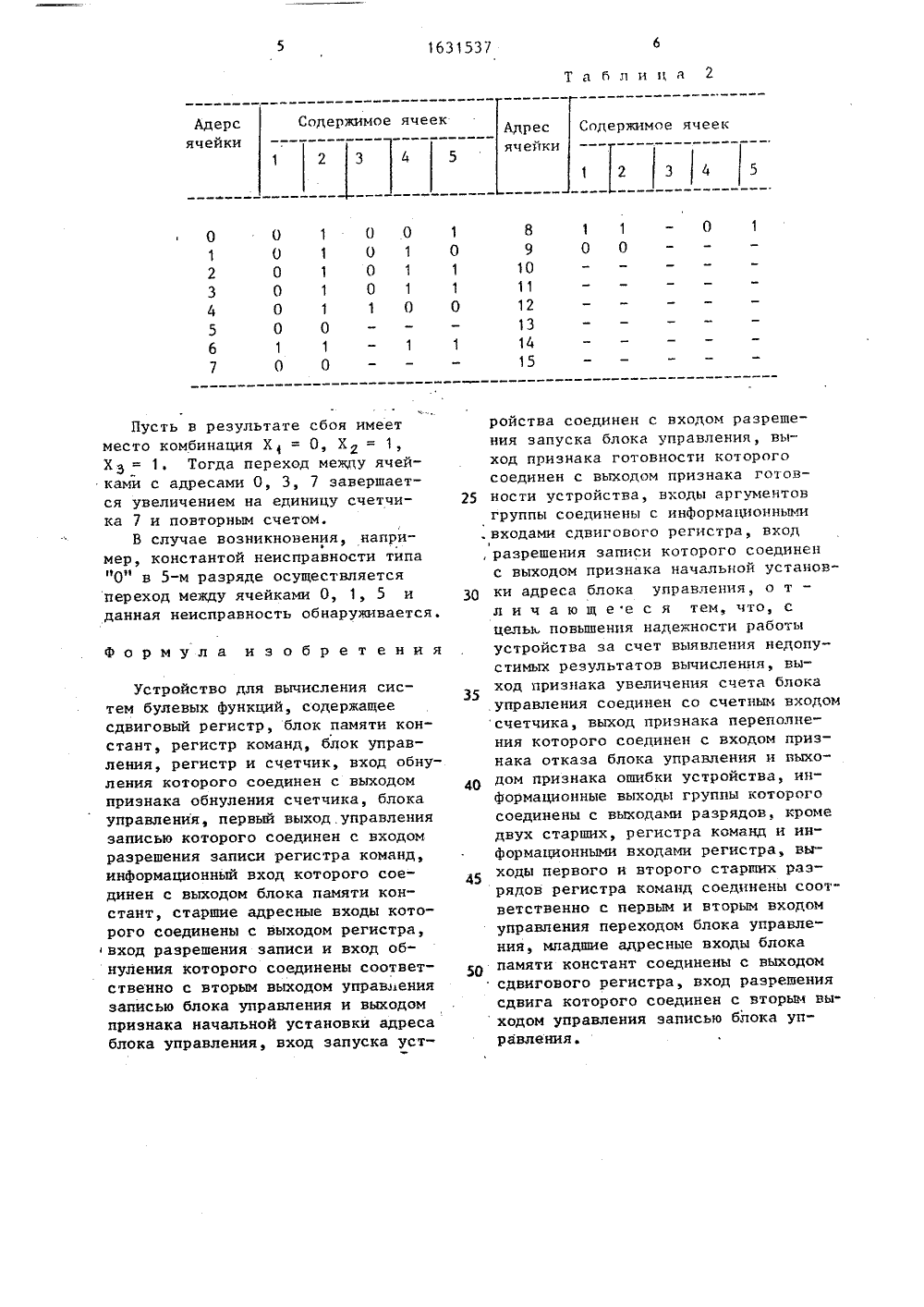

:;гг И ЕНИЯ ЕЛЬСТВУ Московског а им.Серго СССР1987.ССР198.8.(54) УСТРО СИСТЕМ БУЛ (57) Изобр матике и в предназнач булевых фу ЕНИЯ ЙСТВОЕВЫХ ФУНетениеычислит ДЛЯ ВЫЧИСЛ КЦИЙ тносится ельной те вычисленавтохнике ия систе бретения кций лью ГОСУДАРСТВЕННЫЙ НОМИПО ИЗОБРЕТЕНИЯМ И ОТНРЫТПРИ ГННТ СССР А ВТОРСКОМУ СВИ,80,1631537 является повышение надежности работы устройства эа счет выявления недопустимых результатов вычисления, Устройство содержит группу входов аргументов 1, сдвиговый регистр 2, блок памяти констант 3, регистр команд 4, блок управления 5, регистр б, снетчик 7. На группу входов аргументов 1 подаются значения входных переменных, которые под управлением сигналов с выходов блока управления 5 последовательно обрабатываются в устройстве, Если в результате вычисления возникает сбой, устройство инициирует повторное вычисление, если устройством фиксируется несколько повторных сбоев (от- ,каз), на выходе устройства формируется сигнал ошибки. 3 ил., 2 табл.Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления систем булевых функций.Цель изобретения - повышение надеж.ности работы устройства за счет выявления недопустимых результатов вычисления.На фиг. 1 приведена структурная 10схема устройства для вычисления булевых функций, на фиг. 2 - алгоритмработы устройства, на фиг. 3 - графсхема вычисления системы булевыхФункций. 15Устройство содержит группу входов1 аргументов, сдвиговый регистр 2,блок 3 памяти констант, регистр 4команд, блок 5 управления, регистр 6,счетчик 7, выход 8 .:эизнака началь Оной установки адреса блока 5 управления, группу информационных выходов9, вход 10 управления записью сдвигового регистра 2, вход 11 управлениясдвигом сдвигового регистра 2, два 25выхода 12 и 13 управления записьюблока 5 управления, выход 14 признака обнуления счетчика блока 5 управления, выход 15 признака увеличениясчета блока 5 управления, выход 16 ЗОпризнака готовности блока 5 управления, вход 17 запуска, два входа18 и 19 управления переходом блока5 управления, вход 20 признака отказа блока 5 управления и выход 21признака ошибки.Алгоритм работы устройства содержит следующие обознач"ния микроопераций: А 1 - обнуление счетчика7; А 2 - запись в сдвиговый регистр 4 О2; запись в регистр 6, АЗ - записьв регистр 4 команд, А 4 - запись врегистр 6 и сдвиг информации в сдвиговом регистре 2; А 5 " установкапризнака готовности на выходе 16; 45Аб - увеличение на единицу содержимого счетчика 7; Р 1 Р 2 - содержимое двух старших разрядов регистра4 команд, РЗ - признак переполнениясчетчика 7,50Устройство работает следующим образом.В исходном состоянии на входы ар"гументов 1 поданы значения входныхпеременных. После подачи сигналазапуска на вход 17 в соответствиис алгоритмом (Фиг.2) блок 5 управления устанавливает в начальное состояние счетчик 7 и регистр 6, обес печивает запись в сдвиговый регистр2 и сбрасывает сигнал готовностирезультата на выходе 16. Далее выполняется запись команды в регистр4 команд. Если это команда перехода к анализу следующей переменной(Р 1 Р 2 = 01), производится сдвиг информации в сдвиговом регистре 2 изаписывается информация для формирования адреса следующей команды врегистр 6. При условии Р 1 Р 2 =11 устанавливается признак готовностирезультата. Если Р 1 Р 2 = 00, то записанная команда указывает на ошибочный результат (либо имеет местонедопустимая комбинация входных переменных, либо неправильно сформирована последовательность переходовмежду ячейками памяти блока управления 5), В этом случае значение счетчика 7 увеличивается на единицу иинициируется повторное вычисление.Если счетчик 7 переполнен, считается, что имеет место устойчивый сбой(отказ), на выходе 21 формируетсясигнал ошибки, признак готовностирезультата отсутствует, блок 5 управления переходит в заключительноесостояние. Таблица 1 Х Х Х У Уд О 1 0 1 1 0 0 1 Возникновение любого другого набора считается ошибкой. Содержимое блока памяти констант 3 задается табл.2, где символомобозначены безразличные значения в ячейках памяти. Предполагается, что обработка переменных осуществляется по одному биту. Значения признаков Р 1 Р 2 записаны в разрядах 1 и 2, значения результата У, У - в разрядах 4 и 5. Начальное состояние регистра 6.- нулевое. Граф-схема (Фиг.З) задает вычисление системы булевых функций У,. Уот трех переменных Х, Х, Х, )Предполагается, что система булевых функций частичная и определена сог-. ласно табл,1.1631537 Тч блицч 2 Содержимое ячеек Адерсячейки 1 2 3 4 5 1 2 3 4 5 1 1 0 1 8 9 10 11 12 13 14 15 0 1 0 0 1 О 1 0 1 0 0 1 0 1 1 0 1 0 1 1 0 1 1 0 0 0 01 1 - 1 1 О 0 О 1 2 3 5 6 7 0 0 Пусть в результате сбоя имеет место комбинация Х = О, Х = 1, Х = 1. Тогда переход между ячейками с адресами О, 3, 7 завершается увеличением на единицу счетчика 7 и повторным счетом.В случае возникновения, например, константой неисправности типа "0" в 5-м разряде осуществляется переход между ячейками О, 1, 5 и данная неисправность обнаруживается. Формула изобретения Устройство для вычисления систем булевых функций, содержащее сдвиговый регистр, блок памяти констант, регистр команд, блок управления, регистр и счетчик, вход обнуления которого соединен с выходом признака обнуления счетчика, блока управления, первый выход. управления записью которого соединен с входом разрешения записи регистра команд, информационный вход которого соединен с выходом блока памяти констант, старшие адресные входы которого соединены с выходом регистра,вход разрешения записи и вход обнуления которого соединены соответственно с вторым выходом управления записью блока управления и выходом признака начальной установки адреса блока управления, вход запуска устАдрес Содержимое ячеек ячейки ройства соединен с входом разрешения запуска блока управления, выход признака готовности которогосоединен с выходом признака готов ности устройства, входы аргументовгруппы соединены с информационными, разрешения записи которого соединенс выходом признака начальной установ ки адреса блока управления, о тл и ч а ю щ е е с я тем, что, сцелью повышения надежности работыустройства за счет выявления недопустимых результатов вычисления, выход признака увеличения счета блока.управления соединен со счетным входомсчетчика, выход признака переполнения которого соединен с входом признака отказа блока управления и выходом признака ошибки устройства, информационные выходы группы которогосоединены с выходами разрядов, кромедвух старших, регистра команд и информационными входами регистра, выходы первого и второго старших разрядов регистра команд соединены соот"ветственно с первым и вторым входомуправления переходом блока угравления, мпадшие адресные входы блокапамяти констант соединены с выходомсдвигового регистра, вход разрешениясдвига которого соединен с вторым вы"ходом управления записью блока управления.1631537 А.Осауленко Редактор Л.Пчолйнска 388 Подписноео изобретениям и открьггиям при ГКНТ ССС 35, Раушская наб., д, 4/5 водственно-издательский комбинат "Патент", г. Ужгор Гагарина, 101 Заказ 547ВНИИПИ Госу Составит Техре

СмотретьЗаявка

4618947, 12.12.1988

ФИЛИАЛ "ВОСХОД" МОСКОВСКОГО АВИАЦИОННОГО ИНСТИТУТА ИМ. СЕРГО ОРДЖОНИКИДЗЕ

БЕЛЯКОВ СТАНИСЛАВ ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: булевых, вычисления, систем, функций

Опубликовано: 28.02.1991

Код ссылки

<a href="https://patents.su/4-1631537-ustrojjstvo-dlya-vychisleniya-sistem-bulevykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления систем булевых функций</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Устройство для выбора экстремального из -разрядных двоичных чисел

Случайный патент: Гидроциклон