Устройство для исправления модульных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

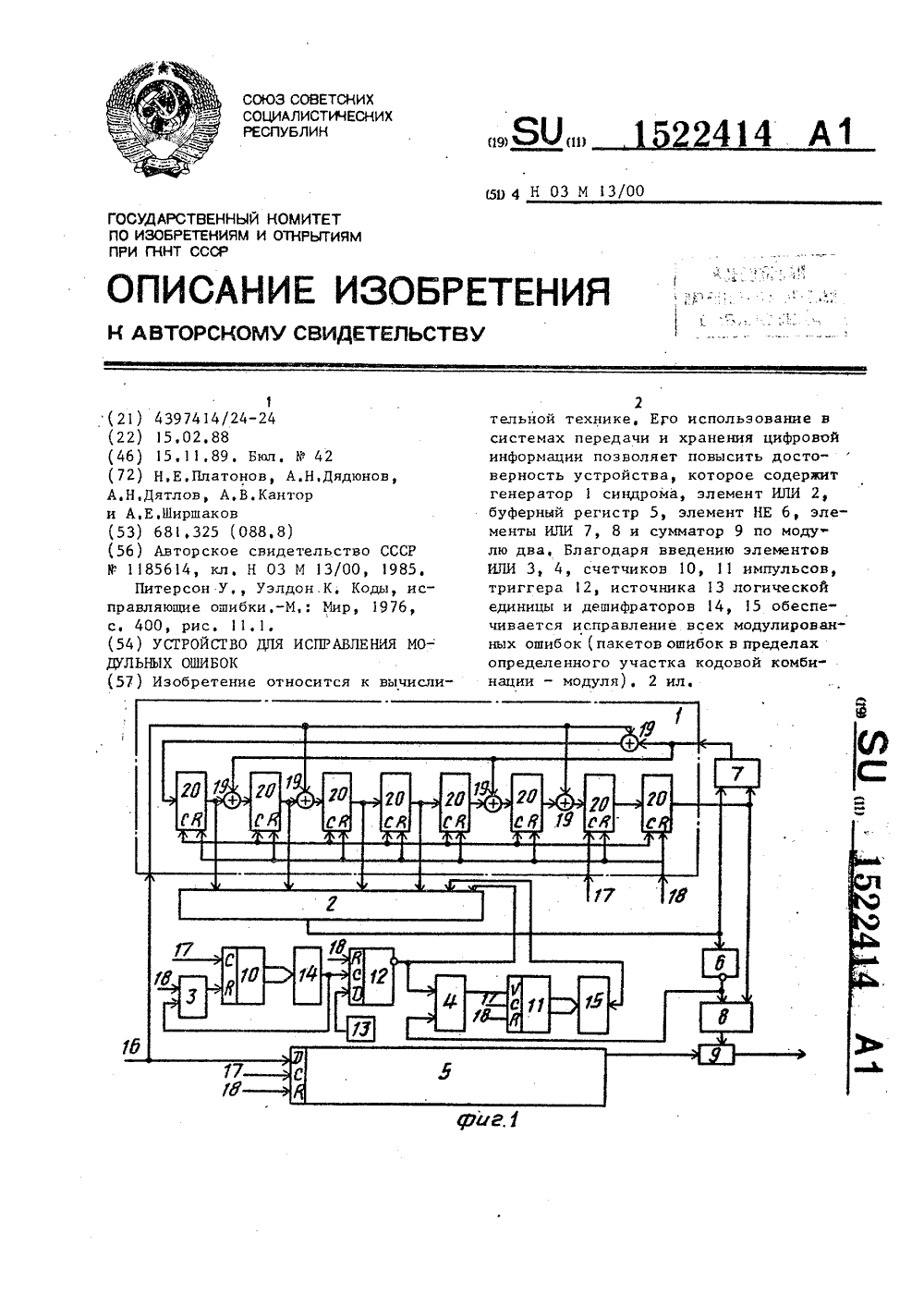

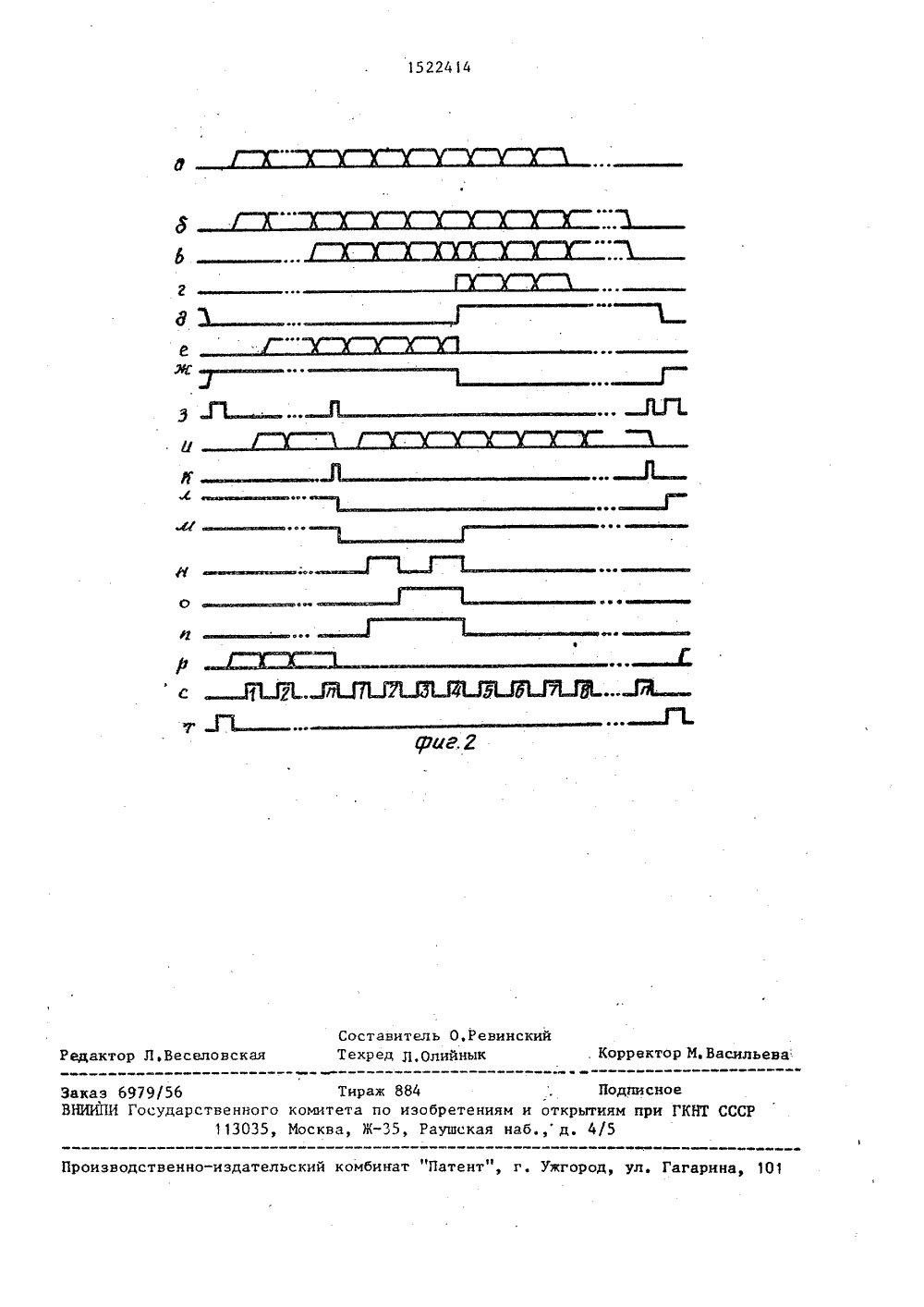

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИРЕСПУБЛИК 19) 11 224 ЗМ 130 ИСА ОБР ЕНИЯ У 42:Ь ОСУДАРСТВЕННЫЙ КОМИТЕПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР А ВТОРСНОМУ СВИДЕТЕЛЬСТ(54) УСТРОЙСТВО ДЛЯДУЛЬНЫХ ОШИБОК(57) Изобретение относит 2тельной технике, Его использование в системах передачи и хранения цифровой информации позволяет повысить достоверность устройства, которое содержит генератор 1 синдрома, элемент ИЛИ 2, буферный регистр 5, элемент НЕ 6, элементы ИЛИ 7, 8 и сумматор 9 по моду лю два, Благодаря введению элементов ИЛИ 3, 4, счетчиков 10, 11 импульсов, триггера 12, источника 13 логической единицы и дешифраторов 14, 15 обеспечивается исправление всех модулированных ошибок (пакетов ошибок в пределах определенного участка кодовой комбинации - модуля), 2 ил.Изобретение относится к вычисли.тельной технике в . может быть использовано в системах передачи и храненияцифровой информации.Цель изобретения - повышение достоверности,На фиг. 1 представлена функциональная схема устройства; на фиг, 2 - временные диаграммы его работы,ОУстройство содержит генератор 1синдрома, первый-третий элементы ИЛИ2-4, буферный регистр 5, элемент НЕ6, первый и второй элементы И 7 и 8,сумматор 9 по модулю два,. первый 10и второй 1 1 счетчики импульсов, триггер 12, источник 13 логической единицы, первый 14 и второй 5 дешифраторы,На фиг. 1 обозначена информационный16 и тактовый. 17 входы и вход 18 начальной установки,Генератор 1 синдрома выполнен насумматорах 19 по модулю два и регистре сдвига с ячейками 20,На фиг. 2 обозначены следующие сиг налы;а - смена информации в, регистре20 сдвига генератора 1;б - смена информации на выходе регистра 5;ЗОв - смена информации на выходе сумматора 9;г -,смена информации на выходе элемента 8;д - сигнал на выходе элемента НЕ б;3е - смена информации на выходе элемента 7;ж - сигнал на выходе элементаИЛИ 2;з - сигнал на выходе элементаИЛИ 3;и - смена информации на выходахсчетчика 10;к - сигнал на выходе дешифратора 14;л - сигнал на инверсном выходе триггера 12;, м - сигнал на выходе элемента ИЛИ 4;н, о - сигналы на выходаХ первогои второго разрядов счетчика 11;п - сигнал на выходе дешифратора 15;р - смена информации на входе 16;с - тактовые импульсы на входе 17;т - импульсы обнуления на входе 18,50На фиг, 1 и 2 приведен пример конкретной реализации генератора 1 синдрома с г=8 ячейками 20 для укороченного кода (24, 1 б), порождаемого полиномом д(х) =х+х+х+1. Этот код исправляет модульные ошибки с длиной пакета Ь 4 (модульными называются пакеты ошибок, возникающие в границах оп 1 ределенного участка кодовой комбинации - модуля), Выходы г-Ь=4 младших ячеек 20 генератора. 1 соединены с элементом ИЛИ 2,Устройство дпя исправления модульных ошибок работает следующим образом.В начальный момент времени передпоступлением кодовой комбинации ( слова) по входу 18 начальной установки,приходит импульс, который устанавливает в нулевое состояние генератор 1 синдрома, буферный регистр 5, счетчик 1 О и 11, триггер 12. После этогона информационном входе 16 в последовательном коде выставляется кодовоеслово, тактируемое задним Фронтом тактовых импульсов, поступающих на тактовый выход 17. По переднему фронтутактовых импульсов кодовое слово записывается в буферный регистр 5 и преобразуется в генераторе 1 синдрома,За первые и тактов, где и - количество символов в слове, в генераторе 1формируется синдром ошибки, а кодовое слово полностью записывается в буферный регистр 5, В это же времяпервый счетчик 10 меняет свОе состояние под действием заднего фронта тактовых импульсов, После поступления и тактовых импульсов срабатывает первый дешифратор 14, на выходе которого появляется единичный импульс, который через второй элемент ИЛИ 3 обнуляет счетчик 10 и переводит триггер 12 в единичное состояние, что означает конец фазы формирования синдрома и начало фазы исправления ошибок,В фазе формирования синдрома единичный потенциал с инверсного выхода триггера 12 через третий элементИЛИ 14 запрещает работу второго счетчика 11.В Фазе исправления ошибок запретна работу счетчика 11 снят, и последний меняет свое состояние под действием заднего фронта тактовых импульсов,Второй дешифратор 15 анализирует состояние счетчика 11, на его выходе появляется нулевой потенциап через каждые Ь тактовых импульсов, гдеЬ - длина модуля (на фиг, 2 н-и в качестве необязательного приема приведена работа счетчика 11 и дешифратора 15 дпя случая Ь=4). В это же время в фазе исправления ошибок по переднему Фронту тактовых импульсов5 152241 происходит синхронный сдвиг информации в генераторе 1 синдрома и ,.в буферном регистре 5. Сдвиг информации в генераторе 1 происходит циклически с обратной связью, замкну 5 той через первый элемент И 7. Информация из буферного регистра 5 поступает через: сумматор 9 по модулю два на выход устройства, 10На каждом такте сдвига первый элемент ИЛИ 2 анализирует состояние выходов г-Ь младших ячеек генератора 1 синдрома на напичие .нулевой комбинации, Наличие нулевой комбинации в этих ячейках означает, что на выходе остальных ячеек генератора 1 присутствует комбинация ошибок, т,е, единица находится в тех ячейках, положение которых по отношению к симво лам кодового слова, находящимся в данный момент в Ь старших разрядах буферного регистра 5, совпадает сположением ошибочных символов, При этом вследствие совпадения с нулевым 25 потенциалом на выходе второго дешифратора 15, что означает признак начала исправления модульной ошибки, на выходе элемента ИЛИ 2 формируется нулевой потенциал, который, поступив на вход первого элемента И 7, размыкает обратную связь в генераторе 1, Этот же сигнал, инвертированный элементом НЕ 6, поступает через третий элемент ИЛИ 4 на управляющий вход счетчика 11 и запрещает его дальней 35 шую работу, Сигналы на выходах счетчика 11 при этом больше не меняются, обеспечивая постоянное наличие нуля на выходе дешифратора 15. Единичный 40 потенциал а выхода элемента НЕ 6 разрешает прохождение сигнала с выхода последней ячейки генератора 1 синдарома Ьа второй вход сумматора 9. по .модулю два, на первый вход которого при этом поступает сигнал с выхода старшего разряда буферного регистра 5,Таким образом, исправляются все модульные ошибки в кодовом слове, Через)О и тактов в фазе исправления ошибок все кодовое слово будет считано из буферного регистра 5 и поступит на выход устройства, После этого вновь срабатывает первый дешифратор 14, который35 устанавливает счетчик 10 в исходное состояние, С приходом нового импульса 4 6начальной установки и нового кодового слова работа устройства повторяется,Формула из обретенияУстройство для исправления модульных ошибок, содержащее буферный регистр, информационный и тактовый входы и вход начальной установки которого объединены с одноименными входами генератора синдрома и являются одноименными входами устройства, первый выход генератора синдрома соединен с первыми входами первого и второго элементов И, вторые выходы генератора синдрома подключены к первым входам первого элемента ИЛИ, выход которого непосредственно и через элемент НЕ соединен с вторыми входами соответственно первого и второго элементов,И, выходы которых и выход буферного регистра подключены соответственно к входу обратной связи генератора синдрома и первому и второму входам. сумматора по модулю два, выход которого является выходом устройства, о т л и ч а ю щ ее с я тем, что, с целью повьппения достоверности устройства, в него введены первый и второй счетчики импульсов, первый и второй дешифраторы, триггер, второй и третий элементы ИЛИ и источник логической единицы, выход которого соединен с информационным входом триггера, вход обнуления кото- рого объединен с входом обнуления второго счетчика импульсов и первым входом второго элемента Ю 1 И и подключен к входу начальной установки устройства, счетные входы счетчиков им-; пульсов объединены и подключены к тактовому входу устройства, выход второго элемента ИЛИ соединен с входом обнуления первого счетчика, выходы которого подключены к входам первого дешифратора, выход которого соепинен с вторым входом второго элемента ИЛИ и тактовым входом триггера, инверсный выход которого подключен к второму входу первого и первому входу третьего элементов ИЛИ, второй вход и выход третьего элемента И 1 И подключены соответственно к выходу элемента НЕ и входу запрета работы второго счетчика импульсов, выходы которого соедЬиены с входами второго дешифратора, выход которого подключен к третьему входу первого элемента ИЛИ,1522414 Фь и Составитель О.РевинскииВеселовская Техред д,ОлийныкЮЕ а рректор И,льева акт 979/56 Госуда Зак венно 11303 ственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 101 Тираж 884 комитета по изобрете Москва, Ж, Раушск Подписноем и открытиям при ГКНТ СССнаб., д. 4/5

СмотретьЗаявка

4397414, 15.02.1988

ПРЕДПРИЯТИЕ ПЯ А-7544

ПЛАТОНОВ НИКОЛАЙ ЕВГЕНЬЕВИЧ, ДЯДЮНОВ АЛЕКСАНДР НИКОЛАЕВИЧ, ДЯТЛОВ АЛЕКСАНДР НИКОЛАЕВИЧ, КАНТОР АЛЕКСАНДР ВАСИЛЬЕВИЧ, ШИРШАКОВ АЛЕКСАНДР ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: H03M 13/05

Метки: исправления, модульных, ошибок

Опубликовано: 15.11.1989

Код ссылки

<a href="https://patents.su/4-1522414-ustrojjstvo-dlya-ispravleniya-modulnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления модульных ошибок</a>

Предыдущий патент: Устройство декодирования бчх-кодов с частичным исправлением ошибок

Следующий патент: Декодирующее устройство

Случайный патент: Нагружающее устройство велотренажера