Дельта-декодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

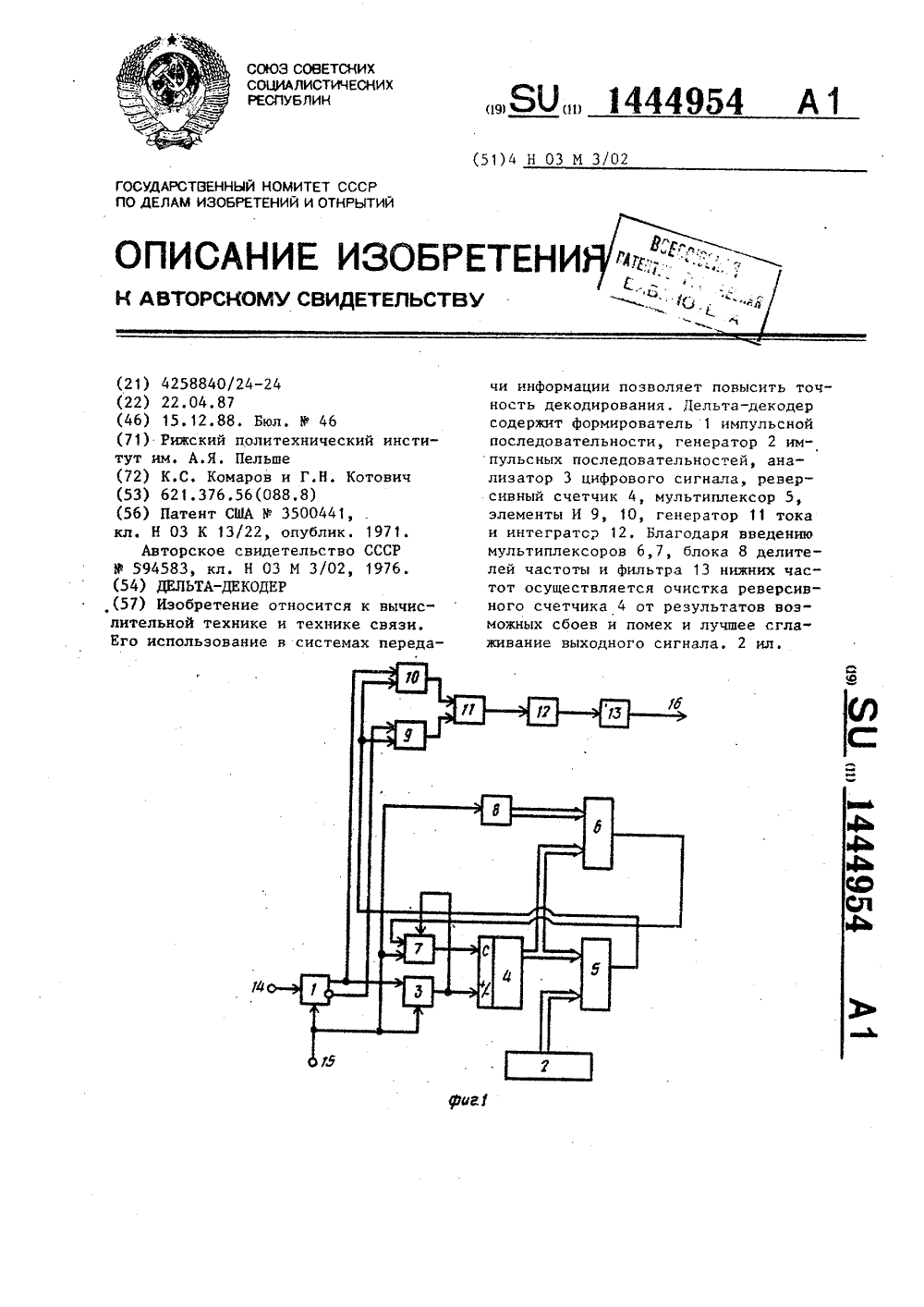

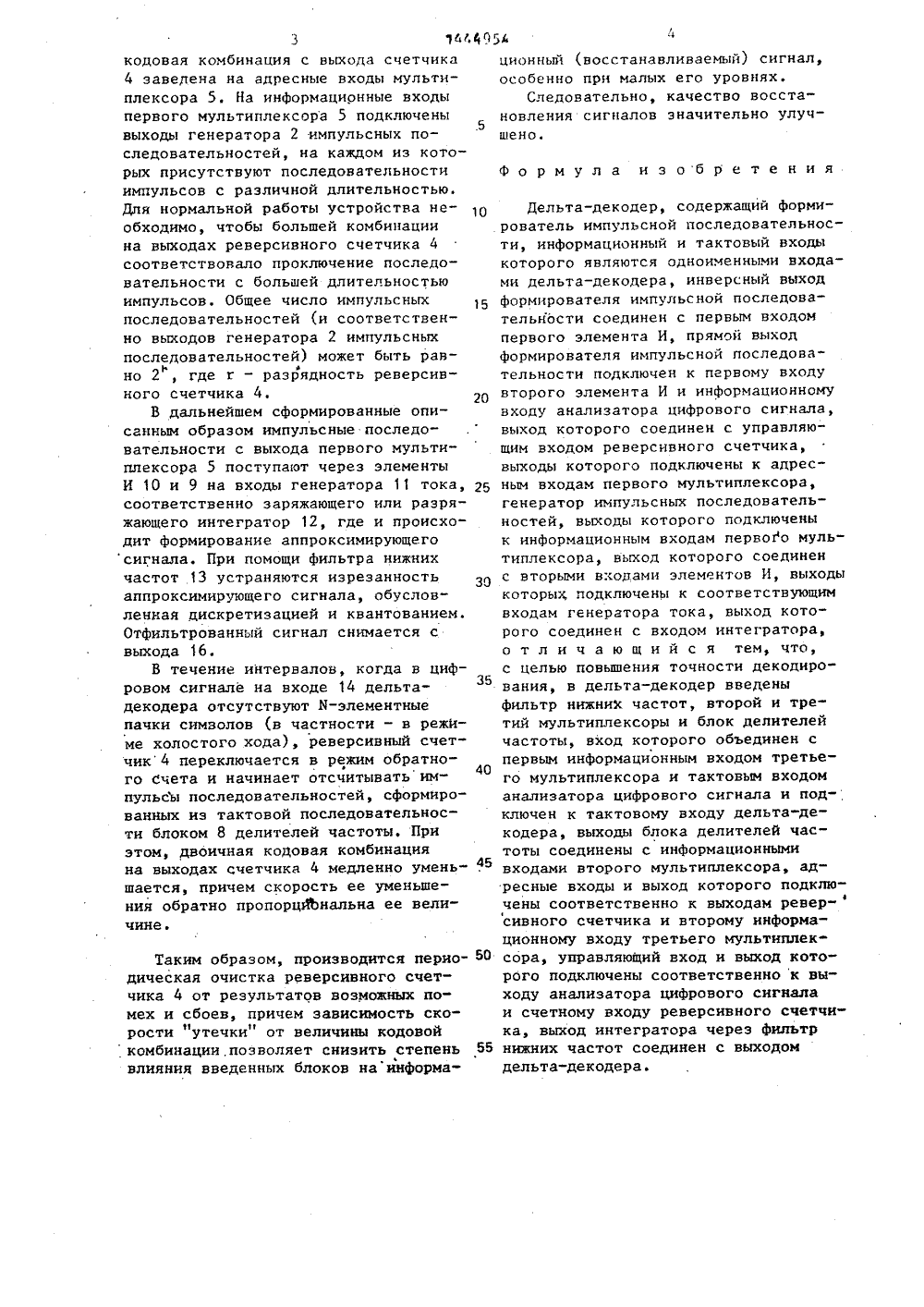

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 119) И 1) 4 9 51)4 Н 03 М НИЕ ИЗОБРЕТЕНМУ СВИДЕТЕЛЬСТВУ ВТОРСКО инстиви 1971 СССР 1976 к вычисого сигнала. 2 ил. живание в передаГОСУДАРСТНЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ,(57) Изобретение относитсялительной технике и техникеЕго использование в система чи информации позволяет повысить точность декодирования, Дельта-декодерсодержит формирователь 1 импульснойпоследовательности, генератор 2 импульсных последовательностей, анализатор 3 цифрового сигнала, реверсивный счетчик 4, мультиплексор 5,элементы И 9, 10, генератор 11 токаи интегратор 12. Благодаря введениюмультиплексоров 6,7, блока 8 делителей частоты и фильтра 13 нижних частот осуществляется очистка реверсивного счетчика 4 от результатов возможных сбоев и помех и лучшее сглаИзобретение относится к вычислительной технике и технике связи и может быть использовано в системах передачи информации, например, в электронных и квазиэлектронных АТС.Цель изобретения " повышение .точности декодирования.На Фиг. 1 изображена функциональная схема дельта-декодера на фиг,2 - 10 временные диаграммы работы анализатора цифровых сигналов.Дельта-декодер содержит формирователь 1 импульсной последовательнос" ти, генератор 2 импульсных последо вательностей, анализатор 3 цифрового сигнала, реверсивный счетчик 4, первый -третий мультиплексоры 5-7, блок 8 делителей частоты, первый и второй элементы И 9 и 10, генератор 2 О 11 тока, интегратор 12 и фильтр нижних частот (ФНЧ) 13. На фиг. 1 обо. значены информационный и тактовый входы 14 и 15 и выход 16.Дельта-декодер работает следующим 25 образом.Цифровой дельта-модулированный (ДМ) сигнал со входа 14 поступает на вход Формирователя 1, имеющего два выхода, первый из которых прямой, 30 а второй инверсный. Алгоритм работы формирователя 1 заключается в формировании из входного ДМ сигнала прямого и инверсного импульсных потоков, Со стандартной высотой импульсов и заданной крутизной фронтов, синхрон 35 ных относительно импульсов тактовой последовательности Г присутствующих на тактовом входе 15 (фиг. 2 а).фЦифровой сигнал с первого выхода формирователя 1 поступает на информационный вход анализатора 3, алгоритмкоторого иллюстрируется временнымидиаграммами на фиг. 2,. В случае, когда подряд следующих символов анализируемого анализатором 3 цифровогосигнала одинаковы (фиг. 2 б), на выходе анализатора 3 появляется единич"ный логический потенциал (фиг, 2 в),который, поступив на управляющий входреверсивного счетчика 4, устанавливает его в режим прямого счета. Вслучае, когда фрагмент цифровогосигнала, охватываемый анализатором3, не содержит Я-элементных пачек,на выходе анализатора 3 формируется 55потенциал логического нуля, который,поступив на управляющий вход реверсивного счетчика 4, переключает его в режим обратного счета. Одновременно при помощи третьего мультиплексора 7 производится коммутация сигналов, поступающих на счетный вход реверсивного счетчика 4 Логическая "1" с выхода анализатора 3 поступает на управляющий вход муль- типлексора 7, в результате чего,импульсы тактовой последовательности Г с тактового входа 15 коммутируются мультиплексором 7 на счетный вход реверсивного счетчика 4В случае, когда на выходе анализатора 3 присутствует логический "0", на счетный вход реверсивного счетчика 4 череземультиплексор 7 проключается выходной сигнал второго мультиплексора б.На вход блока 8 делителей частоты поступают импульсы тактовой последовательности Г с тактового входа 15. На каждом выходе блока 8 делителей частоты присутствуют периодичес" кие последовательности импульсов, сфбрмированные из тактовой последо- . вательности методом деления ее частоты Г на различные постоянные коэфФициенты,. (В простейшем случае в качестве блока 8 делителей частоты может быть использована так называемая "линейка триггеров", т,е. несколько соединенных последовательно Т-триггеров). На выход второго мультиплексо" ра 6 проключается импульсная последовательность с щного из выходов блока 8 делителей частоты, в зависимости от кодовой комбинации на адресных входах второго мультиплексора 6, определяемой, в свою очередь, состоянием реверсивного счетчика 4.Для нормальной работы устройства необходимо, чтобы большейкодовой комбинацией на выходе реверсивного счетчика 4 (и соответственно на адресных входах второго мультиплексора 6) на выход второго мультиплексора 6 проключалась импульсная последовательность с большей тактовой частотой.Таким образом, в случае, когда цифровой ДМ-сигнал на входе 14 дельта-декодера содержит И-элементные пачки однотипных символом, счетчик 4, работающий в режиме прямого счета, отсчитывает импульсы тактовой последовательности Г , в результате чего двоичная кодовая комбинация на его выходах увеличивается, С изменением двоичного числа на выходах реверсивного счетчика 4 изменяется и последовательность импульсов на выходе первого мультиплексора 5, так как3 14449кодовая комбинация с выхода счетчика4 заведена на адресные входы мультиплексора 5, На информационные входы первого мультиплексора 5 подключены выходы генератора 2 импульсных последовательностей, на каждом из которых присутствуют последовательности импульсов с различной длительностью,гд/ционньп (восстанавливаемый) сигнал, особенно при малых его уровнях.Следовательно, качество восстановления сигналов значительно улучшено. Формула изобретенияДля нормальной работы устройства необходимо, чтобы большей комбинации на выходах реверсивного счетчика 4 соответствовало проключение последовательности с большей длительностью импульсов. Общее число импульсных последовательностей (и соответственно выходов генератора 2 импульсных последовательностей) может быть равно 2 , где г - разрядность реверсивного счетчика 4.В дальнейшем сформированные описанным образом импульсные последовательности с выхода первого мультиплексора 5 поступают через элементыИ 10 и 9 на входы генератора 11 тока,соответственно заряжающего или разряжающего интегратор 12, где и происходит формирование аппроксимирующего сигнала. При помощи фильтра нижних частот 13 устраняются изрезанность аппроксимирующего сигнала, обусловленная цискретизацией и квантованием. Отфильтрованный сигнал снимается с выхода 16.В течение интервалов, когда в цифровом сигнале на входе 14 дельта- декодера отсутствуют Я-элементные пачки символов (в частности - в режйме холостого хода), реверсивный счетчик 4 переключается в режим обратного счета и начинает отсчитывать импульсы последовательностей, сформированных из тактовой последовательности блоком 8 делителей частоты, При этом, двоичная кодовая комбинация на выходах счетчика 4 медленно уменьшается, причем скорость ее уменьшения обратно пропорцйЬналька ее величине. Таким образом, производится периодическая очистка реверсивного счетчика 4 от результатов возможных помех и сбоев, причем зависимость скорости "утечки" от величины кодовой комбинации, позволяет снизить степень влияния введенных блоков наикформа 10 15 20 25 30 35 40 45 50 Дельта-декодер, содержащий формирователь импульсной последовательности, информационный и тактовый входы которого являются одноименными входами дельта-декодера, инверсный выход формирователя импульсной последовательности соединен с первым входом первого элемента И, прямой выход формирователя импульсной последовательности подключен к первому входу второго элемента И и информационному входу анализатора цифрового сигнала, выход которого соединен с управляющим входом реверсивного счетчика, выходы которого подключены к адресным входам первого мультиплексора, генератор импульсных последовательностей, выходы которого подключены к информационным входам первого мультиплексора, выход которого соединен с вторыми входами элементов И, выходы которыми подключены к соответствующим входам генератора тока, выход которого соединен с входом интегратора, о т л и ч а ю щ и й с я тем, что, с целью повышения точности декодирования, в дельта-декодер введены фильтр нижним частот, второй и третий мультиплексоры и блок делителей частоты, вход которого обьединен с первым информационным входом третьего мультиплексора и тактовым входом анализатора цифрового сигнала и подключен к тактовому входу дельта-декодера, выходы блока делителей частоты соединены с информационными входами второго мультиплексора, адресные входы и выход которого подключены соответственно к выходам ревер-сивного счетчика и второму информационному входу третьего мультиплексора, управляющий вход и выход которого подключены соответственно к выходу анализатора цифрового сигнала и счетному входу реверсивного счетчика, выход интегратора через фильтр нижних частот соединен с выходом дельта-декодера.1444954 Редактор И.Сегляник Заказ 6515/57 Тираз 929 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж Раушская наб., д. 4/5

СмотретьЗаявка

4258840, 22.04.1987

РИЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

КОМАРОВ КОНСТАНТИН СЕРГЕЕВИЧ, КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-декодер

Опубликовано: 15.12.1988

Код ссылки

<a href="https://patents.su/4-1444954-delta-dekoder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-декодер</a>

Предыдущий патент: Дельта-модулятор

Следующий патент: Устройство для приема информации

Случайный патент: Навивочное устройство для химических волокон