Устройство для моделирования упругого гистерезиса

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

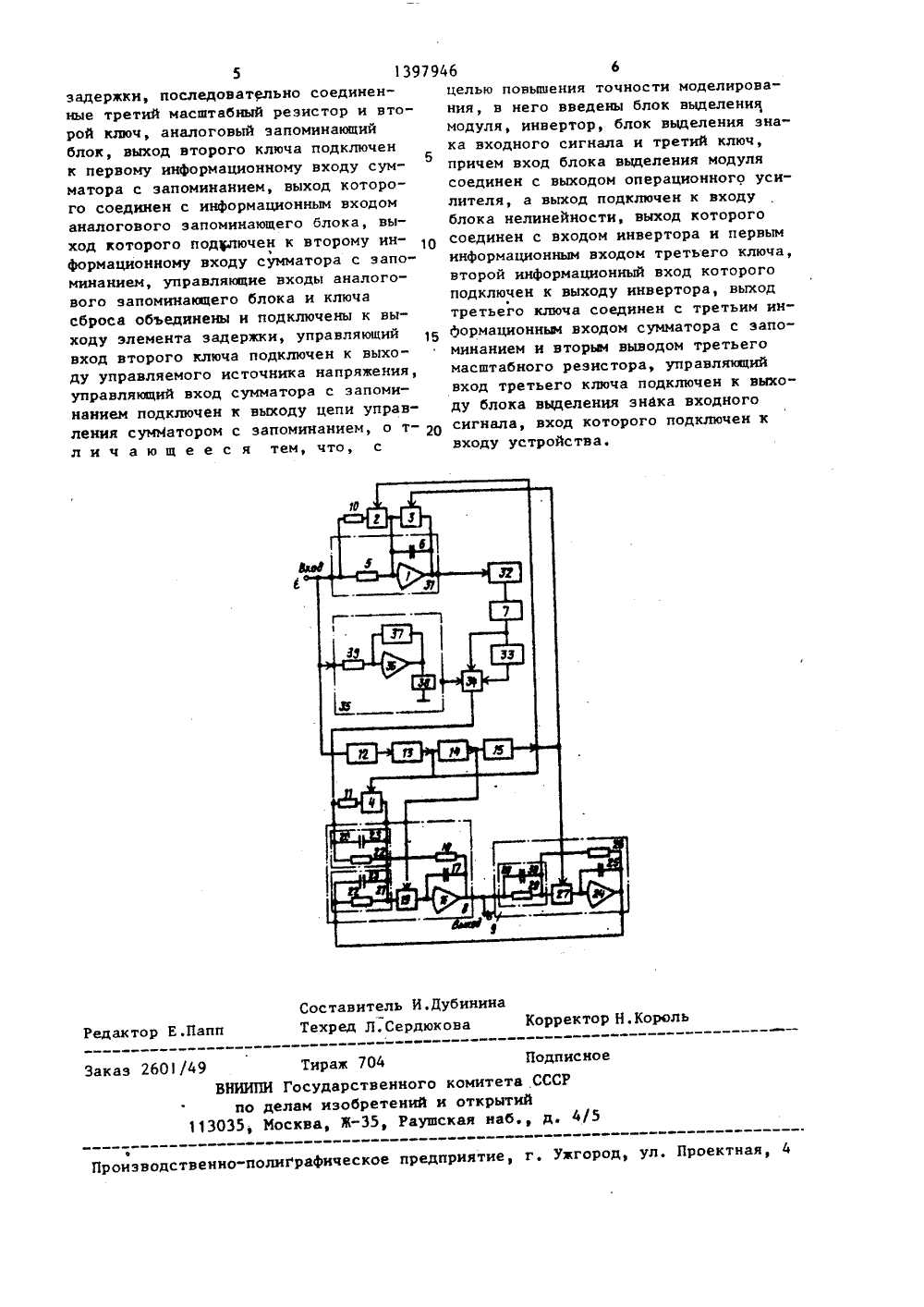

/48 ОПИСАНИЕ ИЗОБРЕТЕНИ ОДЕЛИРОВ алого- нэободелири цикГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ АВТОРСКОМУ СВИДЕТЕЛЬСТ(46) 23,05.88. Бюл. У 19 (71) Куйбышевский авиационный институт им. акад. С.П.Королева (72) В.А,Вьниканин, Е.И.Давыдов и А.К.Мартынов(56) Авторское свидетельство СССР В 860091, кл. С 06 С 7/48, 1979,Авторское свидетельство СССР У 966708, кл. С 06 С 7/48, 1980,(54) УСТРОЙСТВО ДЛЯ М)ПРУГОГО ГИСТЕРЕЗИСА (57) Изобретение относится квой вычислительной технике, цретения - повышение точностировання упругого гистереэиса лических деформациях за счет устранения неидентичности воспроизведениянисходящей и восходящей ветвей петлигистереэиса. Для этого в устройстводополнительно введены блок выделениямодуля, инвертор, блок выделения знака входного сигнала и ключ. Введениеблока .выделения модуля позволяет настраивать блок нелинейности толькона воспроизведение положительной ветви экспериментальной функции. В зависимости от знака входного сигналанапряжение с выхода блока нелинейности с помощью ключа подается на входсумматора с запоминанием либо со своим знаком, либо через инвертор с противоположным знаком. Управление рабо- Йтой ключа осуществляется от блока вы- ррделения знака входного сигнала. 1 нл. ф ф(С) + 2 й(1/2Е ) з 18 п Е,Изобретение относится к аналоговой вычислительной технике.Цель изобретения - повышение точности моделирования.На чертеже представлена функциональная схема устройства для моделирования упругого гистерезиса.Устройство содержит операционный усилитель (ОУ) 1, первый ключ 2,1ключ 3 сброса, второй ключ 4, первый масштабный резистор 5, интегрирующий конденсатор 6, блок 7 нелинейности, сумматор 8 с запоминанием, аналоговый запоминающий блок 9, второй и третий масштабные резисторы 10 и 11, блок 12 фиксации нуля, управляемый источник 13 напряжения, цепь 14 управления сумматором с запоминанием, элемент 15 задержки.Сумматор 8 с запоминанием содержит ОУ 16, конденсатор 17, масштабгде Е - модуль приращения деформации конструкции.Весь процесс моделирования петли гистерезиса состоит из трех основных этапов: моделирование начального участка петли, моделирование нисходящей ветви, моделирование восходящей ветви. 35Устройство работает следующим образом.Исходное состояние схемы устройства соответствует этапу моделирования начального участка петли. 40В исходном положении ключи 2,3 и 27 разомкнуты, а ключи 4 и 19 замкнуты. При этом коэффициент передачи интегратора 31 и коэффициент передачи по первому входу сумматора 8 с запо минанием равны единице. Напряжение на выходе ОУ 36 блока 35 вьщеления знака входного сигнала равно нулю и реле 38 обесточено, а его контакты (ключ 34) нормально замкнуты. Настройка элемента 37 ограничения в цепи обратной связи ОУ 36 обеспечивает появление напряжения на выходе усилителя только при отрицательном входном сигнале. 55Напряжение, пропорциональное скорости деформации Е, поступает на вход ОУ 1 через масштабный резистор 5 в блок 12 фиксации нуля и в блок ный резистор 18, ключ 19, два форсирующих звена 20 и 21, каждое из которых содержит параллельно включенныерезистор 22 и конденсатор 23. Аналоговый запоминающий блок 9 содержитОУ 24, конденсатор 25, масштабный резистор 26, ключ 27, форсирующее звено 28, состоящее из параллельно соединенных резистора 29 и конденсатора30. Элементы 1,5 и 6 представляют собой интегратор 31, Кроме того, устройство содержит блок 32 вьщелениямодуля, инвертор 33, ключ 34 и блок35 вьщеления знака входного сигнала,состоящий из ОУ 36, элемейта 37 ограничения, реле 38 и масштабного резистора 39,Устройство реализует аналоговуюмодель упругого гистерезиса в виде 35 вьщеления знака входного сигнала. Напряжение, отражающее изменение деформации, с выхода интегратора 31 поступает в блок 32 вьщеления модуля, с выхода которого модуль приращения деформации Е подается на вход блока 7 нелинейности. Блок нелинейности настраивается на воспроизведение только положительной ветви функции Г(Е). С выхода блока нелинейности снимается напряжение, пропорциональное 1(Е) . Это напряжение всегда будет положительным. Так как начальный участок воспроизводится при ЕО, напряжение с выхода блока 7 нелинейности, знак которого совпадает со знаком входного сигнала, через нормально замкнутый ключ 34 поступает на первый информационный вход сумматора 8 с запоминанием. На третий вход сумматора 8 подается напряжение с выхода блока 9. В начальный момент времени на выходе аналогового запоминающего блока 9 напряжение равно нулю, поэтому выходное напряжение сумматора пропорционально значению функции Е(Е ). Первый этап моделирования заканчивается в момент С, когда Е= О.Для перехода от моделирования начального участка петли к моделированию нисходящей ветви необходимо всумматор 8 переводится в режим запоминания сигнала, который находился 10 3 139794определенной последовательности с помощью цепей управления произвести переключения в схеме устройства.В момент 1 = 1 ло сигналу цепи15 14 управления сумматором ключ 19 размыкается, При этом вход ОУ 16 сумматора с запоминанием отключается отего входных цепей, в результате чего 6 4ления знака входного сигнала появляется напряжение, которым залитывается реле 38. Контакты реле 38 (ключ 34) размыкаются. При этом первый информа-,ционный вход сумматора 8 подключается к выходу инвертора 33, назначениекоторого изменять знак сигнала, поступающего с выхода блока 7 нелинейности.Этап моделирования нисходящей ветна выходе усилителя по окончанию предыдущего этапа моделирования. По сигналу с выхода элемента 15 задержкизамыкается ключ 3, и напряжение навыходе интегратора 31 становится равным нулю. Одновременно замыкаетсяключ 27. При этом вход ОУ 24 соединяется с его выходной цепью, превращаяблок 9 в масштабное звено. На выходеОУ 24 появляется напряжение, равноенапряжению на выходе ОУ 16, Одновременно с этими переключениями происходит перестройка входных цепей интегратора 31 и сумматора 8 с запоминанием. По сигналу от управляемого источника 13 напряжения ключ 2 переключает коэффициент передачи интегратора 31, устанавливая его равным 1/2,а ключ 4 устанавливает коэффициентпередачи по первому входу сумматора8 с запоминанием, равным двум. Этиновые значения коэффициентов передаМи сохраняются в течение. всех последующих этапов моделирования, Синхронизация работы всех цепей управленияосуществляется по сигналам с блока12 фиксации нуля,В момент времени Т ) Т, по сигналу 30 35 Е 0 производится возврат схемы в ра бочее состояние для моделированиянисходящей ветви петли. Эти обратные переключения в схеме устройства также производятся в определенной последовательности. Сначала размыкаются ключи 3 и 27, При этом в исходное состояние возвращаются интегратор 31 и блок 9, на выходе которого теперь хранится конечный результат предыду- щего этапа моделирования. После это 50 го замыкается ключ 19, и в исходное состояние - режим суммирования - возвращается сумматор 8 с запоминанием.Так как моделирование этого этапапроисходит при Е (О, необходимо изме 55 нить знак сигнала, поступающего с выхода блока 7 нелинейности на первый информационный вход сумматора 8, При Е ( О на выходе ОУ 36 блока выдеви длится до момента времени С " С, когда снова Г = 1.При С = С происходит переход от моделирования нисходящей ветви к моделированию восходящей ветви петли, который проводится в той же последовательности, что и переход к предыду"щему этапу. Поскольку моделирование восходящей ветви проводится при Е О, напряжение на выходе ОУ 36 блока 35 выделения знака вновь становится рав. ным нулю, реле 38 обесточивается и ключ 34 замыкается. Снова выход блока 7 нелинейности подключается непосредственно к первому информационному входу сумматора 8 с запоминанием.Заключительный этап - моделирование восходящей ветви - длится до момента С = С , при котором вновь Е = О.Формула изобретенияУстройство для моделирования упругого гистерезиса, содержащее операционный усилитель, в цель обратной связи которого включены параллельно соединенные интегрирующий конденсатор и ключ сброса, первый и второй масштабные резисторы, первые выводы которых объединены и являются входом устройства, первый ключ, информационный вход которого подключен к второму выводу первого масштабного резистора, выход первого ключа и второй вывод второго масштабного резистора объединены и подключены к входу операционного усилителя, последовательно соединенные блок фиксации нуля и и управляемый источник напряжения, выход которого подключен к управляющему входу первого ключа, вход блока фиксации нуля подключен к входу устройства, блок нелинейности, сумматор с запоминанием, выход которого является выходом устройства, последовательно соединенные цепь управления сумматором с запоминанием и элемент46 Составитель И.ДубининаТехред Л,Сердюкова Корректор Н.Король Редактор Е.Папп Тираж 104 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб д. 4/5Заказ 2 ЬО/49 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 5 13979 задержки, последовательно соединенные третий масштабный резистор и второй ключ, аналоговый запоминающий блок, выход второго ключа подключен к первому информационному входу сум 5 матора с запоминанием, выход которого соединен с информационным входом аналогового запоминающего блока, выход которого подключен к второму инЪформационному входу сумматора с запоминанием, управляющие входы аналогового запоминающего блока и ключа сброса объединены и подключены к выходу элемента задержки, управляющий вход второго ключа подключен к выходу управляемого источника напряжения, управляющий вход сумматора с запоминанием подключен к выходу цепи управления сумматором с запоминанием, о т л и ч а ю щ е е с я тем, что, с целью повышения точности моделирования, в него введены блок выделениямодуля, инвертор, блок выделения знака входного сигнала и третий ключ,причем вход блока выделения модулясоединен с выходом операционного усилителя, а выход подключен к входублока нелинейности, выход которогосоединен с входом инвертора и первыминформационным входом третьего ключа,второй информационный вход которогоподключен к выходу инвертора, выходтретьего ключа соединен с третьим информационным входом сумматора с запоминанием и вторым выводом третьегомасштабного резистора, управлякзцийвход третьего ключа подключен к выходу блока выделения знака входногосигнала, вход которого подключен квходу устройства.

СмотретьЗаявка

4142772, 05.11.1986

КУЙБЫШЕВСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. АКАД. С. П. КОРОЛЕВА

ВЬЮЖАНИН ВЯЧЕСЛАВ АРКАДЬЕВИЧ, ДАВЫДОВ ЕВГЕНИЙ ИВАНОВИЧ, МАРТЫНОВ АЛЕКСАНДР КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G06G 7/48

Метки: гистерезиса, моделирования, упругого

Опубликовано: 23.05.1988

Код ссылки

<a href="https://patents.su/4-1397946-ustrojjstvo-dlya-modelirovaniya-uprugogo-gisterezisa.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования упругого гистерезиса</a>

Предыдущий патент: Многофазный функциональный преобразователь

Следующий патент: Устройство для моделирования механизмов шагового перемещения

Случайный патент: Устройство для подъема диэлектрической жидкости