Датчик равномерно распределенных случайных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

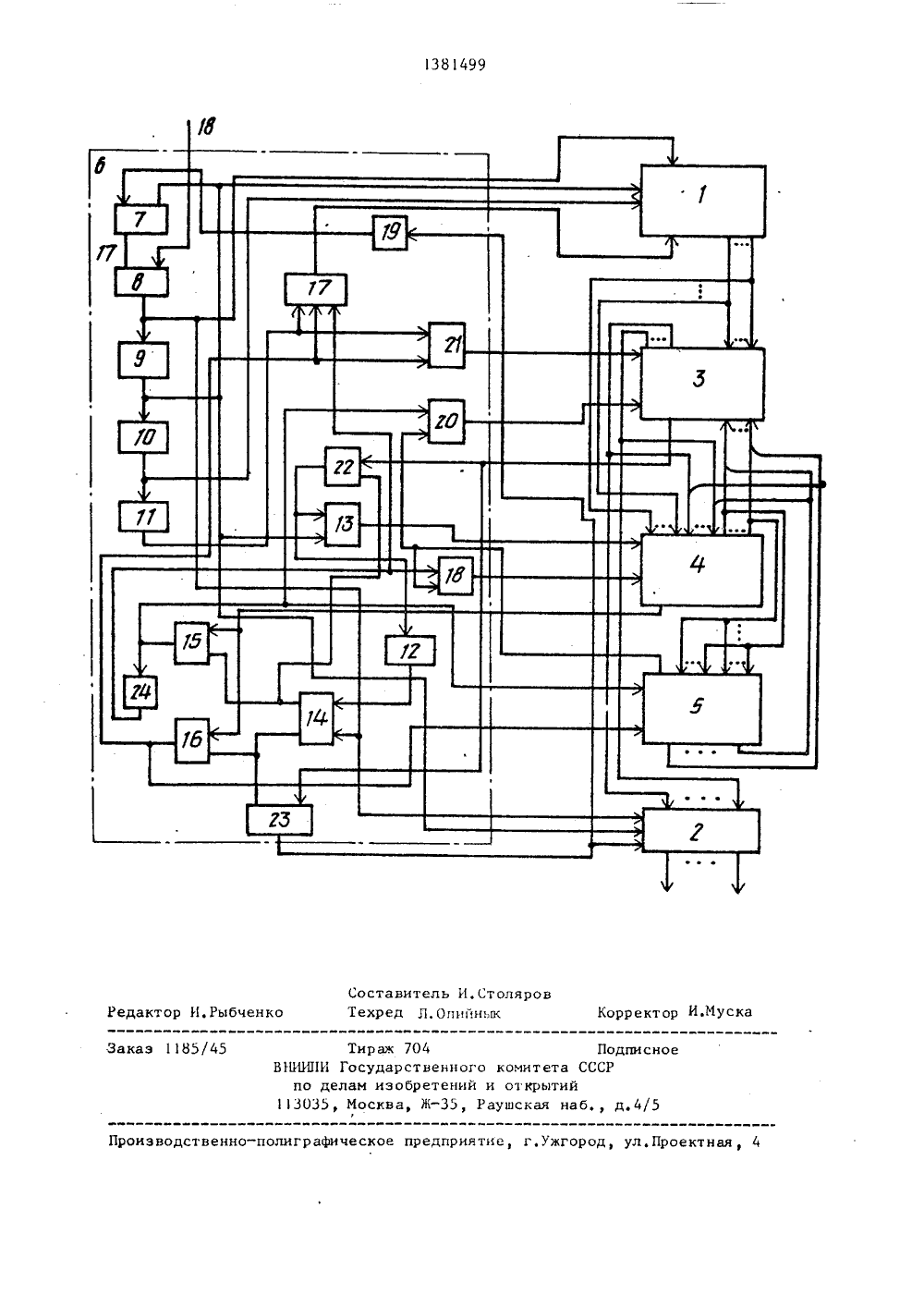

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ПИСАНИ К АВТОРСКОМ(21) 4020221/2 (22) 29,11.85 (46) 15.03.88 (72) А. Е.филю А.П.Бочков, В (53) 68.3 (О (56) Авторско М 430400, кл.Авторское с У 1256023, кл. (54) ДАТЧИК РА НИХ СЛУЧАЙНЫХ 1381499(57) Иэобрете вычислительно использовано ных моделирующи изобретения я е относится к областитехники и может бытьи построении раэлиг.х устройств. Цельюяется повышение точности датчика.достигается темрегистры, блок Поставленная цельчто датчик содержит деления, блок умножеи блок управления, -триггеров, элеменв ИЛИ и элементов эания, вычитатель состоящий иэ ВЯ тов И, элементо держки. 1 ил.Изобретение относится к вычислительной технике и может быть использовано при построении устройств для статистического моделирования.Цель изобретения - повышение точности датчика.На чертеже представлена структурная схема датчика.Датчик содержит регистр 1 памяти, регистр 2, блок 3 деления, блок 4 умножения, вычитатель 5 и блок 6 управления.Блок 6 управления содержит ВБ- триггер 7, элемент И 8, элементы15 9-12 задержки, элемент ИЛИ 13, Ю- триггер 14, элементы И 15 и 16, элементы И)И 17 и 18, элемент 19 задержки, элементы ИЗП 20 и 21, элементы И 22 и 23, элемент 24 задержки.20Датчик работает следующим образом.В исходном состоянии случайное число 1)и, находится в регистре 2.ВБ- триггер 7 блока Ь управления установлен в состояние, при котором на 25 его выходе присутствует высокий уровень, свидетельствующий о том, что датчик готов к работе, Высоким уровнем подготовлен к срабатыванию элемент И 8, Число У находится в блоке 4 в качестве первого операнда. Сигнал запуска от внешнего устройства через элемент И 8 поступает на регистры 1 и 2 и на Ж-триггер 14. В регистр 1 заносится параплельным кодом константа К, = 47000135 = О 11001010111110001 п. Из регистра 2 на выход датчика выдается случайное число, ВБ-триггер 14 переводится всостояние, при котором на его выходе 40 появляется высокий уровень, подготавливающий к работе элемент И 15. Сигнал запуска датчика после элемента И 8 последовательно проходит элементы 9,10 и 11 задержки. С элемента 9 45 задержки сигнал поступает на В-вход ВБ-триггера 7 и через элемент ИЛИ 13 - на вход записи блока 4 умножения. ВБ-триггер 7 переводится в состояние, при котором на его выходе50 появляется низкий уровень, свидетельствующий о том, что датчик запущен и до окончания формирования случайного числа Уэлемент И 8 закрыт,Сигналом с выхода элемента 10 задержки в регистр 1 заносится константа К = = 999563 - " 111101000000100010111) которая по сигналу с элемента 11 задержки заносится в блок 3 деления в качестве первого операнда. По окончании умножения на выходе конца операции блока 4 умножения появляетсясигнал, который проходит через элемент И 15 на первый вход записи вычитателя 5 и элемент ИЛИ 20 на второйвход записи блока 3 деления. В блок3 заносится произведение, и он запускается, Кроме того, произведениеЖК, заносится в качестве первогооперанда в вычитатель 5, Сигнал с выхода элемента И 15 после задержки наэлементе 24 задержки поступает черезэлементы ИЛИ 17 и 18 соответственнона первый вход чтения регистра 1 ивторой вход записи блока 4 умножения.После окончания операции деления навыходе конца операции блока 3 появляется сигнал, который пройдя элемент И 22, открытый высоким уровнемс ВБ-триггера 14, элемент ИЛИ 13,поступает на второй вход записи блока 4 и осуществляет занесение результата деления и запуск блока 4 на выполнение второй операции умножения,С элемента И 22 сигнал через элемент12 задержки поступает на ВБ-триггер14 и переводит его в противоположноесостояние. Теперь высоким уровнем попервому входу подготовлены элементыИ 16 и 23. После второго умножениякап К 1,результат--- ) К по сигналус выхода конца операции блока 4 черезэлемент И 16 заносится в вычитатель5 в качестве второго операнда и вычитат ель 5 з апускается . Одно вр еменнопо сигналу с выхода элемента И 16 изрегистра 1 считывается константа Ки заносится в блок 3 деления в качестве первого операнда, После вычитания результат И = И КттрК 1- - - - ) К заносится в блок1Я4 в качестве первого, а в блок 3 -второго операнда. Блок 3 запускаетсяна выполнение второй операции деления, Сигнал с выхода конца операцииблока 3 проходит через элемент И 23,открытый высоким уровнем с Ю-триггера 14, на вход записи регистра 2и обеспечивает занесение в него случайного числа Уп= МК,1.1 к 1 к, кроме тогоКгБ-входу переводит ВБ-триггер 7 всостояние, при котором на его выходепоявляется высокий уровень, открьгвающий по первому входу элемент И 8и свидетельствующий о готовности5датчика к выдаче случайного числаи формула иэ обретенияДатчик равномерно распределенных случайных чисел, содержащий регистр памяти, выход которого является выходом датчика, о т л и ч а ю щ и йс я тем, что, с целью повышения точ ности, он содержит регистр, блок деления, блок умножения,. вычитатель и блок управления, который содержит два ВБ-триггера, пять элементов И, пять элементов ИЛИ, шесть элементов задержки, причем выход первого элемента И блока управления через последовательно соединенные второй и третий элементы задержки соединен с первым входом первого элемента ИЛИ,вто рой вход которого соединен с выходом второго элемента И, первый вход которого соединен с первым входом третьего элемента И и подключен к выходу конца операции блока умножения, выход третьего элемента И через четвертый элемент задержки соединен с третьим входом первого элемента ИЛИ, выход которого соединен с пер-. вым входом чтения регистра, выход первого ВБ-триггера соединен с пер 35 вым входом первого элемента И,второй вход которого является входомПуск датчика, В-вход первого ВБ-триггера соединен с выходом первого элемента задержки и с первым входом второго элемента ИЗЫДИ, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с прямым выходом второго ВБ-триг 45 гера и подключен к второму входу третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с первым входом четвертого50 элемента ИЛИ и подключен к выходу конца операции вычитателя, второй вход четвертого элемента ИЛИ соединен с выходом четвертого элемента задержки, второй вход четвертого элемента И соединен с первым входом пя 55 того элемента И и подключен к выходу конца операции блока деления, вто" рой вход пятого элемента И соединенс инверсным выходом второго ВБтриггера и подключен к второму входувторого элемента И, Б-вход второгоВБ-триггера соединен с выходом первого элемента И, В-вход второго ВБтриггера соединен с выходом пятогоэлемента задержки, вход которого соединен с выходом четвертого элементаИ, первый вход первого элемента ИЛИсоединен с первым входом пятого элемента ИЛИ и подключен к выходутретьего элемента задержки, второйвход пятого элемента ИЛИ соединен свторым входом первого элемента ИЛИ,выход шестого элемента задержки подключен к Б-входу первого ВБ-триггера, выход первого элемента И блокауправления соединен с первым входомзаписи регистра, выход которого соединен с первым информационным входомблока деления и с первым информационным входом блока умножения, выходпервого элемента задержки соединенс вторым входом чтения регистра,второй вход записи которого соединен свыходом второго элемента задержкиблока управления, выход блока деления соединен с вторым информационнымвходом блока умножения, выход которого соединен с вторым информационнымвходом блока деления, выход пятогоэлемента ИЛИ блока соединен с первымвходом записи блока деления, второйвход записи которого соединен с вьгходом третьего элемента ИЛИ блокауправления, информационный выход блока умножения соединен с первым ивторым информационными входами вычитателя, выход которого подключен квторому информационному входу блокаделения, первый вход записи вычитателя соединен с выходом третьего элемента И блока управления, второй входзаписи вычитателя соединен с выходомвторого элемента И блока управления,выход блока деления соединен с информационным входом регистра памяти,вход чтения которого соединен с Бвходом второго ВБ-триггера блока управления, вход обнуления регистрапамяти соединен с выходом первогоэлемента задержки блока управления,вход записи регистра памяти соединенс выходом пятого элемента И блока управления и входом шестого элементазадержки блока управления.1381499 оставитель И, Столяроехред Л, Олийнык орректор И.Мус Редактор И.Рыбче Заказ 1185 45 одственно-полиграфическое предприятие, г.ужгород, ул.Проектная Тираж 704 1 ИИПИ Государственн по делам изобретен 3035, Москва, ЖПодписноего комитета СССРй и открытийР аушс к ая на б., д, 4/5

СмотретьЗаявка

4020221, 29.11.1985

ВОЕННАЯ АРТИЛЛЕРИЙСКАЯ КРАСНОЗНАМЕННАЯ АКАДЕМИЯ ИМ. М. И. КАЛИНИНА

ФИЛЮСТИН АНАТОЛИЙ ЕГОРОВИЧ, БОЕВ ВАСИЛИЙ ДМИТРИЕВИЧ, БОЧКОВ АЛЕКСАНДР ПЕТРОВИЧ, ВОЛКОВ ВИКТОР АЛЕКСАНДРОВИЧ, ГОЛИК ЕВГЕНИЙ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 7/58

Метки: датчик, равномерно, распределенных, случайных, чисел

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/4-1381499-datchik-ravnomerno-raspredelennykh-sluchajjnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Датчик равномерно распределенных случайных чисел</a>

Предыдущий патент: Логарифмический преобразователь

Следующий патент: Устройство для формирования случайного процесса

Случайный патент: Прибор для построения дуги эллипса