Дискретно-аналоговый интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1372337

Автор: Заклецкая

Текст

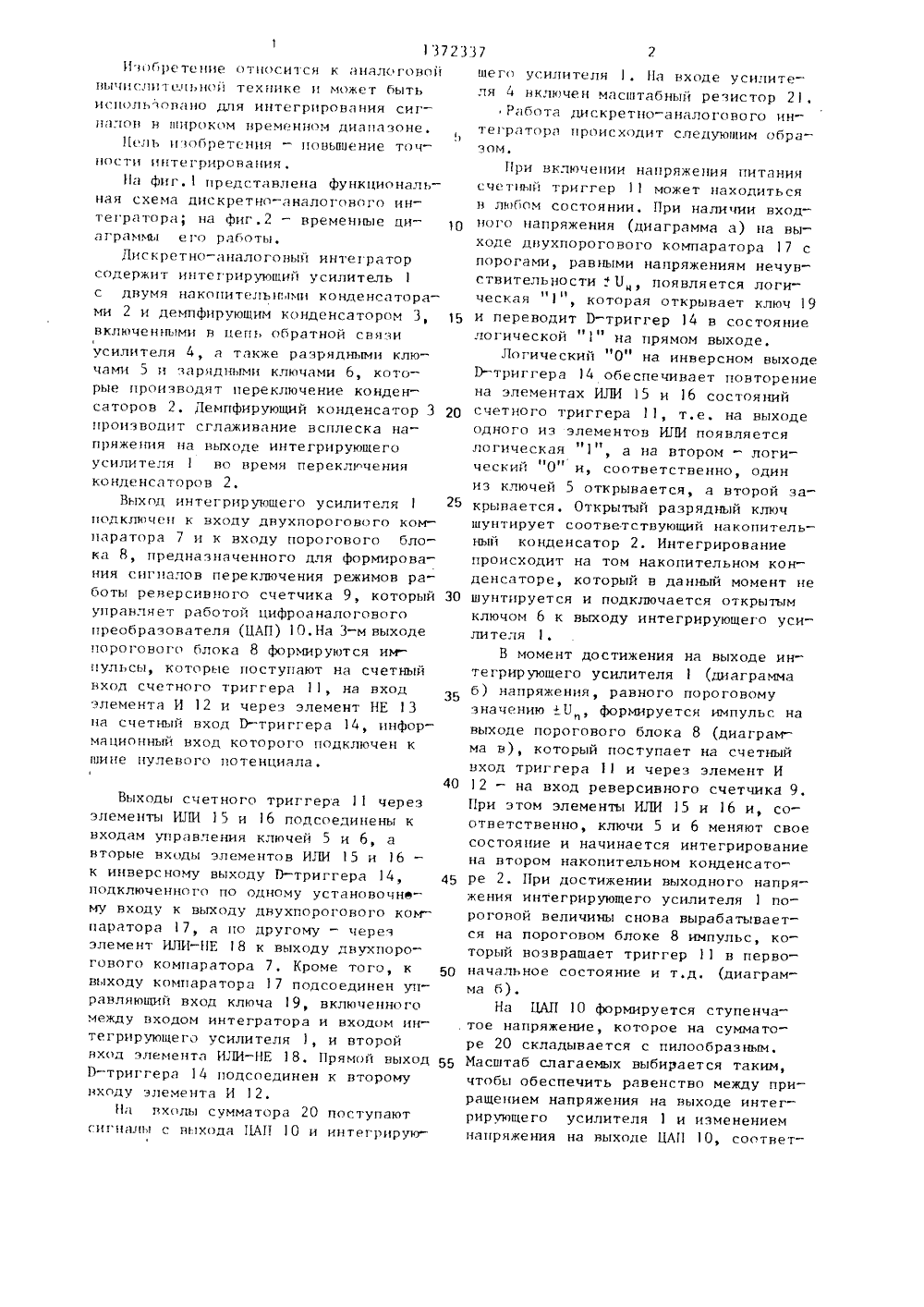

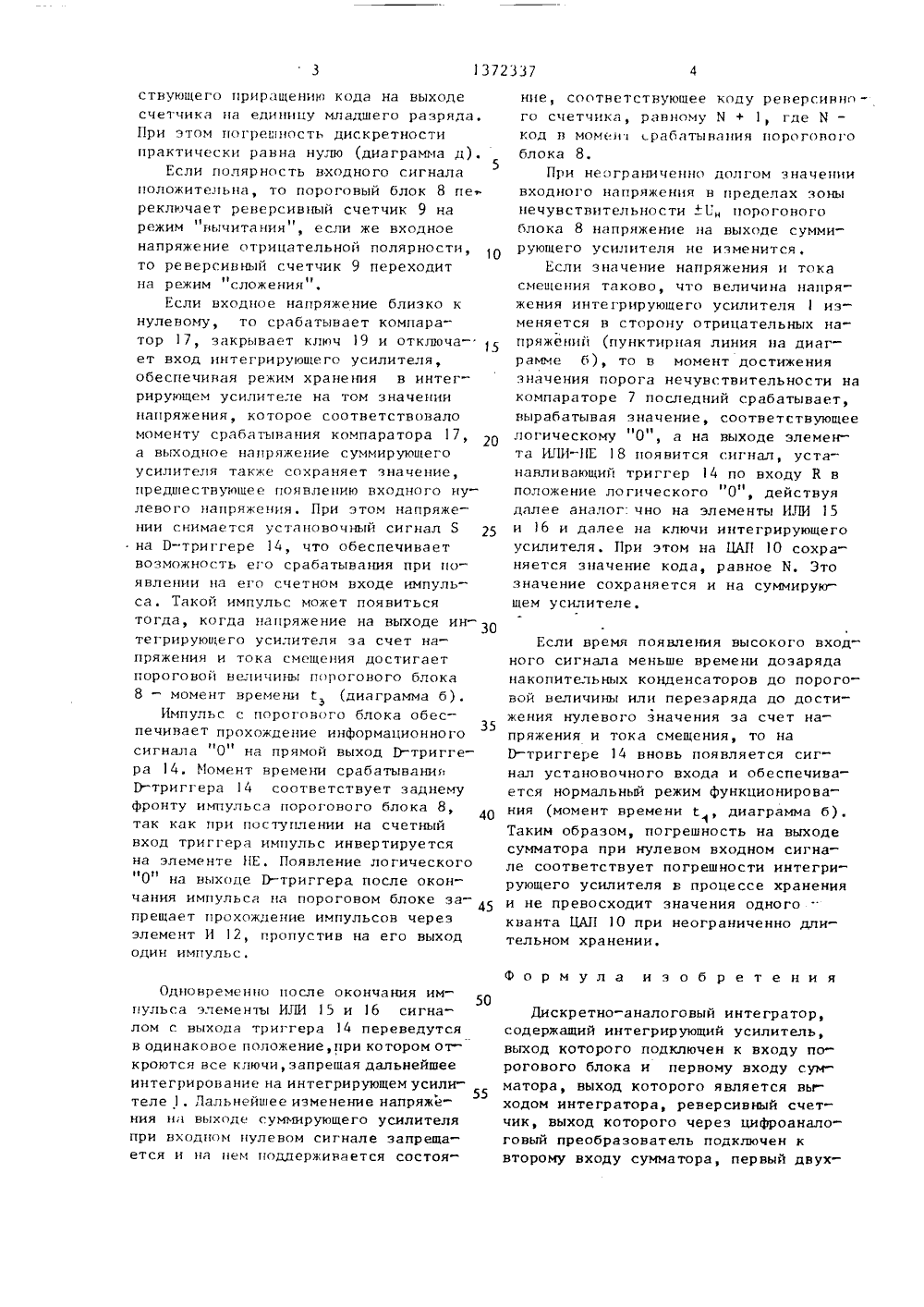

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 19 51)4 С 06 186 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ СР 1" 1 Р ЗОБРЕТЕНИ ИСА У СВИДЕТЕЛЬСТ ВТОРС У 5торское бюро биокой кибернетики ельство СССР 7/186) 1980, ьство СССР 7186, 1976,(54) ДСКРЕТНО-А 1 АЛОГОВЪЙ ИНТЕГР (57) Изобретение относится к обл аналоговой вычислительной техник может быть использовано для инте рования сигналов в ш .роком време диапазоне. Цель изобретения - по ние точности интегрирования. Дис но-аналоговый интегратор содержи тегрирующий усилитель 1 с накопи ными конденсаторами 2, демпфирую конденсатором 3, включенным в це обратной связи усилителя 4, разр сти уси сФ сти ном ин- ельил.(56) Авторское свидУ 866563, кл, С 06 САвторское свидет1 611218, кл. 0 06 ми ключами 5 и зарядными ключами 6,двухпороговый компаратор 7, пороговый блок 8, реверсивный счетчик 9,цифроаналоговый преобразователь 10,счетный триггер 11,элемент И 12,элемент НЕ 13, Э-триггер 14, элементы ИЛИ 15, 16 двухпороговый компаратор 17, элемент ИЛИ-НЕ 18, ключ 19,сумматор 20, Интегратор обеспечиваетвозможность интегрирования апериодического входного сигнала с нулевойизолинией. При этом в пределах зонынечувствительности двухпороговогокомпаратора 17 происходят отключениеинтегрирующего усилителя от входногосигнала и переход интегрирующеголителя в режим хранения. Погрешноинтегратора при нулевом сигнале в зависимости от времени интегрированияравны погрешности хранения интегрирующего усилителя и не превосходятпогрешности дискретности при неограниченно длительном интегрировании.15 20 25 30 35 40 45 50 55 И обретение относится к аналоговойг)ы)гиснитгь(ц)цой техцике и может быть использовано для интегрирования сигцд:ог) в широком временном диапазоне.Цель и )обретения - повышение точности интегрирования,Нд фиг. представлена функциональная схема дискретно-аналогового интегратора; на фиг.2 - временные цидгрдмлгы его работы.Лискретцо-дцдлогоный интеграторсодержит интегрирующий усилитель 1с двумя накопительными конденсдтора -ми 2 и демпфирующим конденсатором 3,вклн)ченными в цепь обратной связиусилителя 4, д тдкже разрядными ключами 5 и зарядными ключами 6, которые производят переключение конденсаторов 2. Демпфирующий конденсатор 3производит сглаживание всплеска напряжения ца выходе интегрирующегоусилителя 1 во время переклк)ченияконденсаторов 2.Выход интегрирующего усилителяггодклк)чец к входу двухпорогового комидрдтора 7 и к входу порогового блока 8, предназначенного для формирования сигцалов переключения режимов работы реверсивного счетчика 9, которыйуправляет работой цифроаналоговогопреобразователя (ЦАП) 10.На 3-м выходепорогового блока 8 формируются импульсы, которые поступают на счетныйвход счетного триггера 11, на входэлемента И 12 и через элемент НЕ 13ца счетный вход Р-триггера 14, информационный вход которого подключен кшине нулевого потенциала. Выходы счетного триггера 1 через элемеггты ИЛИ 15 и 16 подсоединены к входам управления ключей 5 и 6, а вторые входы элементов ИЛИ 15 и 16 к инверсному выходу Р-триггера 14, подключенного по одному установочнему входу к выходу двухпорогового комиаратора 17, д ио другому - через элемент ИЛИ-НЕ 18 к выходу двухпорогового комиаратора 7. Кроме того, к выходу компараторд 17 подсоединен управляющий вход ключа 19, включенного между входом интегратора и входом интегрирующего усилителя 1, и второй вход элемента ИЛИ-НЕ 18. Прямой выход Р-триггера 14 подсоединен к второму входу элемента И 12.Нд входы сумматора 20 поступают сигцдль) с выхода ЦА 1 10 и интегрирующего усилителя 1. Нд входе усилителя 4 нключен масштабный резистор 2.Работа дискретно-аналогового интегратора происходит следующим образом.При включении напряжения питдния счетный триггер 11 может находиться в лк)бом состоянии. При наличии входного цапряжения (диаграмма а) ца выходе двухпорогового компаратора 17 с порог ами, равными напряжениям нечувствительности ". Б, появляется логическая "1", которая открывает ключ 19 и переводит Р-триггер 4 в состояние логической на прямом выходе.Логический "0" на инверсном выходе Р-триггера 14 обеспечивает повторение на элементах ИЛИ 15 и 16 состояний счетного триггера 1, т.е. на выходе одного из элементов ИЛИ появляется логическдя "1", а на втором - логический О( и, соответственно, одиниз ключей 5 открывается, а второй закрывается. Открытый разрядный ключшунтирует соответствующий накопительный конденсатор 2. Интегрированиепроисходит на том накопительном конденсаторе, который в данный момент це шунтируется и подключается открытым ключом 6 к выходу интегрирующего усилителя 1,В момент достижения на выходе интегрирующего усилителя 1 (диаграмма б) напряжения, равного пороговому значению ( У, формируется импульс на выходе порогового блока 8 (диаграмма в), который поступает на счетный вход триггера 11 и через элемент И 12 - на вход реверсивного счетчика 9. При этом элементы ИЛИ 15 и 16 и, соответственно, ключи 5 и 6 меняют своесостояние и начинается интегрированиена втором накопительном конденсаторе 2. При достижении выходного напряжения интегрирующего усилителя 1 пороговой величины снова вырабатывается на пороговом блоке 8 импульс, который возвращает триггер 11 в первоначальное состояние и т.д. (диаграмма б).На ЦАП 1 О формируется ступенчатое напряжение, которое на сумматоре 20 складывается с пилообразным. Масштаб слагаемых выбирается таким,чтобы обеспечить равенство между приращением напряжения на выходе интегрирующего усилителяи изменениемнапряжения на выходе ЦАП 10, соответ 3 1372337 4ствующего приращению кода на выходесчетчика ца единицу младшего разряда. При этом погрешность дискретности практически равна нулю (диаграмма д).5Если полярность входного сигнала положительна, то пороговый блок 8 пе реключает ренерсивцый счетчик 9 на11 црежим вычитания, если же входное напряжение отрицательной полярности, то реверсивный счетчик 9 переходит на режимсложения .Если входное напряжение близко к нулевому, то срабатывает компаратор 17, закрывает ключ 19 и отключает вход интегрирующего усилителя, обеспечивая режим хранения в интегрирующем усилителе на том значениинапряжения, которое соответствовало моменту срабатывания компаратора 17, а выходное напряжение суммирующего усилителя также сохраняет значение, предшествующее появлению входного нулевого напряжения. При этом напряжении снимается установочный сигнал Б 25 на П-триггере 14, что обеспечивает возможность его срабатывания при появлении ца его счетном входе импульса. Такой импульс может появиться тогда, когда напряжение на выходе ин тегрирующего усилителя эа счет напряжения и тока смещения достигает пороговой величины порогового блока 8 - момент времени Г (диаграмма б).эИмпульс с порогового блока обеспечивает прохождение информационного35 сигнала цО на прямой выход )-триггера 14. Момент времени срабатывани Ел-триггера 4 соответствует заднему фронту импульса порогового блока 8, так как при поступлении на счетныйвход триггера импульс инвертируется на элементе ПЕ. Появление логического цОц на выходе П-триггера после окончания импульса ца пороговом блоке за прещает прохождение импульсов через элемент И 12, пропустив на его выход один импульс. Одновременно после окончания импульса элементы ИЛИ 15 и 16 сигналом с выхода триггера 4 переведутся в одинаковое положение,при котором откроются все ключи, запрещая дальнейшее интегрирование на интегрирующем усили 55 теле 1. Дальнейшее изменение напряжения и выходе суммирующего усилителя при входном цулевом сигнале запрещается и ца цем поддерживается состояние, соответствующее коду реверсивцо -го счетчика, равному М + 1, где И -код в момен срабатывания пороговогоблока 8,При неограниченно долгом значениивходного напряжения в пределах зонынечувствительности Г пороговогоблока 8 напряжение ца выходе суммирующего усилителя не изменится,Если значение напряжения и токасмещения таково, что величина цапряжения интегрирующего усилителя 1 изменяется в сторону отрицательных напряжений (пунктирная линия на диаграмме б), то в момент достижениязначения порога нечувствительности накомпараторе 7 последний срабатывает,вырабатывая значение, соответствующеелогическому 0, а на выходе элемента ИЛИ-Е 18 появится сигнал, устанавливающий триггер 4 по входу К вположение логического 0, действуядалее аналог: чно на элементы ИЛИ 15и 16 и далее на ключи интегрирующегоусилителя. При этом на ЦАП 1 О сохраняется значение кода, равное И. Этозначение сохраняется и на суммирующем усилителе,Если время появления высокого входного сигнала меньше времени дозаряданакопительных конденсаторов до пороговой величины или перезаряда до достижения нулевого значения за счет напряжения и тока смещения, то на0-триггере 14 вновь появляется сигнал установочного входа и обеспечивается нормальный режим функционирования (момент времени Т, диаграмма б),Таким образом, погрешность на выходесумматора при нулевом входном сигнале соответствует погрешности интегрирующего усилителя в процессе храненияи не превосходит значения одногокванта ЦАП 10 при неограниченно длительном хранении,формула изобретенияДискретно-аналоговый интегратор, содержащий интегрирующий усилитель, выход которого подключен к входу порогового блока и первому входу сумматора, выход которого является вью.ходом интегратора, реверсивный счетчик, выход которого через цифроаналоговый преобразователь подключен к второму входу сумматора, первый двух1372337 триггера. Составитель С. БеланТехред М.Ходанич Редактор В.Данко Корректор М.Шарощи Заказ 484/41 Тираж 704 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб д, 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4 пороговый компаратор, вход которогосоединен с входом интегратора, счетньп триггер, вход которого подключенк импульсному выходу порогового блока, два элемента ИЛИ, первые входыкоторых соединены с выходом счетноготриггера, а выходы подключены к первому и второму входам соответственноуправления зарядом-разрядом интегратора, о т л и ч а ю щ и й с я тем,что, с целью повышения точности интегрирования, в него введены второйдвухпороговый компаратор, Э-триггер,элементы И, ИЛИ-НЕ, НЕ и ключ, включенный между входом интегратора ивходом интегрирующего усилителя, выход первого двухпорогового компаратора подключен к управляющему входуключа, первому установочному входу0-триггера и первому входу элемента ИЛИ-НЕ, второй вход которого соединен с выходом второго двухпорогового компаратора, входом подключенного к выходу интегрирующего усилителя, выход элемента ИЛИ-НЕ соединен с вторым установочным входом Р-триггера, информационный вход которого связан с шиной нулевого потенциала, счетный вход через элемент НЕ подключен к импульсному выходу порогового блока, соединенному с первым входом элемента И, второй вход которого подключен к прямому выходу В-триггера, а выход соединен со счетным входом реверсивного счетчика, входы управления направлением счета которого соединены со знаковыми выходами порогового блока, причем вторые входы элементов ИЛИ 20 подключены к инверсному выходу 0

СмотретьЗаявка

4122837, 11.06.1986

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО БИОЛОГИЧЕСКОЙ И МЕДИЦИНСКОЙ КИБЕРНЕТИКИ

ЗАКЛЕЦКАЯ ЖАННЕТА ЯКОВЛЕВНА

МПК / Метки

МПК: G06G 7/186

Метки: дискретно-аналоговый, интегратор

Опубликовано: 07.02.1988

Код ссылки

<a href="https://patents.su/4-1372337-diskretno-analogovyjj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Дискретно-аналоговый интегратор</a>

Предыдущий патент: Развертывающий преобразователь

Следующий патент: Функциональный генератор

Случайный патент: Способ получения полиамидоэфиров