Генератор псевдослучайной последовательности импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1277362

Авторы: Каракушьян, Седунов

Текст

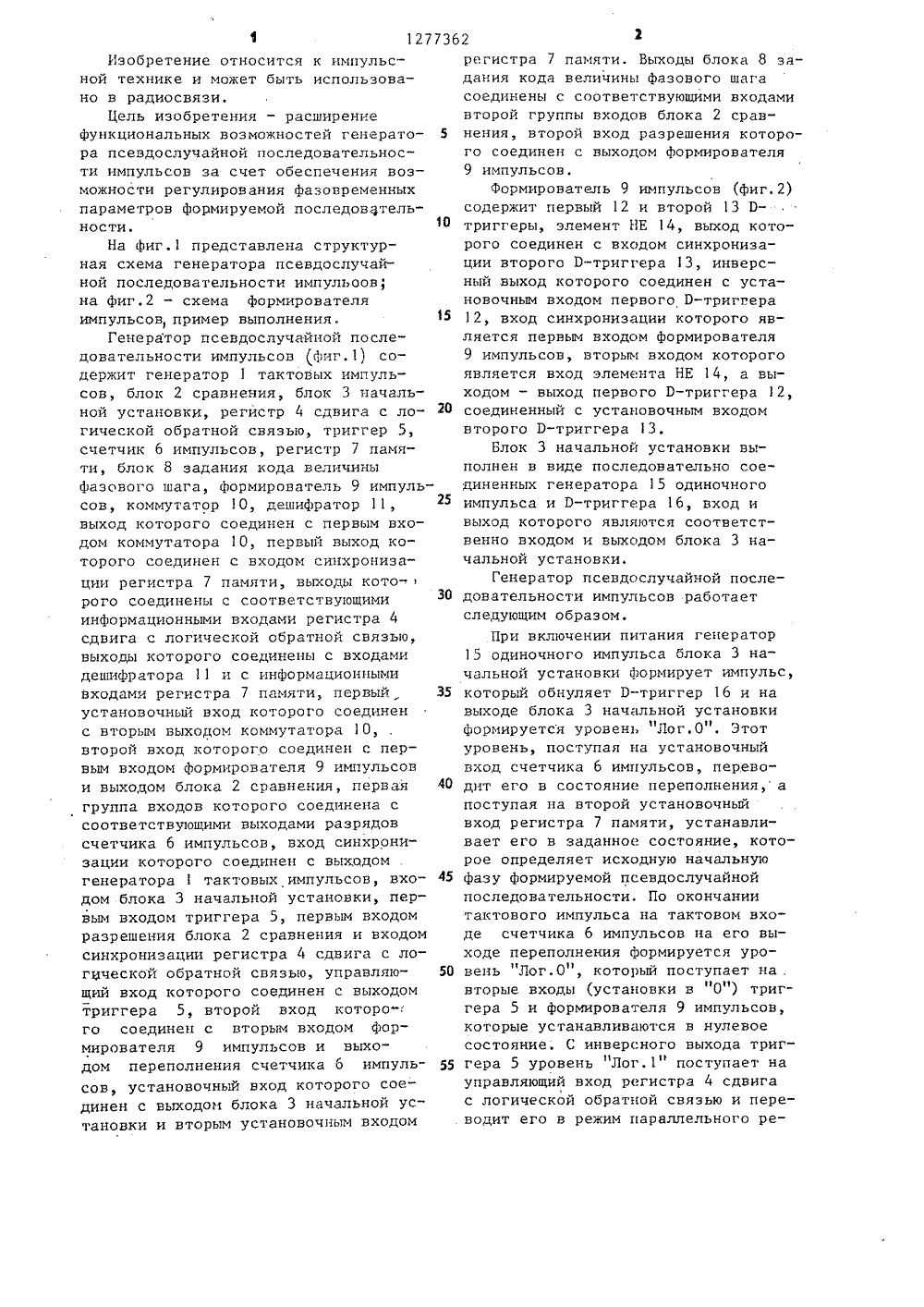

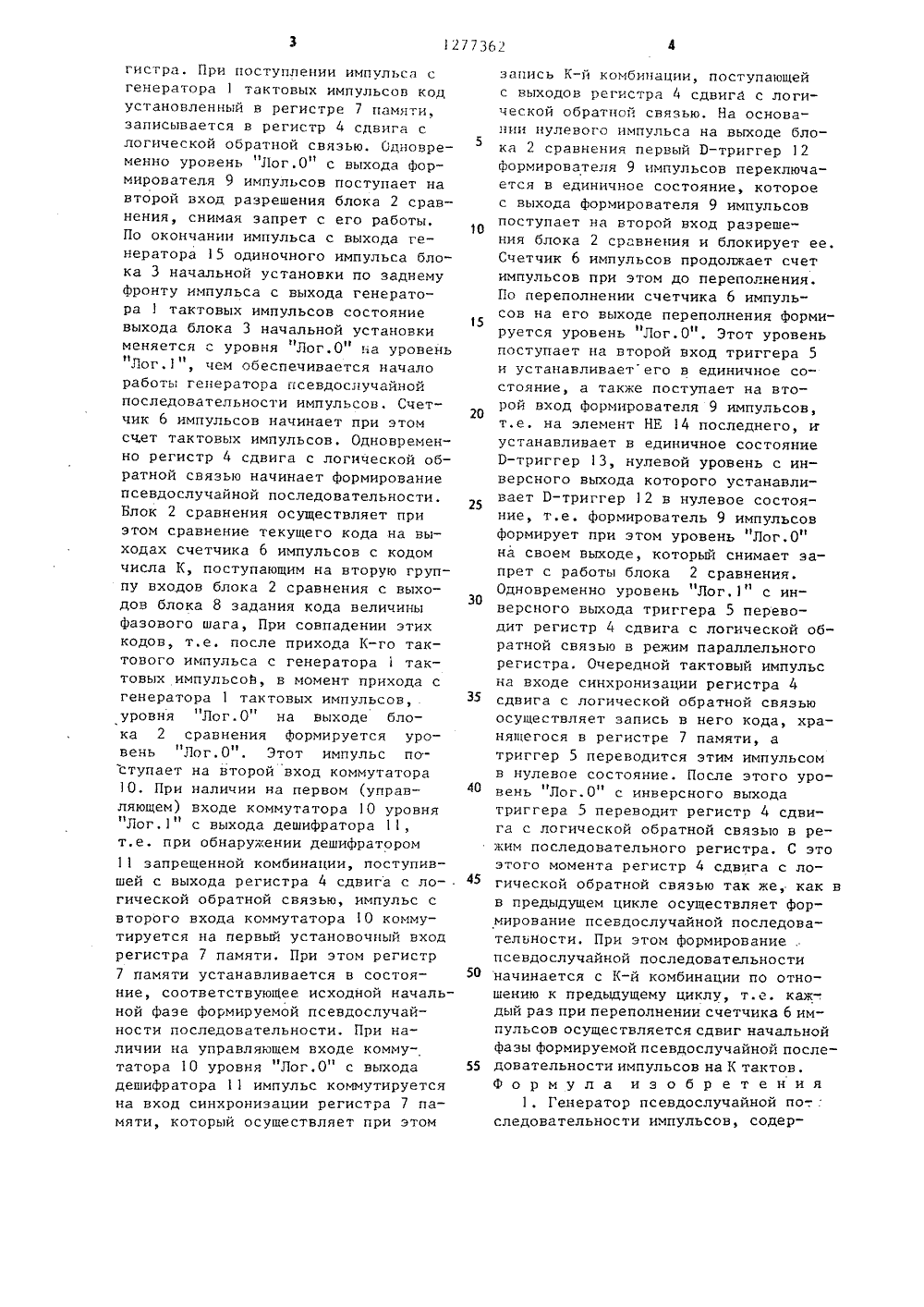

(2 (22 ледова ститут о СССР1978,СССР1978.НОЙ ПОиспол забре нкцио СУДАРСТ 8 ЕННЬЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ОПИСАНИЕ ИЗО К АВТОРСКОМУ(71) Горьковский ордена ТруКрасного Знамени научно-истельский радиофизический и(54) ГЕНЕРАТОР ПСЕВДОСЛУЧАСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ(57) Изобретение может бытьзовано в радиосвязи. Цельютения является расширение ф налъных возможностей, Для достижения цели в генератор псевдослучайной последовательности импульсов введены блок 3 начальной установки) блок 2 сравнения, триггер 5, счетчик 6 импульсов, регистр 7 памяти, блок 8 задания кода величины фазового шага, формирователь 9 импульсон и дешифратор 11. Генератор псевдослучайной последовательности импульсов также содержит генератор 1 тактовых импульсов, регистр 4 сдвига с логической обратной связью, коммутатор 10. Данный генератор обеспечивает воэможность регулирования фазовременных параметров формируе= мой последовательности. 1 з.п.ф-лы. 2 ил.7362 2 5 10 15 20 1 127Изобретение относится к импульсной технике и может быть использовано в радиосвязи.Цель изобретения - расширениефункциональных возможностей генератора псевдослучайной последовательности импульсов за счет обеспечения возможности регулирования фазовременныхпараметров формируемой последовательности.На фиг.1 представлена структурная схема генератора псевдослучайной последовательности импульоов;на фиг.2 - схема формирователяимпульсов, пример выполнения.Генератор псевдослучайной последовательности импульсов (Фиг.) содержит генератор 1 тактовых импульсов, блок 2 сравнения, блок 3 начальной установки, регистр 4 сдвига с логической обратной связью, триггер 5,счетчик 6 импульсов, регистр 7 памяти, блок 8 задания кода величины Фазового шага, Формирователь 9 импульсов, коммутатор 1 О, дешифратор 11, выход которого соединен с первым входом коммутатора 1 О, первый выход которого соединен с входом синхронизации регистра 7 памяти, выходы которого соединены с соответствующими информационными входами регистра 4 сдвига с логической обратной связью, выходы которого соединены с входами дешифратора 11 и с информационными входами регистра 7 памяти первый . установочный вход которого соединен с вторым выходом коммутатора 1 О, второй вход которого соединен с первым входом Формирователя 9 импульсов и выхоцом блока 2 сравнения, первая группа входов которого соединена с соответствующими выходами разрядов счетчика 6 импульсов, вход синхронизации которого соединен с выходом генератора 1 тактовых импульсов, входом блока 3 начальной установки, первым входом триггера 5, первым входом разрешения блока 2 сравнения и входом синхронизации регистра 4 сдвига с логической обратной связью, управляющий вход которого соединен с выходом триггера 5, второй вход которо": го соединен с вторым входом Формирователя 9 импульсов и выходом переполнения счетчика 6 импульсов, установочный вход которого соединен с выходом блока 3 начальной установки и вторым установочным входом 25 30 35 40 45 50 55 регистра 7 памяти, Выходы блока 8 задания кода величины фазового шага соецинены с соответствующими входами второй группы входов блока 2 сравнения, второй вход разрешения которого соединен с выходом формирователя 9 импульсов.Формирователь 9 импульсов (фиг.2) содержит первый 12 и второй 13 Р- триггеры, элемент НЕ 14, выход которого соединен с входом синхронизации второго Р-триггера 13, инверсный .выход которого соединен с установочным входом первого 0-триггера 12, вход синхронизации которого является первым входом формирователя 9 импульсов, вторым входом которого является вход элемента НЕ 14, а выходом - выход первого 0-триггера 12,соециненный с установочным входом второго Р-триггера 13.Блок 3 начальной установки выполнен в виде последовательно соединенных генератора 15 одиночногоимпульса и Э-триггера 16, вход ивыход которого являются соответственно входом и выходом блока 3 начальной установки.Генератор псевдослучайной последовательности импульсов работаетслецующим образом,При включении питания генератор15 одиночного импульса блока 3 начальной установки формирует импульс,который обнуляет П-триггер 1 б и навыходе блока 3 начальной установкиформируется уровень нЛог.О, Этотуровень, поступая на установочныйвход счетчика 6 импульсов, переводит его в состояние переполнения, апоступая на второй установочныйвход регистра 7 памяти, устанавливает его в заданное состояние, которое определяет исходную начальнуюфазу формируемой псевдослучайнойпоследовательности, По окончаниитактового импульса на тактовом входе счетчика б импульсов на его выходе переполнения формируется уровень Лог.О", который поступает на .вторые входы (установки в О) триггера 5 и формирователя 9 импульсов,которые устанавливаются в нулевоесостояние. С инверсного выхода триггера 5 уровень "Лог.1" поступает науправляющий вход регистра 4 сдвигас логической обратной связью и переводит его в режим параллельного ре 1277362гистра. При поступлении импульса с генератора 1 тактовых импульсов код установленный в регистре 7 памяти, записывается в регистр 4 сдвига с логической обратной связью. Одновременно уровень "Лог.011 с выхода формирователя 9 импульсов поступает на второй вход разрешения блока 2 сравнения, снимая запрет с его работы, По окончании импульса с выхода генератора 15 одиночного импульса блока 3 начальной установки по заднему фронту импульса с выхода генератора 1 тактовых импульсов состояние выхода блока 3 начальной установки меняется с уровня 11 Лог.011 на уровень 11 11Лог,1 , чем обеспечивается начало работы генератора псевдослучайной последовательности импульсов, Счетчик б импульсов начинает при этом счет тактовых импульсов. Одновременно регистр 4 сдвига с логической обратной связью начинает формирование псевдослучайной последовательности, Блок 2 сравнения осуществляет при этом сравнение текущего кода на выходах счетчика б импульсов с кодом числа К, поступающим на вторую группу входов блока 2 сравнения с выходов блока 8 задания кода величины фазового шага, При совпадении этих кодов, т.е. после прихода К-го тактового импульса с генератора 1 тактовых импульсоЬ, в момент прихода с генератора 1 тактовых импульсов,. уровня "Лог.О" на выходе блока 2 сравнения формируется уровень 1 Лог.011. Этот импульс поступает на второй вход коммутатора 10, При наличии на первом (управляющем) входе коммутатора 10 уровня "Лог.1" с выхода дешифратора 11, т.е, при обнаружении дешифратором 11 запрещенной комбинации, поступившей с выхода регистра 4 сдвига с логической обратной связью, импульс с второго входа коммутатора 10 коммутируется на первый установочный вход регистра 7 памяти. При этом регистр 7 памяти устанавливается в состояние, соответствующее исходной начальной фазе формируемой псевдослучайности последовательности, При наличии на управляющем входе коммутатора 10 уровня "Лог.О" с выхода дешифратора 11 импульс коммутируется на вход синхронизации регистра 7 памяти, который осуществляет при этом 5 1 О 5 20 25 30 Э 5 40 45 50 55 запись К-й комбинации, поступающей с выходов регистра 4 сдвига с логической обратной связью, На основании нулевого импульса на выходе блока 2 сравнения первый 0-триггер 12 формирователя 9 импульсов переключается в единичное состояние, которое с выхода формирователя 9 импульсов поступает на второй вход разрешения блока 2 сравнения и блокирует ее. Счетчик 6 импульсов продолжает счет импульсов при этом до переполнения. По переполнении счетчика 6 импульсов на его выходе переполнения формируется уровень 11 Лог.011. Этот уровень поступает на второй вход триггера 5 и устанавливаетего в единичное состояние, а также поступает на второй вход формирователя 9 импульсов, т,е. на элемент НЕ 14 последнего, и устанавливает в единичное состояние 0-триггер 13, нулевой уровень с инверсного выхода которого устанавливает Р-триггер 12 в нулевое состояние, т.е. формирователь 9 импульсов формирует при этом уровень "Лог,011 на своем выходе, который снимает запрет с работы блока 2 сравнения. Одновременно уровень 1 Лог." с инверсного выхода триггера 5 переводит регистр 4 сдвига с логической обратной связью в режим параллельногорегистра. Очередной тактовый импульс на входе синхронизации регистра 4 сдвига с логической обратной связью осуществляет запись в него кода, хранящегося в регистре 7 памяти, а триггер 5 переводится этим импульсомв нулевое состояние. После этого уровень Лог.О с инверсного выхода триггера 5 переводит регистр 4 сдвига с логической обратной связью в режим последовательного регистра. С это этого момента регистр 4 сдвига с логической обратной связью так же, как вв предыдущем цикле осуществляет формирование псевдослучайной последовательности. При этом формированиепсевдослучайной последовательности начинается с К-й комбинации по отношению к предыдущему циклу, т.е. каж-, дый раз при переполнении счетчика 6 импульсов осуществляется сдвиг начальной фазы формируемой псевдослучайной последовательности импульсов на К тактов. Формула изобретения1. Генератор псевдослучайной по-.: следовательности импульсов, содер5127 жащий генератор тактовых импульсов, регистр сдвига с логической обратной связью и коммутатор, о т л и - ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности регулирования фазовременных параметров формируемой последовательности, в него введены блок начальной установки, блок сравнения, триггер, счетчик импульсов, регистр памяти, блок задания кода величины фазового шага, формирователь импульсов И дешифратор, выход которого соединен с первым входом комму 1 гатора, первый выход которого соединен с входом синхронизации регистра памяти, выходы которого соединены с соответствующими:информационными входами регистра сдвига с логической обратной связью, выходы которого соединены с входами дешифратора и с информационными входами регистра памяти,первый установочный вход которого соединен с вторым выходом коммУтатора, второй вход которого соединен с первым входом формирователя импульсов и выходом блока сравнения, первая группа входов которого соединена с соответствующими выходами разрядов счетчика импульсов, .вход синхронизации которого соединен с выходом генератора тактовых импульсов, входом блока на 73 б 2 чальной установки, первым входомтриггера, первым входом разрешенияблока сравнения и входомсинхрониэции регистра сдвига с логической 5 обратной связью, управляющий вход ьторого соединен с выходом триггера,второй вход которого соединен с вторым входом формирователя импульсов 10и выходом переполнения счетчика импульсов, установочный вход которогосоединен с выходом блока начальнойустановки и вторым установочнымвходом регистра памяти, выходы блока задания кода величины фазового шага соединены с соответствующими входами второй группы входов блока сравнения, второй вход разрешения которого соединен с выходом формироваттеля импульсов.20 2. Генератор по п. 1, о т л и -ч а ю щ и й с я тем, что Формирователь импульсов содержит первый и второй 0-триггеры и элемент НЕ, выход .которого соединен с входом синхронизации второго Э-триггера, инверсныйвыход которого соединен с установочным входом первого П-триггера, входсинхронизации которого является пер вым входом формирователя импульсов,вторым входом которого является входэлемента НЕ, а выходом - выход первого В-триггера, соединенный с установочным входом второго Э-триггера. оставитель И.Бурмистехред А.Кравчук Корректор М,Пароши дактор М.Петров Подписнокомитета СССРи открытийушская наб., д, 4/5 Заказ 6 оиэводственно-полиграфическое предп 5 Тираж 816НИИПИ Государственного по делам изобретений 3035, Москва, Ж, Р г,ужгород, ул.Проектная,

СмотретьЗаявка

3895225, 13.05.1985

ГОРЬКОВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ НАУЧНО ИССЛЕДОВАТЕЛЬСКИЙ РАДИОФИЗИЧЕСКИЙ ИНСТИТУТ

КАРАКУШЬЯН АЛЕКСАНДР ГРИГОРЬЕВИЧ, СЕДУНОВ НИКОЛАЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: генератор, импульсов, последовательности, псевдослучайной

Опубликовано: 15.12.1986

Код ссылки

<a href="https://patents.su/4-1277362-generator-psevdosluchajjnojj-posledovatelnosti-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор псевдослучайной последовательности импульсов</a>

Предыдущий патент: Формирователь пачек импульсов для электростимулятора дыхания

Следующий патент: Генератор линейно-частотно-модулированных сигналов

Случайный патент: Способ изготовления чугунной тормозной колодки