Устройство для деления чисел в интервально-модулярном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1241240

Автор: Коляда

Текст

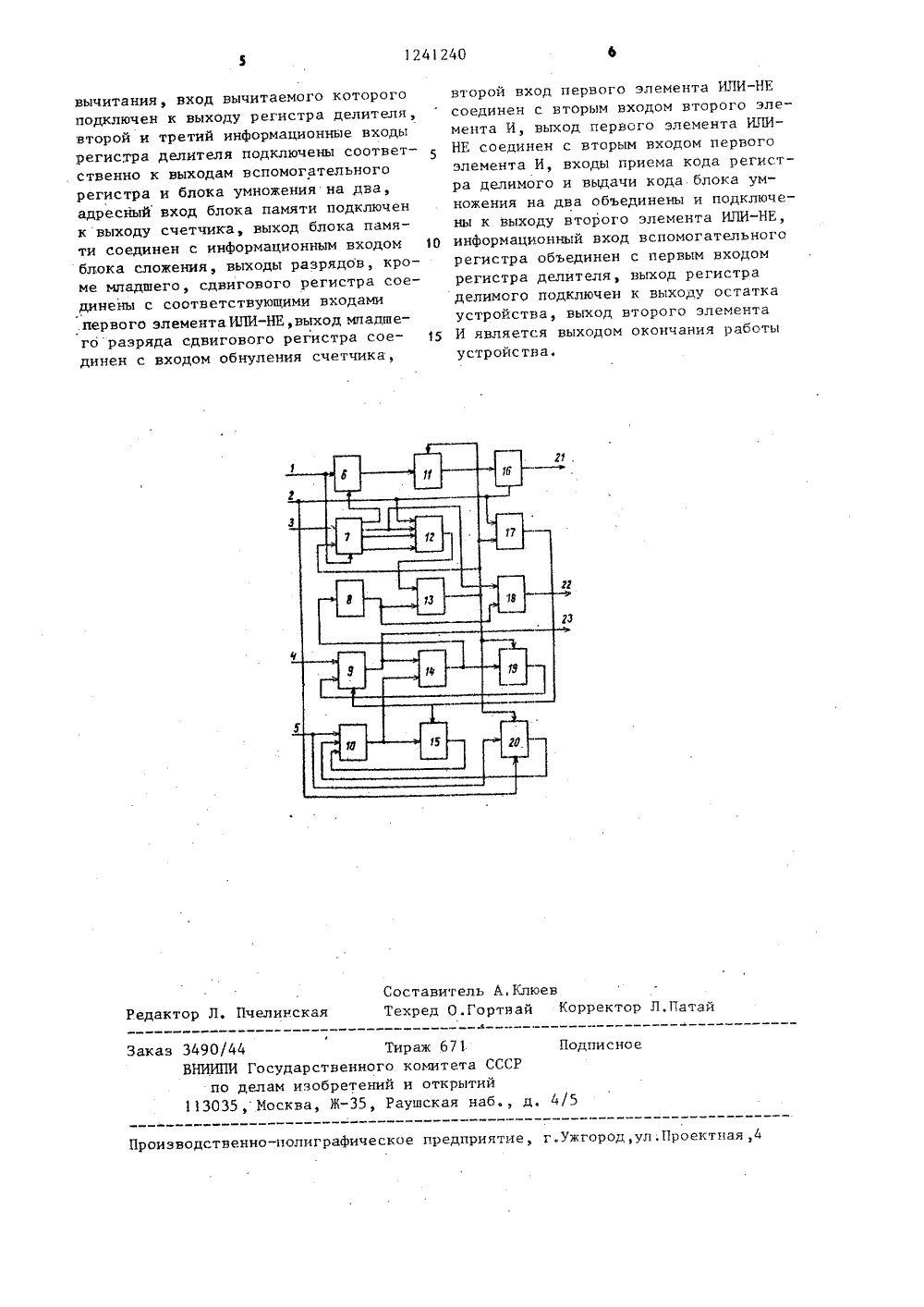

СОЮЗ СОВЕТСН(ИХСОЦИАЛИСТИЧЕСНИРЕСПУБЛИН 19) 111) 1) 4 С 06 Р 7/7 ОЮЗЯМ ИСАНИЕ ИЗОБРЕТЕНИЯ ДЕЛЕНИЯ ЧИСЕЛ ВНОМ КОДЕ(54) УСТРОЙСТВО ДЛ ИНТЕРВАЛЬНО-МОДУЛЯ (57) Изобретение лительной технике пользовано в ариф ствах непозиционн относится к и может быт ч исетически роиыполо типа для в ения чисел, пред- вально-модулярной ния операции д авленных в инт Ю ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВ(71) Научно-исследовательский институт прикладных физических проблемим. А.Н.Савченко(56) Авторское свидетельство СССР9 398949, кл. С 06 Р 7/72, 1971,Авторское свидетельство СССРУ 579614, кл. С 06 Р 7/72, 1975. системе счисления. Цель изобретения - уменьшение количества оборудования устройства, Поставленная цель достигается за счет реализации итерационного алгоритма, базирующегося на операциях умножения на два, деления и формирования знака числа в интервально-модулярном коде. Поставленная цель достигается тем, что устройство для деления чисел в интервально-модулярном коде, содержащее блоки сложения, вычитания и умножения, два элемента ИЛИ-НЕ, содержит счетчик, сдвиговый регистр, блок памяти, блок формирования знака, два элемента И, элемент задержки и вспо- ф могательный регистр с соответствующими связями. Устройство также может быть использовано в специализированных вычислительных устройствах, реализующих вторичную обработку дискретных сигналов в системах различного назначения. 1 ил, 12412401Изобретение относится к вычислительной технике и может быть исполь-зовано в арифметических устройствахнепозиционного типа для выполненияоперации деления чисел представленных в интервально-модулярной системесчисления.Цель изобретения - сокращение количества оборудования.Начертеже приведена структурнаясхема устройства для" деления чисел винтервально-модулярном кодеУстройство Для деления чисел винтервально-модулярном коде содержиттактовый вход 1 устройства, первый 2и второй 3 установочные входы устройства, вход 4 делимого устройства,вход 5 делителя устройства, счетчикб, сдвиговый регистр 7, блок 8 формирования знака, регистр 9 делимого,регистр 1 О делителя, блок 11 памяти,первый элемент ИЛИ-НЕ 12, первыйэлемент И 13, блок 14 вычитания,блок 15 умножения на два, блок 16сложения, второй элемент ИЛИ-НЕ 17,второй элемент И 18, элемент 19 задержки, вспомогательный регистр 20,выход 21 частного устройства, выход22 окончания работы устройства и выход 23 остатка устройства,Блоки 16 и 14 представляют собойизвестные устройства для суммирования чисел в интервально-модулярнойсистеме счисления, блок 8 формирования знака - известное устройствоконвейерного типафИз блока 11 памяти по адресу 1считывается интервально-модулярныйкод константы 2".Сдвиговый регистр 7 реализуетсдвиг на один разряд вправо н имеетразрядность (Т+4), где Т - целаячасть 1 оя К; К - число оснований интервально-модулярной системы.Элемент 19 задержки представляет собой цепочку из (Т+3) регистров, вход первого из которых является входом элемента задержки, выход последнего - выходом элемента задержки,Устройство для деления чисел в интервально-модулярном коде работает следующим образом.По сигналу, подаваемому на первый установочный вход 2 устройства, блок 16 сложения приводится в исходное состояние, на выходах элементов И 13 и ИЛИ-НЕ 17 вырабатываются сигналы Г, =0 и Г =О, которые, поступая с вы 50 На (1+1)-м такте операции (7) 0)на входы блока 8 формирования знака .и элемента 19 задержки поступаетразность К =А-В, а в регистре 10получают произведение В, = 2 В, Поокончании (Т+3) -го такта на выходеблока 8 получают знак Б разностиоЕа ее интервально-модулярный кодпоявляется на выходе элемента 19 за 5 10 5 го 25 30 35 40 45 ходов элементов 13 и 17 на входы управления выдачей кода блока 11 памяти элемента 19 задержки, вспомогательного регистра 20 и блока 15 умножения на два соответственно блокируют поступление с их выходов ненулевой информации. В регистр 9 делимогочерез вход 4 устройства передаетсяинтервально-модулярный код (Кл-13(А делимого А, в регистр10 делителя и вспомогательный регистр20 через информационный вход 5 устройства передается интервально-модулярный код ( Р 1, / , .,1(Вделителя В (А Ъ О, В ) О) а в сдвиговый регистр 7 через второй установочный вход 3 устройства записываетг+зся двоичный код числа 2 . Послеэтого начинается выполнение операцииделения,На первом такте операции интервально-модулярный код делимого А свыхода регистра 9 подается на пер-вый вход блока 14 вычитания, а интервально-модуля:рный кодделителя Вс выхода регистра 10 поступает навторой вход блока 14 и вход блока 15умножения на два, Блок 14 вычитаниянаходит разность К =А.-В, интервально-модулярный код которой попадает вблок 8 Формирования знака и элемент 19задержки, а блок 1 5 умножения на дваполучает произведение В =2 В, интервально-модулярный код которого свыхода блока 15 передается в регистр.10 через третий его вход. На данномтакте сигналы Г, и Г принимают значения "0" и "1" соответственно,На каждом такте работы устройствапо сигналу, подаваемому на тактовыйвход 1 устройства, содержимое. счетчика 6 увеличивается на единицу, асодержимое регистра 7 сдвигается наодин бит вправо при этом выдвинутоезначение о нулевого разряда подаетося на вход обнуления счетчика 6, ус-танавливая его в нулевое состояние,если б :=1. В первый раз это произойдет на (Т+4)-м такте.з 1241держки. Если Б=1 (АВ), то на выходе элемента И 18 и соответственнона выходе 22 устройства по входнымвеличинам б, =1 и Б =1, поступающимсоответственно на первый и второй5входы с выходов первого разряда сдвигового регистра 7 и Формирователя 8знака числа соответственно, формируется единичный сигнал, указывающийна то, что процесс деления чисел А и 0В завершен, Частное Я=О и остатокК =А снимаются с выходов 21 и 23 уст. оройства и на этом работа устройствазаканчивается. Если Б=О(АВ),то описанные выше действия повторяют ся. На (Т+4)-м такте содержимоеб =1нулевого разряда сдвигового регистра7 поступает на вход обнуления счетчика 6, устанавливая его в нулевоесостояние, а на (Т+1+3)-м такте на . бвыходе блока 8 и элемента 19 задержки появляются соответственно знакБ и интервально-модулярный код числа К. Предположим, что при некотором 2= Ч+1 (Ч . 1) на выходе блока 8 25появится единичный сигнал Б =1,У+1соответствующий разности КО,Тогда, В силу того, чтОб, = б,= б, =О, на выходе элементаИ 13 формируется единичный сигнал 30Г, =1, который поступает в старший(Т+3)-й разряд сдвигового регистра 7,. на второй вход элемента ИЛИ-НЕ 17 ивходы управления выдачей кода блока11 памяти, элемента 19 задержки ивспомогательного регистра 20. Из блока 11 памяти по адресу Ч, полученномук этому времени в счетчике 6, считывается интервально-модулярный кодконстанты 2"., который подается навход блока 16 сложения, осуществляющего накопление частного Я. На выходе элемента ИЛИ-НЕ 17 вырабатывается сигнал Г =О, который, поступая навход управления выдачей кода блока15 умножения на два, блокирует поступление с его выхода ненулевой информации, в регистр 10 из вспомогательного регистра 20 передается интервально-модулярный код делителя В,а в регистр 9 делимого с выхода элемента 19 задержки поступает интервально-модулярный код разности КНа этом заканчивается первая итерация реализуемого алгоритма деления.В дальнейшем описанный процесс функционирования устройства повторяется до тех пор, пока на выходе эле 240 4мента И 18 не появится единичный сигнал, Это случится после добавления в блоке 16 сложения к накапливаемой сумме младшего члена двоичного представления частного Я. Интервальномодулярные коды частного Ц и остатка К от деления снимаются соответственно с. выходов 21 и 23 устройства, на этом работа устройства заканчивается.Формула изобретенияУстройство для деления чисел в интервально-модулярном коде, содержащее регистры делимого и делителя, блок сложения, блок вычитания, блок умножения на два и два элемента ИЛИНЕ, причем входы делимого и делителя устройства соединены с первыми инФормационными входами регистров делимого и делителя соответственно, выход регистра делителя соединен с инФормационным входом блока умножения на два, выход блока сложения является выходом частного устройства, о т- л и ч а ю щ е е с я тем, что, с целью сокращения количества оборудования, оно содержит счетчик, сдвиговый регистр, блок памяти, блок формирования знака, два элемента И, элемент задержки и вспомогательный регистр, причем счетный вход счетчика и вход сдвига сдвигового регистра объединены и подключены к тактовому входу устройства, вход обнуления блока сложения, первые входы первого и второго элементов ИЛИ-НЕ и вход приема кода вспомогательного регистра объединены и подключены к первому установочному входу устройства, информационный вход сдвигового регистра является вторым установочным вхо-дом устройства, вход старшего разряда сдвигового регистра, второй вход второго элемента ИЛИ-НЕ, входы выдачи кода блока памяти, элемента задержки и вспомогательного регистра объединены и подключены к выходу первого элемента И, первые входы первого и второго элементов И объединены и подключены к выходу блока формирования знака, вход которого объединен с входом элемента задержки и подключен к выходу блока вычитания, второй информационный вход регистра делимого подключен к выходу элемента задержки, а выход регистра делимого подключен к входу уменьшаемого блока1241240 Составитель А,Клюеведактор Л. Пчелинская Техред О.Гортвай Коррект Патаи Заказ 34 Тираж 671ного комитета СССРений и открытий5, Раушская наб.,Подписно ВНИИПИ Государстве по делам изобре 113035, Москва, Ж 5 еское предприятие, г.ужгород,ул.Проектная,4 зводственно-нол вычитания, вход вычитаемого которогоподключен к выходу регистра делителя,второй и третий информационные входырегистра делителя подключены соответственно к выходам вспомогательногорегистра и блока умножения на два,адресный вход блока памяти подключенк выходу счетчика, выход блока памяти соединен с информационным входом 1 Облока сложения, выходы разрядов, кроме младшего, сдвигового регистра соединены с соответствующими входами.первого элементаИЛИ-НЕ,выход мпадшего разряда сдвигового регистра соединен с входом обнуления счетчика,второй вход первого элемента ИЛИ-НЕсоединен с вторым входом второго элемента И, выход первого элемента ИЛИНЕ соединен с вторым входом первогоэлемента И, вхоцы приема кода регистра делимого и выдачи кода блока умножения на два объединены и подключены к выходу второго элемента ИЛИ-НЕ,информационный вход вспомогательногорегистра объединен с первым входомрегистра делителя, выход регистраделимого подключен к выходу остаткаустройства, выход второго элементаИ является выходом окончания рабстыустройства,

СмотретьЗаявка

3827565, 20.12.1984

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИКЛАДНЫХ ФИЗИЧЕСКИХ ПРОБЛЕМ ИМ. А. Н. СЕВЧЕНКО

КОЛЯДА АНДРЕЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 7/72

Метки: деления, интервально-модулярном, коде, чисел

Опубликовано: 30.06.1986

Код ссылки

<a href="https://patents.su/4-1241240-ustrojjstvo-dlya-deleniya-chisel-v-intervalno-modulyarnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для деления чисел в интервально-модулярном коде</a>

Предыдущий патент: Стохастический преобразователь

Следующий патент: Микропрограммное устройство управления

Случайный патент: Газомазутная горелка