Преобразователь перемещения в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1236611

Авторы: Гольденштейн, Коган

Текст

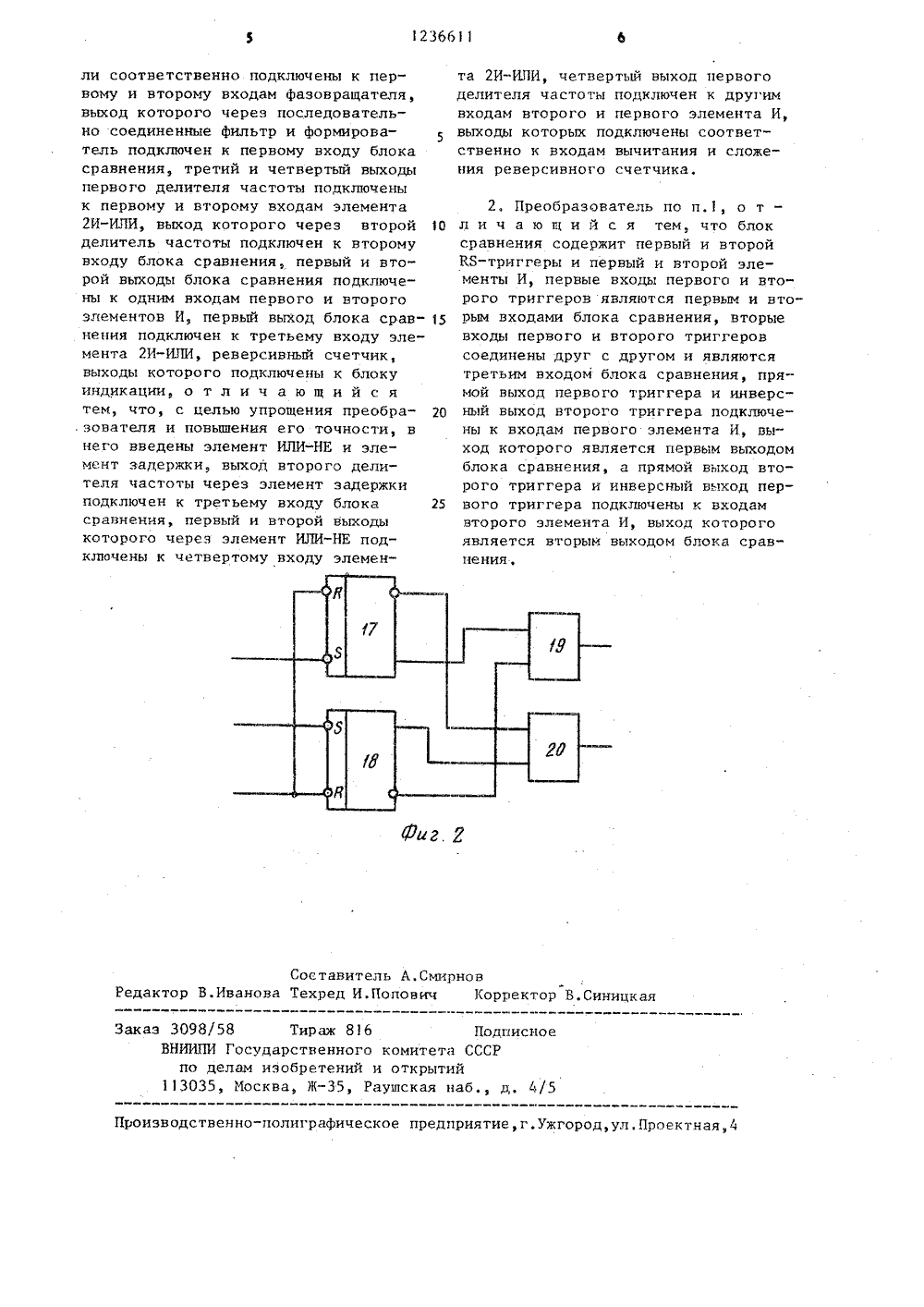

, 1236611 5114 Н 03 ОПИСАНИЕ ИЗОБРЕТЕНИ СВИДЕТЕЛ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское свидетельство СССР В 030824, кл, С 08 С 9/00, 1982,Авторское свидетельство СССР У 561208, кл, С 08 С 9/00, 1976.(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью упрощения и повьвпения точности преобразователя фазовращатель 5 эапитывается сигналом генератора 1 через делитель 2 частоты и усилители 3, 4, Из выходного сигнала фазовращателя 5 Формирователь 7 вырабатыва"ет импульс, поступающий на первыйвход блока 8 сравнения. Блок 8 в совокупности с элементом ИЛИ-НЕ 16,элементом 2 И-ИЛИ 10, делителем 11частоты и элементом 15 задержки образуют Фазоимпульсную следящую системуИа выходах блока 8 Формируются импульсные сигналы, длительность которых равна относительному временномусдвигу сигналов с формирователя 7 иделителя 11 частоты, Выходные сигналы блока 8 открывают элементы И 9или 12, на другие входы которых поступают импульсы с промежуточного выхода делителя 2. Выходные импульсыэлементов И 9 и 12 поступают соответственно на входы сложения и вы"читания реверсивного счетчика 13,где Формируется код перемещения смомента начала измерения. 1 э.п.ф-лы, 2 ил.Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством, 5Цельюизобретения является упрощение преобразователя и повышениеего точности при реверсивном перемещении.На фиг.1 представлена структурнаясхема преобразователя перемещения вкод; на фиг.2 - структурная схемаблока сравнения.Преобразователь перемещения в код(фиг.1) содержит генератор 1 импульсов, первый делитель 2 частоты, уси -лители 3 и 4, фазовращатель 5, фильтр6, формирователь 7, блок 8 сравнения,первый элемент И 9, элемент 2 И-ИЛИ Овторой делитель 11 частоты, второйэлемент И 12, реверсивный счетчик 13,блок 1 ч индикации, элемент 15 задержки, элемент ИЛИ-НЕ 16,Блок 8 сравнения (фиг,2) содержит25первый 17 и второй 18 триггеры, первый 19 и второй 20 элементы И.Преобразователь перемещения в кодработает следующим образом.С генератора 1 импульсы поступают на вход делителя 2 частоты, напервом и втором выходах которого формируются сдвинутые между собой начетверть периода импульсные последовательности в виде меандра. Зти импульсные последовательности через 35импульсные усилители 3 и 4 поступаютна синусно-косинусные входы фазовращателя 5. Перемещение ротора фазовращателя 5 относительно статора определяют на выходе фазовращателя фазу первой гармоники, которая выделяется фильтром 6 нижних частот идалее в формирователе 7 вырабатываетсл импульс в момент перехода синусоидь через ноль. Зтот импульс, временное положение (фаза) которого определено положением ротора фазовращателя 5, поступает на первый входблока 8 сравнения. Блок 8 в совокупности с элементом ИЛИ-НЕ 16, эле Оментом 2 И-ИЛИ 1 О, делителем 11 частоты, элементом 15 задержки образуютфазоимпульсную следящую систему(ФИСС). На выходах блока 8 формиру -ются импульсные сигналы, длительность 55которых равна относительному временному сдвигу двух входных сигналов,поступающих на его первый и второй входы. Если первым приходит импульс на первьй вход, то сигнал формируется на первом выходе, если наоборот, то - на втором, При одновременном приходе импульсов сигналы не формируются. В исходное состояние блок 8 приводится импульсом с выхода делителя 11 частоты, задержанным элементом 15.При работе ФИСС возможны следующиеслучаи.Случай 1, Сигналы на первый и второй входы блока 8 приходят одновременно. На выходах блока 8 сигналы бу - дут отсутствовать. При этом элементом 6 разрешается прохождение импульсов с третьего выхода делителя 2 частоты через элемент 2 И-ИЛИ 1 О на вход делителя 11 частоты. Его коэффициент деления выбран таким, что при поступлении на вход импульсов с третьего выхода делителя 2 частотычастота следования выходных импульсов делителя 11 равна частоте следования входных сигналов фазовращателя 5. Следовательно, при отсутствии перемещения ротора фазовращателя 5 сигналы на первый и второй входы блока 8 будут приходить в одной фазе. Поскольку на выходах блока 8 сигналов нет то через элементы 9 и 12 на входы реверсивного счетчика 13 импульсы не поступают. Через время, равное примерно половине периода выходного сигнала делителя 11, блок 8 сбрасывается сигналом с элемента 15 задержки и тем самым подготавливается к работе в следующем периоде.Случай 2, При перемещении ротора фазовращателя 5 сигнал на первый вход блока 8 приходит позже, чем появится сигнал на его втором входе. В этом случае на втором выходе блока 8 появится сигнал, который через элемент ИЛИ-НЕ 16 запретит прохождение на вход делителя 11 частоты импульсов с третьего выхода делителями 2 частоты. Через элемент И 12 разрешается прохождение этих импульсов удвоенной частоты с четвертого выхода делителя 2 на вычитающий вход реверсивного счетчика 13. С приходом сигнала на первый вход блока 8 на его втором вьходе сигнал исчезнет, а затем он будет сброшен сигналом с выхода элемента 15 задержки. В дальнейшем ФИСС работает аналогично слу- чаюО Поскольку на вход делителя 11 частоты импульсы не поступали до прихода импульса с выхода формирователя 7, то после прихода последнего фазы сигналов на выходе формирователя 7 5 и ФИСС вновь будут совпадать. Количество импульсов, поступающих на вход счетчика 13, определяется величиной разности фаз между импульсами с ФИСС и формирователя 7.Случай 3. При перемещении ротора фазовращателя 5 в противоположном направлении сигнал приходит на первый вход блока 8 раньше, чем появится сигнал на его втором входе. 5 В этом случае на первом выходе блока 8 появится сигнал, разрешающий прохождение через элемент 2 И-ИЛИ 1 О на вход делителя 11 импульсов удвоенной частоты с четвертого выхода де лителя 2, Тот же сигнал запрещает через элемент ИЛИ-НЕ 6 прохождение импульсов с третьего выхода делителя 2 частоты. Одновременно через элемент И 9 импульсы удвоенной частоты с четвертого выхода. делителя 2 частоты поступают на суммирующий вход реверсивного счетчика 13. С приходом сигнала на второй вход блока 8 на его первом выходе сигнал исчезнет, 30Фа затем он будет сброшен сигналом с выхода элемента 15 задержки. После этого ФИСС работает аналогично случаюВ рассмотренных случаях 2 и 3 фа эа сигнала на выходе делителя 11 частоты приравнивается к фазе сигнала формирователя 7. Так как реверсивный счетчик 13 подсчитывает количество импульсов, необходимых для 40 сдвига фазы сигнала на выходе делителя 11 частоты, то результат измерения при одинаковых перемещениях, Фазовращателя 5 в противоположных направлениях одинаков. Результат, за фиксированный в реверсивном счетчике 13, выводится на блок 14 индикации,Случай 4. На выходе формирователя 7 отсутствует очередной сигнал, 50 Это может быть результатом действия помехи, которая находится в фазовращателе 5 или в соединительном кабеле между фазовращателем 5 и фильтром 6 нижних частот. Имея сложный спектр 55 и высокий уровень, помеха может пройти через фильтр 6 нижних частот и внести формирователь 7 в насыщение. В этом случае полезный сигнал не пройдет на второй вход блока 8. ФИСС начинает работать как в случае 2 с тем отличием, что измерение осуществляется с момента поступления импчльса на второй вход блока 8 до моментаего сброса в исходное состояние импульсом с элемента 15 задержки, Величина задержки определяет максимально возможный сдвиг Фазы сигнала на выходе делителя 11 частоты за один период Т входного сигнала фазовращателя 5. А так как величина задержки меньше одного периода Т, то по окончанию действия помехи и с появлением сигнала с выхода формирователя 7 ФИСС отработает Фазу сигнала на вы - ходе делителя 1 частоты в обратном направлении, при этом число в ревер- сивном счетчике 13 восстановится до значения, предшествовавшего наступлению случая 4. Таким образом на величину задержки элемента 15 задержки накладываются следующие условия. Уменьшение величины задержки позволяет восстановить правильность показаний индикации по истечению случая 4, повторившегося в нескольких периодах входного сигнала Фазовращателя 5 подряд. В то же время зта величина не должна быть меньше максимально возможного сдвига Фазы сигнала с выхода Формирователя 7 за один период Т. После включения питания в преобразователе перемещения в код возникает переходный процесс, по окончанию которого фазы сигналов на первом и втором входах блока 8 совпадают, т,.е. синхронизируется положение сигналов на выходах формирователя 7 и делителя 11 частоты. Уста - новка преобразователя перемещения в код в исходное состояние осуществляется после завершения переходного процесса путем установки в нуль только реверсивного счетчика 13, либо путем записи в него значения исходного положения фазовращателя 5 (не показано).Формула изобретения1. Преобразователь перемещения в код, содержащий генератор импульсов, выход которого подключен к входу первого делителя частоты, первый и второй выходы первого делителя частоты через первый и второй усилитеакаэ 3098/58 Тираж 8 ВНИИПИ Государственно по делам изобретени 113035, Москва, Ж, 6 Подписноо комитета СССРи открытийРаушская наб., д. / Проектная,4 роиэводственно-полиграфическое предприятие,г.ужгор ли соответственно подключены к первому и второму входам фазовращателя,выход которого через последовательно соединенные фильтр и формирователь подключен к первому входу блокасравнения, третий и четвертый выходыпервого делителя частоты подключенык первому и второму входам элемента2 И-ИЛИ, выход которого через второйделитель частоты подключен к второмувходу блока сравнения, первый и второй выходы блока сравнения подключены к одним входам первого и второгоэлементов И, первый выход блока сравнения подключен к третьему входу элемента 2 И-ИЛИ, реверсивный счетчик,выходы которого подключены к блокуиндикации, о т л и ч а ю щ н й с ятем, что, с целью упрощения преобра.зователя и повышения его точности, внего введены элемент ИЛИ-НЕ и элемент задержки, выход второго делителя частоты через элемент задержкиподключен к третьему входу блокасравнения, первый и второй выходыкоторого через элемент ИЛИ-НЕ подключены к четвертому входу элемента 2 И-ИЛИ, четвертый выход первого делителя частоты подключен к другим входам второго и первого элемента И, 5 выходы которых подключены соответственно к входам вычитания и сложения реверсивного счетчика. 2. Преобразователь по п.1, о т 10 л н ч а ю щ и й с я тем, что блоксравнения содержит первый и второйКБ-триггеры и первый и второй элементы И, первые входы первого и второго триггеров являются первым и вторым входами блока сравнения, вторыевходы первого и второго триггеровсоединены друг с другом и являютсятретьим входом блока сравнения, прямой выход первого триггера и инверс ный выход второго триггера подключены к входам первого элемента И, выход которого является первым выходомблока сравнения, а прямой выход второго триггера и инверсный выход пер ного триггера подключены к входамвторого элемента И, выход которогоявляется вторым выходом блока сравнения,

СмотретьЗаявка

3784226, 25.08.1984

ПРЕДПРИЯТИЕ ПЯ В-2817

КОГАН ВЛАДИМИР АРОНОВИЧ, ГОЛЬДЕНШТЕЙН ЯНИ ХУНОВИЧ, КОГАН ЕВГЕНИЙ ГРИГОРЬЕВИЧ

МПК / Метки

МПК: H03M 1/46

Метки: код, перемещения

Опубликовано: 07.06.1986

Код ссылки

<a href="https://patents.su/4-1236611-preobrazovatel-peremeshheniya-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь перемещения в код</a>

Предыдущий патент: Преобразователь угла поворота вала в код

Следующий патент: Измеритель времени установления выходного напряжения цифроаналоговых преобразователей

Случайный патент: Установка для испытания смазочных масел на лакообразование и пригорание поршневых колец