Микропроцессорная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

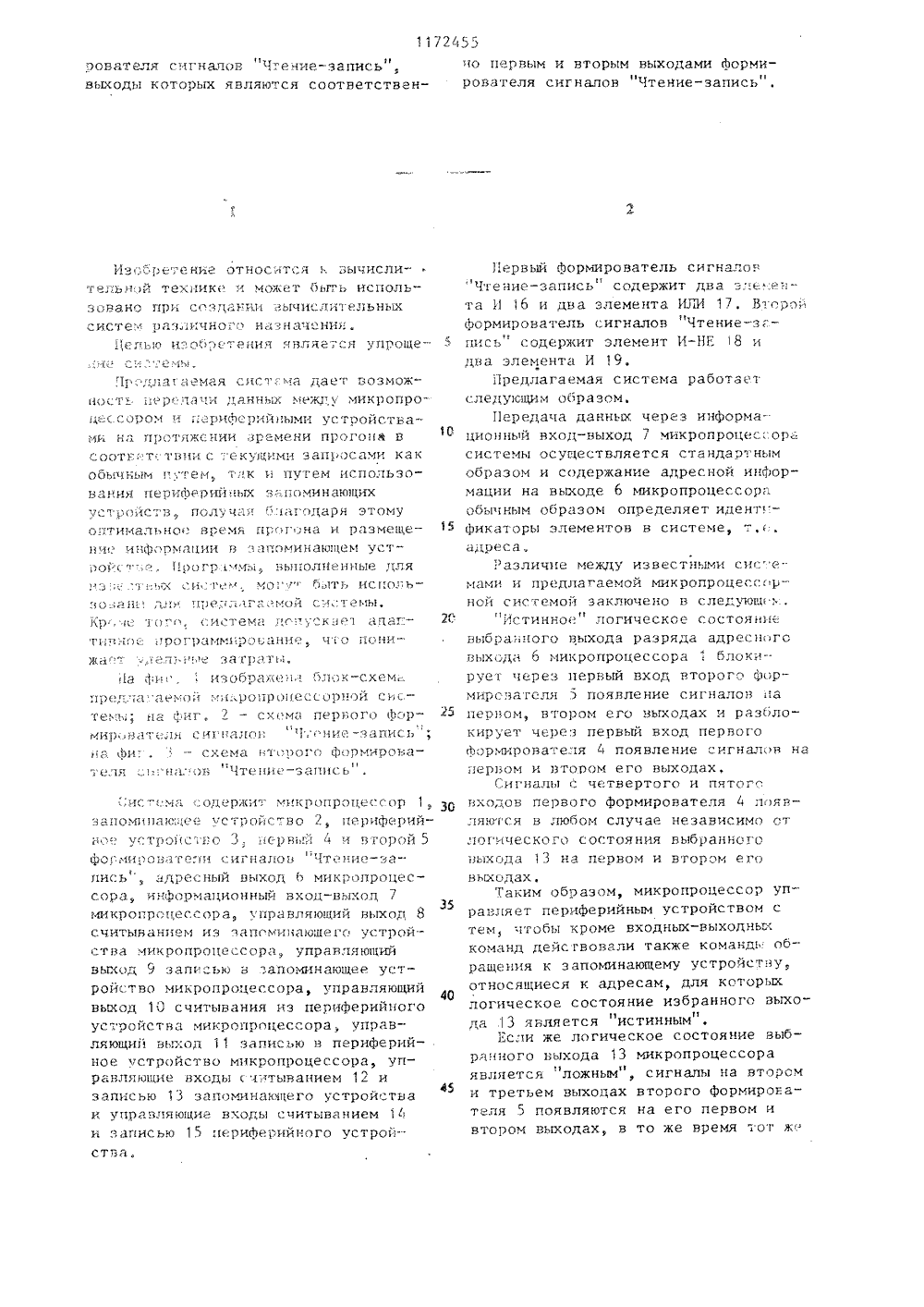

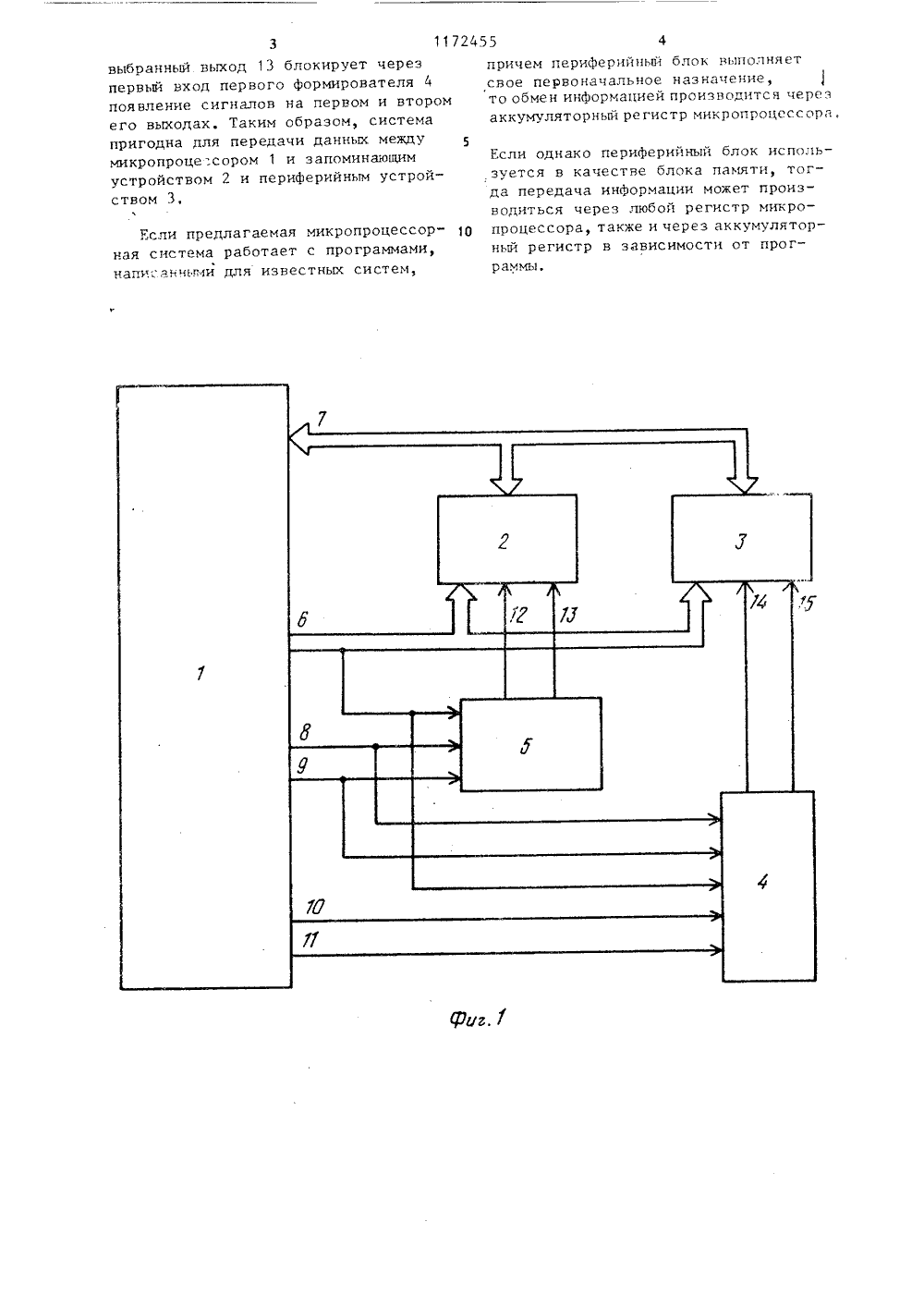

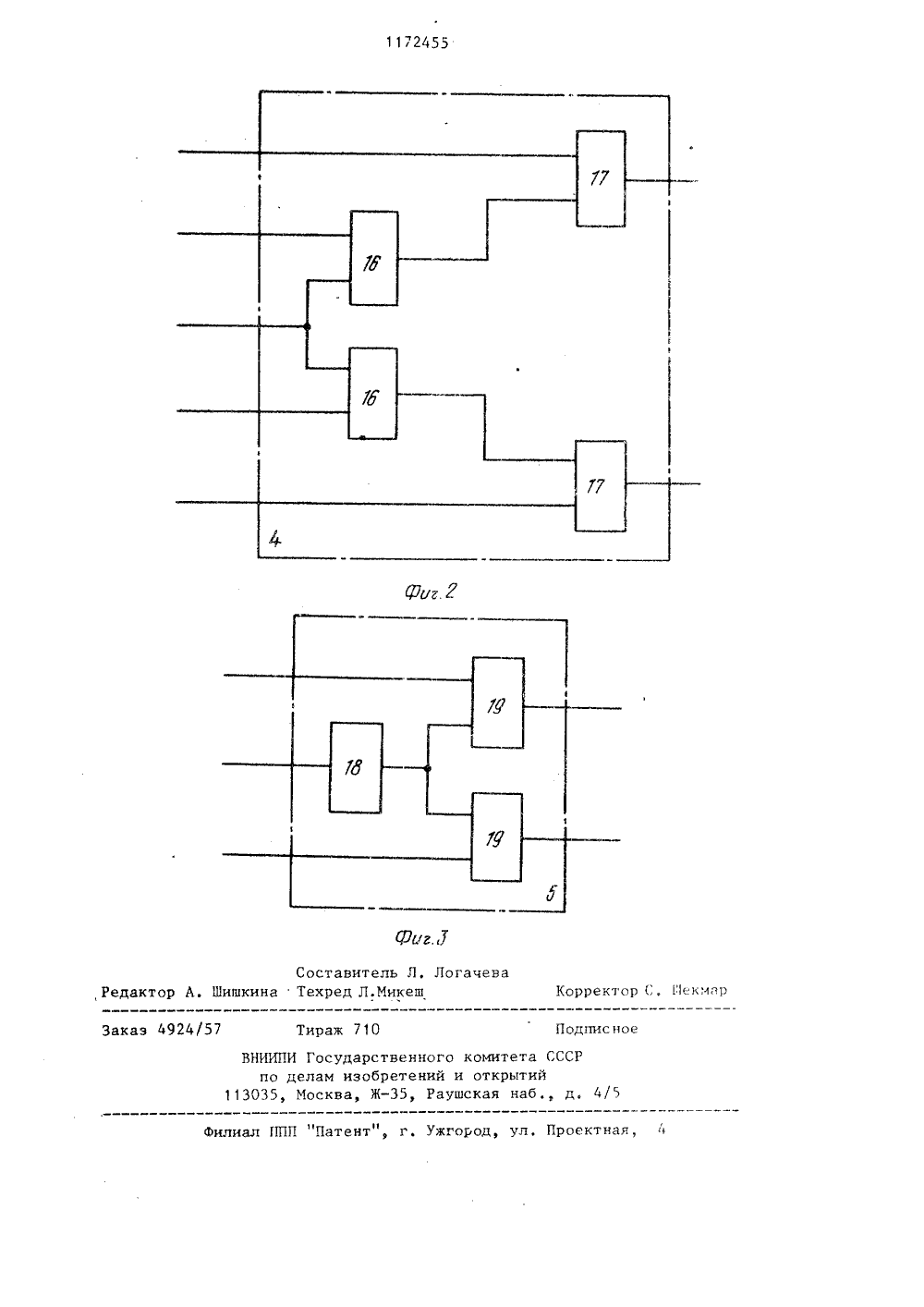

(46) 07 (72) Ив и, 3 нд Аттила аши Г к Кермецди,за Молнар,ер, Лайош) ъюлаштван СилардТакач иТМи нгишнили микро-ЭВМ,33-38, праце гия ,выо устроистн периферии а ю сц а я ль с я тем, что, сца содержит первыатели сигналов Ч й и вт тениесигнала управения, рой фармиро запись , к о, в,с Чтение И-НЕ и апись" сода элемента элементичем первый ерньм входам кото о выход разряда адресн роцессора, упранлнанем и записью апомицающего уст цн цн сны саатнетстьивходам перво поключец ныхоЛа микрос ход нта Чтециерого формир запись чер н к нателя сигцала з элемент И-НЕ я ньходы сит фериицог. и которого ;то. вторымтр подключ второго первым ентов нха км первого и торым входа ойст ен г АРСТВЕННЫЙ НОМИТЕТ СССР М ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ГИСАНИЕ ИЗ с. рис, 1-4, 1-9.Руководство для пользования микрокомпьютерными системами ИНТЕЛ 8080, 1975, т. 9, с, 3-8, рис. 3-9.(54)(57) МИКРО 1 РОЦЕССОРНАЯ СИСТЕМА, содержащая микропроцессор, запоминающее устройство и периферийное устройство, причем информационные входы-выходы запоминающего и периферийного устройств через информационную шинч соединены с информационным вхопомходом микрс компрессора, адресный вь- ход которого соединен через адресную шину с адресными входами запоминающег второго формирователей сгнала "Чтение-запись", управляющис ныхалы считыванием и записьюаг.омицаюцего устройства микропроцесссара подкла - чены соотнетстне.на к четгс р и пятому входам первого фармир гинтс:я сигналов Чтение-за лис ь, перй и второй выходы которого падключ соответственна к упранлянгщим входам счигынанием и записью периферий,. го устройства, перньсй и тарой ныхас; второго формирователя сиггслонЧтение - запись падь лнгены ссотнст - стзеца к управля оцим входам считыванием и записью запомицанцега устройства, первый ф;рьиронатсл с игцалов "Чтение-загинь содержит дна элемента И и дна элемента 1 И, г.ричем перньги вход первого формиронате:1 я сиг -11налан Чтение-завис подключен к первым входам первого и нторагс элементов И, выходы которых подклю - чены соответственно к вторым входам первого и второго элементов ИЛИ, вторые входы которых и вторые входы первого и второго элементов И падклн,ецы соответственно к второму, третьему, четвертому и пятому входам первого формирователя сигцалонЧте - ние-запись, перы и второй выходы которого являются выходами первого и второго элементов И.;П соатнетстненцрой формировательв которых подклкчець соответственновторой и третий входы второго форм,ние-загИс.ь ", Го формировались рователя сигналов Чтение-записьВыходы которых являются соатВетственИзобретение относится к зычисли 1 Е.;1 ЬН тй ТЕХ 1 ИК. И МОЖЕТ ОЬГГЬ ИСПОЛЬ 3 СваНО ПР Савла . и ВЫЧИСЛИ 1 Е тЬ 11 ЫХ С ИС Т Е:% 1";.1,1 ИЧ Н 0 Г а Н т 1 З Н аЧ" НИЭ 1.,ЕЛ 1 О ИЗОГ ЕТЕНИЯ ЯВЛЯЕТСЯ УПРОЩЕк: :,:." мы, П 1".1 а 1 ЕМВЯ С 1 СТ: т":а Давт ВОЗМОЖН 1 СтЬ;.ЕР.:Ла ти ттаННЬХ: ЕЖДУ МИКРОПРО,";ссорам и .Рифарийными устаойстьами на 111)атяжснии времени праг 011 й В соотв;.т.твин с текущими запросами как обычным г;тем тк и путем использованин периферийных запоминающих.,СТРС 1 йСТВ. ПОЛуЧя б:1 рыцаря ЭтОМуЭ:тти 11 аЛЬНО. ВРЕМЯ ПРГ Эяа И РаЗМЕШЕ -НЧЕ ИнфГ 1 ЦИИ В :11 тгтИНаЮ 1 ЦЕМ .ЧСТ 01,. Рагр:1 мь 1, ВЬН 1 оляенпые для. э ;: Ьх си: г;., мо 1 г быть исполь.О 111: Г 1 т 1;Е;: 1 га 1 ой СИ,.ТЕ 11 Ь 1,1 ттр,т О Г О, С И . Т Е МД Ст т Г С К З Е З П аг. тил ноРо Граь 1 м 1 ра вани, чО псз ни" Ж 1 т, т Г т, тт,э З1 рт 1,1 :а фи,изобраьстн,. блок-схем,прс.ч ,1 ае 1 с 1 й 1,рапр 01 етеьъ,: на фнг, 2 - схематМИР ВТЕЛЯ С 11111 О 1на фи 1, ; схема нОроеля; т. н: ов Чтени - з.:ис-а;,1 . одержит мт 1 кропроцессор 1, Зо залами пас:ее 1 с тр ой с "в о 2.нерифегий- О:. туат 1 тто 11 СТ 11 О 3, 1 ЕрнЬГП 1 и ВТОРСй 5 фар миро натгт и сигнало 11 ЧттНие за лись адрссный Бьход б миктрапрацес - соРа, информационный вход-выход 735 жкропро 11 ессора, управляющий выход 8 считыванием из заг 1 еминающегс. устройства микропроцессор, управляющий выход 9 записью в запоминающее устройс.тво микропроцессора, управляющий4 О выход 10 считывания из периферийного устройства микропроцессора, управляющий Выход 11 записью в периферийное устройства микропроцессора, управляющие входы с ч .тыванием 12 и45 записью 13 запоминающего устройства к уг 1 разляющие входы считыванием 11 и записью 15 периферийного устрой-. ства. но первым и вторым выходами формирователя сигналов Чтение-запись Первый формирователь сигналовЧтение-записьсодержит два эс;ее- -та И 16 и два элемента ИЛИ 17, Второ:.формирователь сигналов "Чтение-з; -письсодержит элемент И-НЕ 8 идва элемента И 19,Предлагаемая система работает следукщим образом.Передача данных через информационный вход-выход 7 микропроцес: ора системы осуществляется стандартным образом и содержание адресной информации на выходе 6 микропроцессор;. обычным образом определяет идент - фикспоры элементов в системе, т. . адреса.,Различие между известными сис"емами и предлагаемой микропроцесс.срнсй системой заключено в следующ 11тИстинное лоГическое состаЯние ВыораНОГО выхода разряда адресн 1 О выход 6 микропроцессора 1 блокирует через первый вход второго ф рмирс.зателя 5 появление сигналов 1 а первом, втором его вьгходах л разблокирует через первый вход первого формировате.:1 я Й появление сигналов на первом и втором его выходах,Сигналы с четвертого и пятсговходов первого формирователя 4 и являются в любом случае независимо Отлогического состояния выбранноговыхода 13 на первом и втором еговыходах.Таким образом, микропроцессор управляет периферийным устройством стем, тобы кроме входных-выходныхкоманд дейс гвовали также комаьдь обращения к запоминающему устройству,относящиеся к адресам, для которыхлогическое состояние избранного выхо тда .13 является истиннымЕс:1 и же логическое состояние выбранного ьыхода 13 микропроцессораявляется ложным", сигналы на второми третьем выходах второго формирователя 5 появляются на его первом ивтором выходах, в то же время тот ж.выбранный выход 13 блокирует черезпервый вход первого формирователя 4появление сигналов на первом и второмего выходах. Таким образом, системапригодна для передачи данных междумикропроце:сором 1 и запоминающимустройством 2 и периферийным устройством 3,Если предлагаемая микропроцессор Оная система работает с программами,напк; анчыми для известных систем,причем периферийный блок выполняет свое первоначальное назначение,то обмен информацией производится через аккумуляторный регистр микропроцсссора,Если однако периферийный блок используется в качестве блока памяти, тогда передача информации может производиться через любой регистр микропроцессора, также и через аккумуляторный регистр в зависимости от программы.1172455 Составитель Л, Логачеватор А. Шишкина Техред Л.Микеш Корре Подпи 71 П "Патент", г. Ужгород,ектная,л каз 4924/57 Т ВНИИПИ Гос по делам13035, Моск арственного комитета СССзобретений и открытийЖ, Раушская наб., д

СмотретьЗаявка

3334252, 16.09.1981

Телефондъяр

ИВАН АДОНЬИ, ЭНДРЕ ФАРКАШ, ДЬЮЛА ХЕГЕДЮШ, АТТИЛА КЕРМЕНДИ, ИШТВАННЕ МОДЬОРОШИ, ГЕЗА МОЛНАР, СИЛАРД ШАШ, ЛАСЛО ШЕЛЛЕР, ЛАЙОШ ТАКАЧ, ДЬЕРДЬ ВИТЕЗ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессорная

Опубликовано: 07.08.1985

Код ссылки

<a href="https://patents.su/4-1172455-mikroprocessornaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессорная система</a>

Предыдущий патент: Способ получения бензина

Следующий патент: Система видеотекста

Случайный патент: Способ производства паштета из мяса куриного