Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1159164

Автор: Гладков

Текст

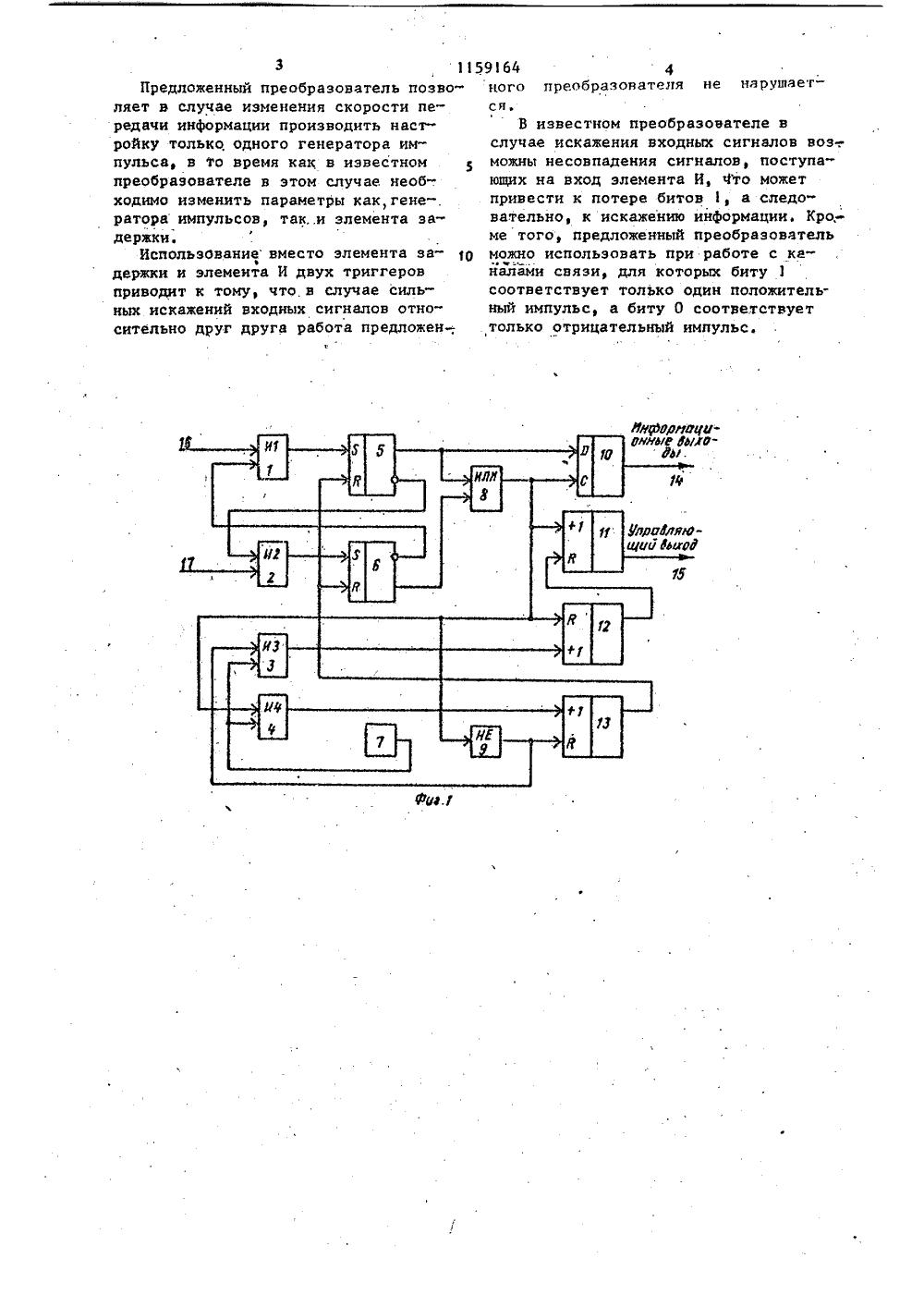

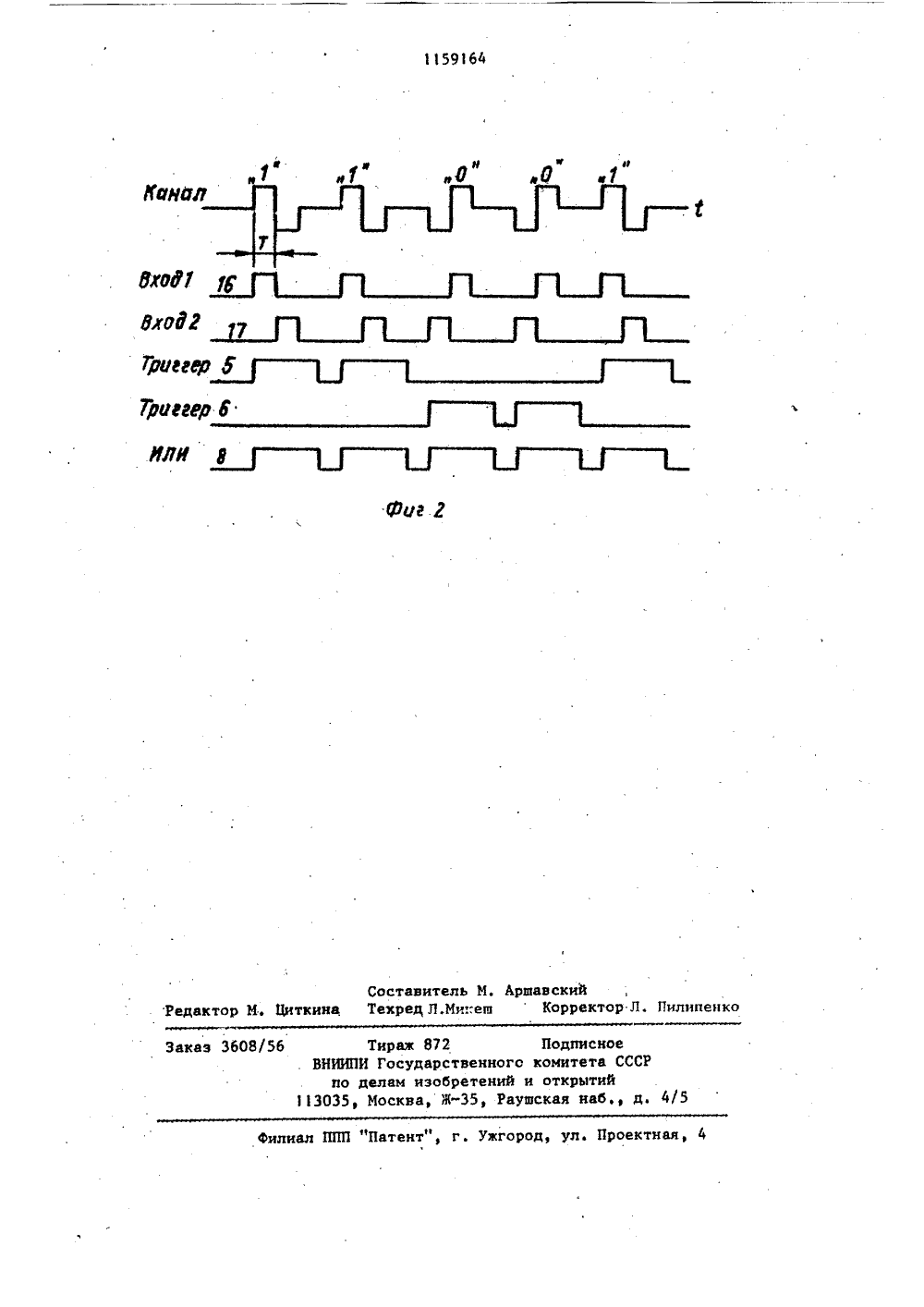

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 164 А 19) (11) П Н 03 М 7/ьО ЯННЫЙ НОМИТЕТ ССС ЗОЬРЕТЕНИЙ И ОТНРЫТ ГОСУДАРС ОО ДЕЛА 1Г гну,гьтт Е ИЗОБРЕТСВИДЕТЕЛЬСТВУ ОРСНОМУ ьство СС 1982. тво СССР 1982.(56) 1, Авторское свидетел СР Р 924 б 96, кл, О Об Р 5/04,2, Авторское свидетельс Р 1045238, кл. Ц Об Р 5/04 (54)(57) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОЛА В ПАРАЛЛЕЛЬНЫЙ, содержащий первый элемент И, генератор импульсов, регистр сдвига, первый и второй счетчики, выход второго счетчика соединен с входом сброса первого счетчика, выход которого явля.ется выхоДом. разрешения считывания преобразователя, информационные выходы которого соединены с выходами регистра сдвига, о т л и ч а ю - щ и й с я тем, что, с целью расширения класса решаемх задач за счет обеспечения возможности преобразования приразличных скоростях передачи данных и при различных формах передаваемых сигналов, в него введены три элемента И, первый и второй триггеры, элемент ИЛИ, злемент НЕ и третий счетчик, выход которого соединен с входами сброса первого и второго триггера, единичныевходы которых соединены с выходамипервого и второго элементов И, первыевходы которых соединены соответствен-.но с инверсными выходами второго ипервого триггеров, единичные выходыкоторых соединены с входами элементаИЛИ, выход которого соединен с син- фхровходами регистра сдвига, со счетным входом первого счетчика, с вхо. дом сброса второго счетчика и с первым входом третьего элемента И, ачерез элемент НЕ - с входом сбросатретьего счетчика и с первым входом очетвертого элемента И, выход которогосоединен со счетным входом счетчика,а второй вход соединен с выходомгенератора импульсов и вторым входомтретьего элемента И, выход которогосоединен со счетным входом третьегосчетчика, выход первого триггера соединен с информационным входом реги, стра сдвига, вторые входы первого ивторого элементов .И соединены соответственно с информационными входамипервого и второго каналов преобразователя,)эобретение относится к вычислительной технике и может быть использовано при построении преобразователей, входящих в состав аппаратуры сопряжения цифровых устройств с полу дуплексными двухпроводными каналами ,связи.Целью изобретения является расширение класса решаемых задач за счетобеспечения возможностипреобраэования)о при различныхскоростях передачи данных и при различных формах передаваемых сигналов.На Фиг. 1 приведена блок-схема. предложенного преобразователя после- )5 довательного кода в параллельный; на фиг. 2 - временные диаграммы,. поясняющие работу преобразователя.Преобразователь последовательного кода в параллельный содерлФт первый 2 О1, второй 2, третий 3, четвертый 4 элементы И, первый 5 и второй 6 триггеры, генератор 7 импульсов, элемент 8 ИЛИ, элемент 9 НБ, регистр 10 сдвига, первый 11, второй 12 и третий 13 25 счетчики, информационные выходы 14 преобразователя, выход разрешения считывания 15, первый 16 и второй 17 информационные входы преобразователяПреобразователь работает следующим образом.На первый и второй входы 16 и 17 поступают сигналы из полудуплексного двухпроводного канала связи. На временной диаграмме (Фиг. 4) показаны временные соотношения между входными З 5 сигналами и биполярными сигналами канала связи. Для передачи каждого бита необходимо время, равное 4 Т. Информационные байты, разрядность кото 40 рых равна 11, следуют во времени друг за другом через 8 Т, где Т - длитель-ность положительного или отрицательного импульса. При поступлении первого бита 1 информационного байта сигнал с первого входа 16 проходит через элемент 1, устанавливает в состояние триггер 5, при этом сигнал с его инверсного выхода запрещает работу элемента 2 и,50 следовательно, установку триггера 6 в состояние "1", Сигнал с прямого выхода триггера 5 поступает на информационный вход регистра 10 и проходит через элемент 8 ИЛИ. Сигнал с выхода 55 элемента 8 ИЛИ поступает на управляющий вход регистра 10, на счетный вход счетчика 11, на вход установки "О" 2счетчика 12, на вход элемента 9 НЕ и на первый вход элемента 4, разрешая поступление импульсов генератора 7 на счетный вход счетчика 13, При работе счетчика )3 на его выходе появляется сигнал во время отсутствия биполярного сигнала, который производит сброс триггера 5, В это время на выходе элемента 8 ИЛИ устанавливается сиг нал "0",в результате чего работает элемент 9 НЕ который устанавливает в состояние "О" счетчик 13 и разрешает работу элемента 3. При этом импульсы генератора 7 поступают на счетный вход счетчика 12, однако на его выходе сигнал не может появиться так как счетчик 12 устанавливается в состояние "О" при поступлении очередного бита 1 или бита О.При поступлении бита "0" сигнал с второго входа )7 проходит через элемент 2, устанавливает в состояние11 триггер 6 , при этом сигнал с е го инверсного выхода запрещает работу элементаи , следовательно , ус тановку триггера 5 в состояние " 1 " . Си гнал с прямого выхода триггера б про= ходит только на вход элемента 8 ИЛИ , При этом в . регистре 1 0 происходит сдвиг инфо рмации , а эн ач ение кода на выходе счетчика 1 1 увеличивается на единицу .При поступлении следующих битов работа преобразователя повторяется .При по с туплении последнего бита информационного байта н а выходе счетчика1 1 , появляется управляющий сигнал , необходимый для считыв ания инФормации , записанной в регистр 1 О . В интервале времени между двумя байтами на счетный вход счетчика 1 2 по ступает большое число импульсов , в реэ уль тате чего на его выходе появляется сигнал для установки счетчика 1 1 в состояние "О" , после чего преобразователь возвращается в исходно е положение . Введение в известный преобразователь последовательного кода в параллельный новых элементов, их связей между собой и с элементами.известного преобразователя приводит к раеширению его функциональных возможностей за счет обеспечения возможности ,преобразования при различных скоростях передачи информации и при различных формах сигналов в канале связи,3 115964 4Предложенный преобразователь позво- ного преобразователя не нару 1 аетляет в случае изменения скорости пе- ся.редачи информации производить наст- В известном преобразователе в ройку только, одного генератора им- случае искажения входных сигналов воз-. пульса, в то время как в известномможны несовпадения сигналов, поступапреобраэователе в этом случае. необ-. ющих на вход элемента И, что может ходимо изменить параметры как,гене-, привести к потере битов 1, а следоратораимпульсов, так,.и элемента за- вательно, к искажению информации, Кро; держки. ме того, предложенный преобразовательИспользование вместо элемента за О можно испольэовать при работе с кеЭмдержки и элемента И двух триггеров йалами связи, для которых биту 1 приводит к тому, что в случае силь- соответствует только один положительных искажений входных сигналов отно" ный импульс, а биту О соответствует сительно друг друга работа предложен-; только отрицательный импульс.1159164 юФ1 ггпу вский торре витель И д Л.Ииеш ОС ех Л. Пилипенко Ред Циткияа акая Э Тираж 872 Подпясн И Государстаенногс комитета делам изобретений и открыты , Москва, Ж, Рауаская яабд. 4/5 НатекГ в ил ВНЗЯП по 113035

СмотретьЗаявка

3676775, 21.12.1983

ПРЕДПРИЯТИЕ ПЯ А-3706

ГЛАДКОВ ВЛАДИМИР ДМИТРИЕВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: кода, параллельный, последовательного

Опубликовано: 30.05.1985

Код ссылки

<a href="https://patents.su/4-1159164-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Электронный граммометр

Следующий патент: Преобразователь параллельного кода в последовательный

Случайный патент: Жидкостнокольцевая машина