Преобразователь уровня сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

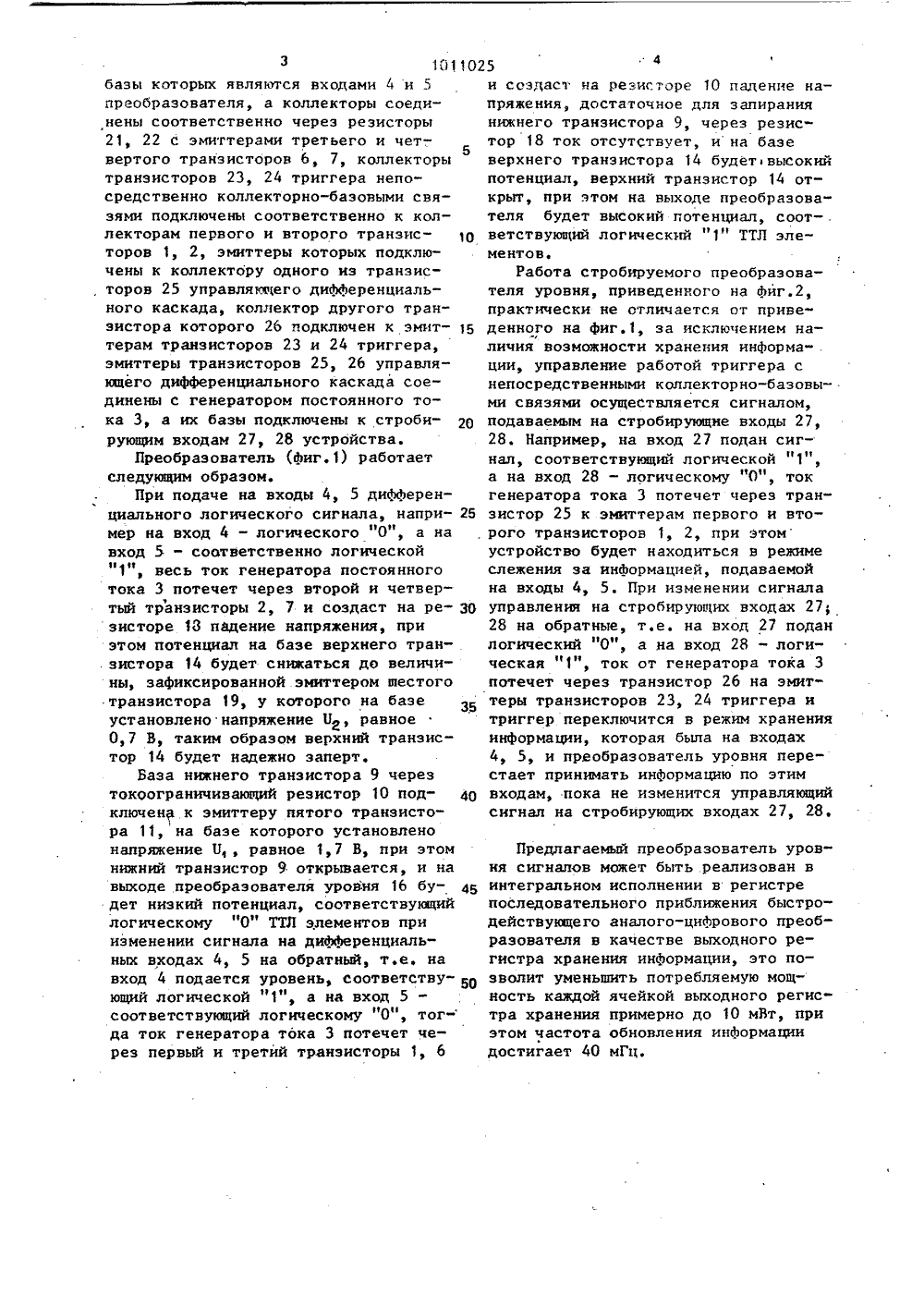

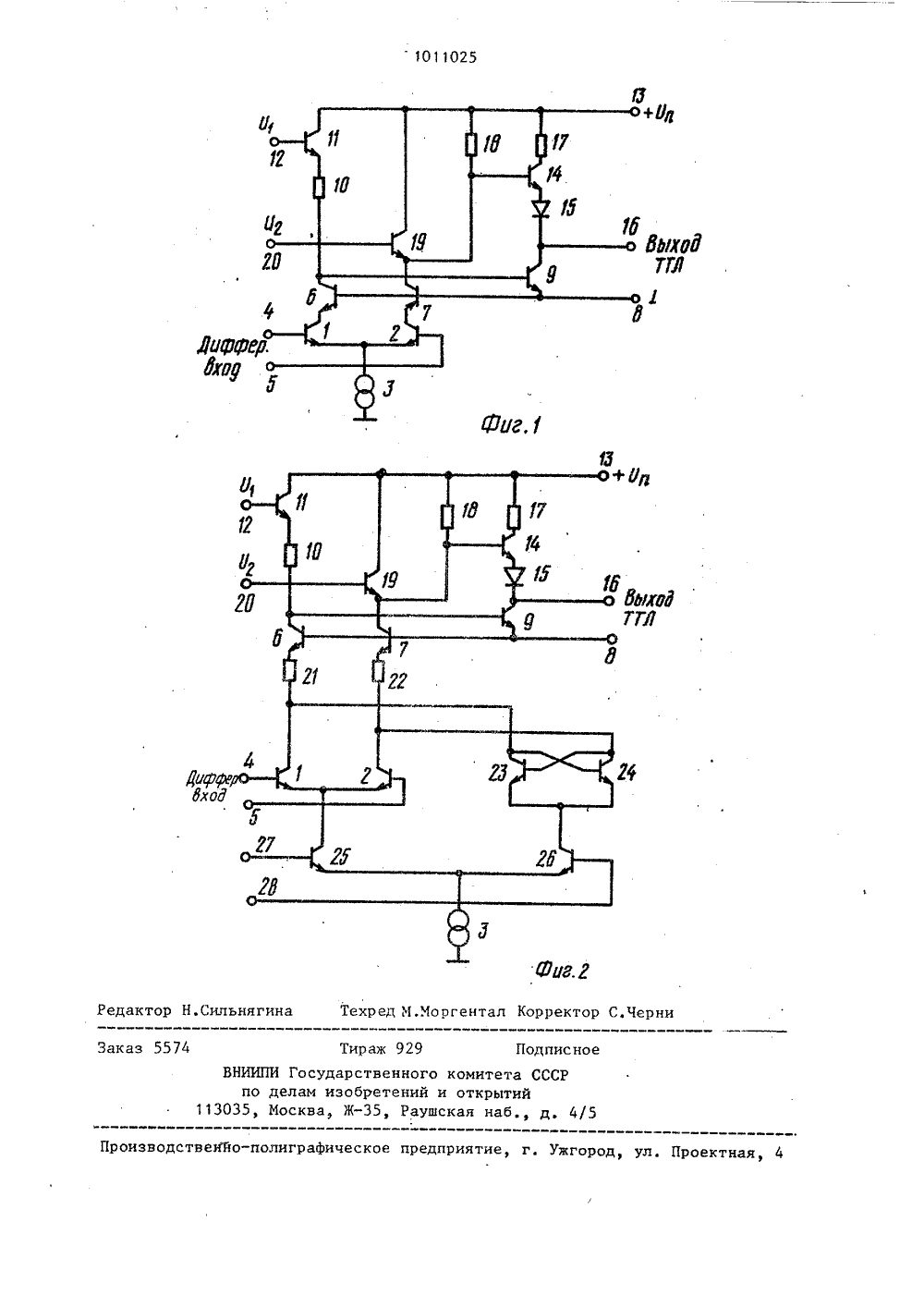

3 К 1900 САНИ ЗО ТЕН Н АВТОРСКОМ ЦЕТЕЛЬСТВУ 42Сотский8) ельство ССС 19/08, 1972 ьство СССР 19/00, 1977 ОСУДАРСТВЕННЫЙ КОМИТЕТ СССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ(54)(57) 1. ПРЕОБРАЗОВАТЕЛЬ УРОВНЯСИГНАЛОВ, содержащий входной дифференциальный переключатель тоха напервом и втором транзисторах, эмиттеры которых подключены к генераторутока, базы - к входам устройства, ивыходной ТТЛ каскад, эмиттер нижнеготранзистора которого подключен к общей шине, а коллектор верхнего транзистора через резистор - к шине питания, о т л и ч а ю щ и й с я тем,что; с целью повышения быстродействияи уменьшения потребляемой мощности,коллекторы первого и второго транзисторов подключены соответственно кэмиттерам третьего и четвертого транзисторов, базы которых подключены кобщей шине, а коллекторы - соответственно к базам верхнего и нижнего транзисторов выходного ТТЛ каскада,коллектор нижнего транзистора которого подключен к выходу и через диод -к эмиттеру верхнего транзистора, база которого через резистор подключенак шине питания, коллекторы пятого ишестого транзисторов подключены к шине питания, базы - к источникам опорных напряжений, а эмиттеры соответственно через резистор и непосредственно подключены к коллекторам второго и третьего транзисторов.2, Преобразователь по п. 1, о т -л и ч а юфщ и й с я тем, что, с целью его расширения функциональныхвоэможностей, введен управляющий дифференциальный каскад, базы транзисторов которого подключены к стробирующим входам устройства, эмиттеры - кгенератору тока, а коллекторы - соответственно к эмиттерам транзистороввходного дифференциального переключателя тока и эмиттерам транзисторовтриггера с непосредственными коллекторно-базовыми связями, коллекторытранзисторов которого подключены соответственно к коллекторам транзисторов входного дифференциального переключателя тока, 1011025Изобретение относится к импульснойтехнике и может быть использовано вкомпараторах напряжения, в выходныхрегистрах хранения, в частности в интегральных аналого-цифровых преобразователях,Известно устройство, содержащеевходной дифференциальньп каскад, выходы которого подклюдень к входамдвух выходных ТТЛ каскадов,Недостатком устройства являетсянизкое быстродействие и большая потребляемая мощность.Известен также ТЛЭС-ТТЛ преобразователь, содержащий входной дифференциальный переключатель тока надвух транзисторах, эмиттеры которыхподключены к источнику тока, базы -к входам устройства, и выходные ТТЛ 20каскады, эмиттеры нижних транзисторовкоторых подключены к общей шине, аколлекторы верхних транзисторов черезрезистор - к шине питания,Недостатком такого преобразователя 25является низкое быстродействие ибольшая потребляемая мощность.Цель изобретения - повышение быстродействия и уменьшение потребляемоймощности преобразователя. 30Для достижения поставленной целив преобразователе содержащем входнойдифференциальный переключатель токана первом и втором транзисторах,эмиттеры кОтОРых подключены к генера 35тору тока, базы - к входам устройства и выходной ТТЛ каскад эмиттернижнего транзистора которого подключен к общей шипе, а коллектор верхнего транзистора - к шине питания, кол"40лекторы первого и второго транзисторов подключены соответственно к эмиттерам третьего и четвертого транзисторов, базы которых подключены к общей шине, а коллекторы - соответственно к базам верхнего и нижнеготранзисторов выходного ТТЛ каскада,коллектор нижнего транзистора которого подключен к выходу и через диодк эмиттеру верхнего транзистора, база которого через резистор подключенак шине питания, базы - к источникамопорных напряжений, а эмиттеры соответственно через резистор, и непосредственно подключены к коллекторам второго и третьего транзисторов, а кро-ме того,. введен управляющий дифференциальный каскад, базы транзисторовкоторого подключены к стробирующим входам устройства, эмиттеры - к генератору тока, а коллекторы - соответственно к эмиттерам транзисторов входного дифференциального переключателя тока и к эмиттерам транзисторов триггера с непосредственными коллекторно-базовыми связями, коллекторы транзисторов. которого подключены соответственно к коллекторам транзисторов входного дифференциального переключателя тока.На. Фиг.1 приведена принципиальная схема преобразователя дифференциальных сигналов в ТТЛ уровни; на фиг,2 - принципиальная схема стробируемого преобразователя дифференциальных сигналов в ТТЛ уровни.Преобразователь уровня (фиг.1) содержит входной дифференциальный переключатель тока на первом и втором транзисторах 1, 2, эмиттеры которых подсоединены к генератору постоянного тока 3, их базы являются входами 4 и 5 преобразователя, базы третьего и четвертого транзисторов 6,соединены с общей шиной 8, их эмиттеры соединены соответственно с коллекторами первого и второго транзисторов 1, 2 коллектор третьего транзистора 6 соединен с базой нижнего транзистора 9 выходного ТТЛ каскада и через резистор 10 с эмиттером пятого транзистора 11, на базу которого подается опорное напряжения от источника опорного напряжения 12, ограничивающее степень насыщения нижнего транзистора 9, коллектор пятого транзистора 11 подключен к шине питания 13, коллектор третьего транзистора 7 подключен к базе верхнего транзистора 14, эмиттер которого через прямосмещенный диод 15 подключен к коллектору нижнего транзистора 9, являющегося выходом 16 преобразователя уровня, коллектор верхнего транзистора 14 через резистор 17 подключен к шине питания 13, кроме того, коллектор транзистора 17 соединен через резистор 18 с шиной питания 13 и с эмиттером шестого транзистора 19, на базу которого подается опорное напряжение от источника опорного напряжения 20, а его коллектор соединен с шиной питания 13.В схему преобразователя уровня (фиг.1) введен стробирующий триггер- защелка (Фиг.2), содержащий входной дифференциальный переключатель тока на первом и втором транзисторах 1; 2,з 10110базы которых являются входами 4 и 5преобразователя, а коллекторы соединены соответственно через резисторы21 22 с эмиттерами третьего и четФ5вертого транзисторов 6, 7, коллекторытранзисторов 23, 24 триггера непосредственно коллекторно-базовыми связями подключены соответственно к коллекторам первого и второго транзис Оторов 1, 2, эмиттеры которых подключены к коллектбру одного иэ транзис, торов 25 управляющего дифференциального каскада, коллектор другого транзистора которого 26 подключен к эмиттерам транзисторов 23 и 24 триггера,эмиттеры транзисторов 25, 26 управляющего дифференциального каскада соединены с генератором постоянного тока 3, а их базы подключены к стробирующим входам 27, 28 устройства,Преобразователь (Фиг,1) работаетследующим образом.При подаче на входы 4, 5 дифференциального логического сигнала, напри бмер на вход 4 - логического "О", а навход 5 - соответственно логической"1", весь ток генератора постоянноготока 3 потечет через второй и четвертый транзисторы 2, 7 и создаст на ре- ЗОзисторе 13 падение напряжения, приэтом потенциал на базе верхнего тран. зистора 14 будет снижаться до величины, зафиксированной эмиттером шестоготранзистора 19, у которого на базеустановлено напряжение П, равное0,7 В, таким образом верхний транзистор 14 будет надежно заперт.База нижнего транзистора 9 черезтокоограничивающий резистор 10 подключена к эмиттеру пятого транзистора 11, на базе которого установленонапряжение П равное 1,7 В, при этомнижний транзистор 9 открывается, и навыходе преобразователя уровня 16 будет низкий потенциал, соответствующийлогическому "О" ТТЛ элементов приизменении сигнала на дифференциальных входах 4, 5 на обратный, т.е. навход 4 подается уровень, соответству- БОющий логической "1", а на вход 5 -соответствующий логическому "0", тог-да ток генератора тока 3 потечет через первый и третий транзисторы 1, 6 и создаст на резисторе 10 падение напряжения, достаточное для залирания нижнего транзистора 9, через резистор 18 ток отсутствует, й на базе верхнего транзистора 14 будетвысокий потенциал, верхний транзистор 14 открыт, при этом на выходе преобразователя будет высокий потенциал, соот- . ветствующий логический "1" ТТЛ элементов.Работа стробируемого преобразователя уровня, приведенного на Фиг.2, практически не отличается от приведенного на фиг.1, за исключением наличия возможности хранения информа- . ции, управление работой триггера с непосредственными коллекторно-базовыми связями осуществляется сигналом,подаваемым на стробирующне входы 27,28. Например, на вход 27 подан сигнал, соответствующий логической "1", а на вход 28 - логическому "О", токгенератора тока 3 потечет через транзистор 25 к эмиттерам первого и второго транзисторов 1, 2, при этомустройство будет находиться в режимеслежения за информацией, подаваемойна входы 4, 5. При изменении сигналауправления на стробирующих входах 27;28 на обратные, т.е. на вход 27 поданлогический "О", а на вход 28 - логическая "1", ток от генератора тока 3 потечет через транзистор 26 на эмиттеры транзисторов 23, 24 триггера и триггер переключится в режим хранения информации, которая была на входах 4, 5, и преобразователь уровня перестает принимать информацию по этим входам, пока не изменится управляющий сигнал на стробирующих входах 27, 28. Предлагаемый преобразователь уровня сигналов может быть реализован в интегральном исполнении в регистре последовательного приближения быстродействующего аналого-цифрового преобразователя в качестве выходного регистра хранения информации, это позволит уменьшить потребляемую мощность каждой ячейкой выходного регистра хранения примерно до 10 мВт, при этом частота обновления информации достигает 40 мГц./5 Проектная, 4 жгор Тираж ВНИИПИ Государст по делам изобр 113035, Москва, Жвенного комитета ССетений и открытий 5, Раушская наб., д оизводствекно-полиграфическое предприятие йа ТЯ

СмотретьЗаявка

3232603, 09.01.1981

ПРЕДПРИЯТИЕ ПЯ М-5255

РЯБОВ Е. А, СОТСКИЙ Д. В

МПК / Метки

МПК: H03K 19/00

Опубликовано: 15.11.1988

Код ссылки

<a href="https://patents.su/4-1011025-preobrazovatel-urovnya-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь уровня сигналов</a>

Предыдущий патент: Устройство для автоматического сопровождения объекта

Следующий патент: Способ гидрохимической съемки на дне водоемов

Случайный патент: Устройство для разгрузки железнодорожных цистерн с застывшими нефтепродуктами