Устройство для обнаружения ошибок в отладочных программах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

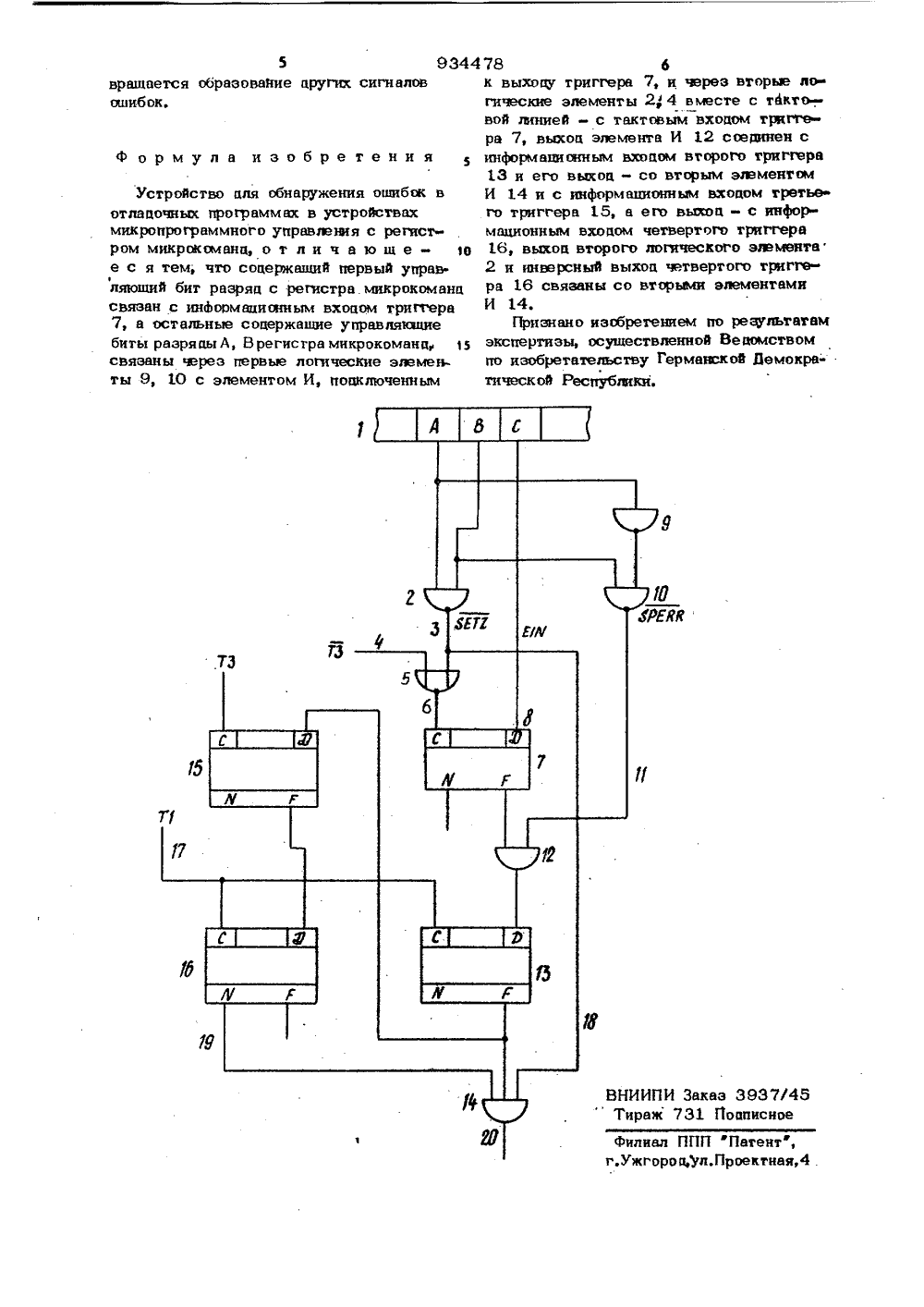

О П И С А Н И Е934478ИЗОБРЕТЕН ИяК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ С фаз СфавтсинвСфцналнстюесиивресттублни(33) %РСО 6 Р 198791(33) ГДРгОпубликовано 07.06,82 Бтоллетень2 1 3 Ьвударстааай кенвтет ИСР ва делан изобретений и еткрнтнй) Заявитель 4) УСТРОЙ ВО ДЛЯ ОБ ДОЧНЫХ П К ЖЕНИЯ АММАХ ванитв перех сравненикать отятельнымени, Ивыполит.е. в 3Изобретение применимо для вычисли, тельных машин с микропрограммным утт равленнем, для которых имеется тест с микропрограммным управлением, благодаря которому можно с помсщью последовательности микрокоманд проверять . коммутационные характеристики средств аппаратурного обеспечения.При пуске в эксплуатацию вычислительных машин и в случае появления ошибок требуется проверить правильное выполнение посждовательностей команд как на макроуровне, так и на микроуров не.Извекаждойвается стен метод, по которому после микроком анды машина останавлии адрес микрокоманды сравнивает данным адресом. После каждого я машину нужно заново запусруки. Этот метод слишком обстой и требует больших затрат врез-за шаговой работы процессы ния могут быть неправильными, яде. случаев ошибки не будут возникать нли они будут ложно интерпретироваться,Известна схема протоколирования вы- полнении программы в цифровых электронных вычислительных машинах (ВИ 3-0в 22 46 863), направленная на устранениеуказанных недостатков, по которой может быть выбран вручную или автомашин один из трех режимов протоколироя. Здесь протокоатрутотся нли адресода, или адрес обхода н перехода,или каждый адрес команды, Протоколирование адресов делает возможным точныйконтроль выполнения программы, однаконе дает автоматического сообщения об5Фф . ошибке при неправильном выполнении программы. Кроме того, требуется памятьпроток ола.Известна также схема для обнаружения и анализа ошибас в электронных вычислительньк машинах, по которой переключательные схемы, упорядоченные в лоъгческой последовательностн по отношениюк потоку информации, проверяются в данФ3 9344 ной послецовательности (ВМЮ 22 47 787). Каждой переключательной схеме сопоставляется адрес, с помошью которого вызывается стандартная программа проверки для данной схемы. При этом проверка относится к таким переключательным схемам как регистры, арифметические блоки, логические элементы и т.д. но не относится к устройству микропрограммного управления.1 ОЦель изобретения - улучшение контроль ного испытания устройства микропрограммного управления вычислительной машины, вследствие чего сокращается фаза ручного управления нри пуске в эксплуатацию и время поиска ошибок.В сснове изобретения лежит задача создать такое устройство, которое автоматически контролировадо бы правильное выполнение микрцпрограммв т.е. правильи ную адресацию микрокоманд, регистрировало и быстро сообшало бы отклонение от заданного выполнения.С огласно изобретению задача решается таким образом, что содержащий первый управляющий бит разряд регистра микро- команд связан с информационным входом триггера, а остальные содержащие управляющие биты разряды регистра микроко мана связаны через первые логические ЗО элементы с элементом И, подключенным к выхоцу триггера, а через вторые ложческие элементы вместе с тактовой линией - с тактовым входом триггера, выход элемента И соединен с информацион- з 5 ным входом второго триггера, а его вьг ход - со вторым элементам И и с информационным входом третьего триггера, а его выход - с информащонным входом чет вертого триггера, выход второго логичес-юО кого элемента и инверсный выхоц четвертого триггера связаны совторыми элементом И.Изображенный на чертеже регистр мик- рокоманц 1 содержит три разряда А, В и С. Разряды А и В связаны с первым элементом НЕ-И 2, который выдает сигнал БАЕТ 2- по линии 3. Линия 3 и тактовая линия 4, на которую поступает такт ТЗ четырехтактной.системы, являются входа 50 ми элемента НЕ-ИЛИ, выход 6 которого связан с тактовым входом триггера 7. Информационный вход триггера 7 соединен с разрядом С регистра микрокоманц 1 и получает сигнал Е 3 й через линию 8.Разряд А соединен через инвертор 9 со вто-рым элементом НЕ-И 10, а разряц В - с его вторым входом, Выход этого элемента подключен к линии 11, на которую по 78 4ступает сигнал 6 РЕЯР . Выход триггера 7 вмес.те с линией 11 выводятся на элемент И 12 в выход которого является информационным входом второго триггера 13, выход которого соединен со вторым элементом И 14 и с информационным входом третьего триггера 15, выхоц которого выводится на информационный вход четвертого триггера 16, На тактовые входы триггеров 13 и 16 через линию 17 поцается такт Т 1, а на тактовый вход триггера 15 - такт Т 3, Остальные входы элемента И 14 связаны через линии 18 и 19 с линией 3 или с инверсным выходом тригжра 16. Выход 20 элемента И 14 выводит си 1 нал ошибки. Сигналы ЯЕТ 2, и 8 РЕЖ могут формироваться непосрецственно или же иэ других комбинаций сигналов. Запись микрокоманд в регистр микрокоманц осуществляется непосрецственно перец тактом Т 1, так что информация нахоцится в распоряжении в течение длительности такта от Т 1 цо Т 4. До тех пор, пока емкость разрядов А, В и С равна О, процесс обнаружения ошибок не действует. С помощью комбинации 111 тактом ТЗ включается первый триггер 7. Таким образом, на епементе И 12 появпяется сигивп 11 е нв пинии 11 - сионов 5 РЕйй=1, Не вм хоце элемента И 12 появляется сигнал 1, который ие становится эффективным в этом такте, так как он записывается в триггер 13 лишь с тактом Т 1 следующего акта. Следующие микрокоманцы имеют комбинацию О 1 Х. В этих условиях Я Е Т 2. =1 и 5 РЕ Й К =О, Выход триггера 13 равен 0 и, тем самым. также и вьг ход элемента И 14 равен О, Если в одной из следующих микрокоманц появится иэмененнвя яомбинвиия, иепощмер О О Х или 1 0 Х, то сигнал 6 РЕЙР и вьаоц элемента И 12 становятся равными 1. С тактом Т 1 эта единица принимается три 1 гером 13 и подается на элемент .И 14, на котором через линию 18 приложен сигнал б 1 ЕТ 2. =1, а через линию 19 от инверсного выхода триггера 16 - также сигнал 1. Тем самым выход 20 элемента И 14 вььцает сигнал ошибки. С тактом ТЗ выход триггера 13 принимается триггером 15, выход которого с тактом Т 1 - триггером 16, вследствие чего его инверсный выход переходит на 0 и отключается сигнал ошибки. В конце тестовой микропрограммы устанавливается комбинация 1 1 О. Вследствие этого в такте ТЗ триггер 7 сбрасывается с О и, тем самым, предот5 9344вращается образование других сигналовошибок.Ф ормула изобретенияУстройство аля обнаружения ошибок в отладочньк программах в устройствах микропрограммного управления с регист ром микрокомана, о т л и ч а ю щ е - 10 е с я тем, что содержащий первый упрввляющий бит разряд с реестра. микрокоманц связан с информационным входом триггера 7, а остальные соаержащие упрввляквцие биты разряды А, В регистра мнкрокоманд 1 з связаны через первые логические элементы 9, 10 с элементом И, подключенным 78 6к выхоцу триггера 7, и через вторые ло гические элементы 2,4 вместе с такто вой юынией - с тактовым входом триггера 7, выхоц элемента И 12 ссединен с информавинным вхоаом второго триггера 13 и его выход - со вторым элементом И 14 и с информационным вхоаом третье го триггера 15, в его выхоа - с информационным входом четвертого триггера 16, выход второго логического элемента 2 и инверсный выход четвертого триггера 16 связаны со вторьачи элементами И 14,Признано изобретением по результатам экспертизы, осуществленной Ве домством по изобретательству Гермаккой Демократической Респубжки.

СмотретьЗаявка

7770154, 04.04.1978

ФЕБ РОБОТРОН, КАРЛ-МАРКС-ШТАДТ

ДИТМАР РЕЙНЕРТ, ХАУБОЛЬД ОЛЬАФ

МПК / Метки

МПК: G06F 11/22

Метки: обнаружения, отладочных, ошибок, программах

Опубликовано: 07.06.1982

Код ссылки

<a href="https://patents.su/3-934478-ustrojjstvo-dlya-obnaruzheniya-oshibok-v-otladochnykh-programmakh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок в отладочных программах</a>

Предыдущий патент: Устройство для формирования контрольного кода по четности

Следующий патент: Имитатор дискретного канала связи с ошибками синхронизации

Случайный патент: Струйный индикатор уровня жидкости