Усредняющее устройство с блокировкой для фазирования дискретной информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 896785

Авторы: Болотин, Сальникова

Текст

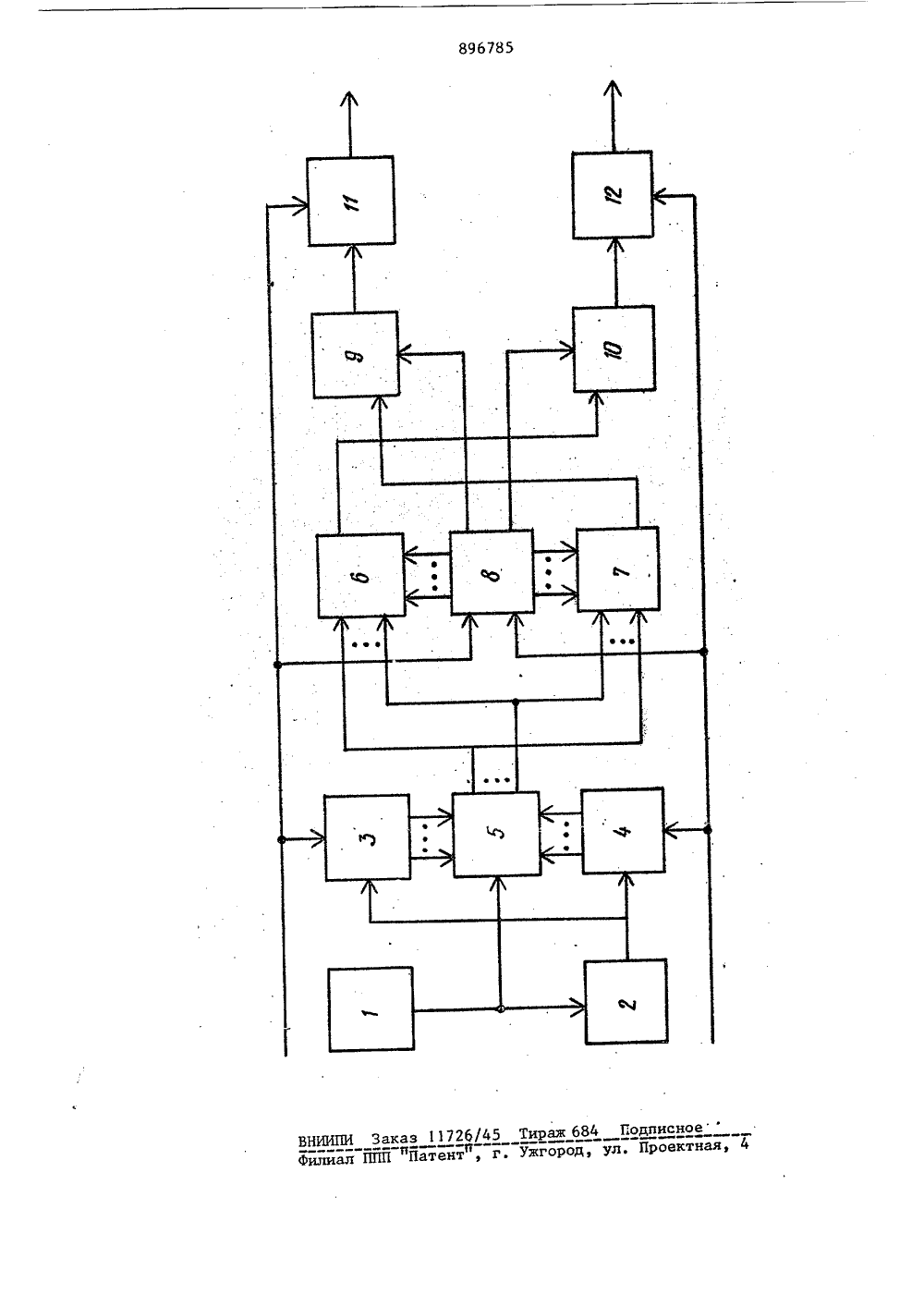

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоаетсиниСоцнапнстнчесинхРеспублик иц 896785(51)М, Кл. Н 04 1 17/00 14/18 исоелинением заявки оеударстееииый конит СССР(23) П р нори тет Опубликовано 07.01.82. Б оо двлаи изобретеиий и открытийта опубликования описания 07.01.83.(71) Заявит УСРЕДНЯЮЩЕЕ УСТРОЙСТВО С БЛОКИРОВКОЙДЛЯ ФАЗИРОВАНИЯ ДИСКРЕТНОЙ ИНФОРМАЦИИ с нулевым входом триггера вычи С 3 ания ОддостаЦелности овышение точь изобретен усреднения. Указанная цель достигается тем, что в известное усредняющее устройство с блокировкой для Фазирования дискретной информации введены датчик времени, элемент задержки, два счетчика, два коммутатора и дешифратор, причем выход датчика времени соединен с одним входом дешифратора и через элемент задержки с первыми входами счетчиком, вторые входы которых соединены с первым и вторым входами устройства, выходы счетчиков соединены с соответству - . ющими входами дешифратора, выходыкоторого соединены с входами коммутаторов, соответствующие разряды .добавления и вычитания реверсивного Изобретение относится к технике передачи дискретной информации и мо жет использоваться в системах синх- ронизации приемников дискретной инФормации.Ло основному авт. св. У 527833 известно усредняющее устройство с блокировкой для Фазирования дискретной информации, содержащее многоразрядный реверсивный счетчик, один выход которого через триггер добавления подключен ко входу первого элемента И, а второй выход реверсивного счетчика через триггер вычитания подключен ко входу второго элемента И, причем к дополнительным входам элементов И подключены соот. ветствующие входы реверсивного счет. чика, промежуточный разряд вычитания реверсивного счетчика соединен с нулевым входом триггера добав. ления, а промежуточный разряд добав. ления реверсивного счетчика соедико в известном устроистве нечная точность, 896785счетчика через коммутаторы соединены с вторыми входами триггеров.На чертеже изображена структурная электрическая схема предлагаемого устройства,Устройство содержит датчик 1 времени, элемент 2 задержки, счетчики3 и 4, дешифратор 5, коммутаторы6 и 7, многоразрядный реверсивныйсчетчик, триггеры 9 и 10 добавленияи вычитания элементы И 11 и 12.Устройство работает следующим образом.Импульсы добавления и вычитания,поступающие на входные шины устройства, заряжают соответственно счетчики 3 и 4 до некоторого значения.В момент формирования датчиком 1 выходного импульса дешифратора 5 на одной.из выходных шин формирует уровень напряжения, управляющий работой коммутаторов 6 и 7. Кроме того, сигнал датчика 1, задержанныйэлементом задержки 2, на время,приблизительно равное длительностисигнала, осуществляет перевод счетчиков 3 и 4 в исходное ( нулевое )состояние. При этом входные импульсы добавления и вычитания поступают соответственно на суммирующий и вычитающий входы многоразрядного реверсивного счетчика 8,осуществляя его заряд.В случае, если, например, число импульсов добавления превыситчисло импульсов вычитания, поступивших на его второй вход, на величину, равную коэффициенту пересчета многоразрядного реверсивного счетчика 8, на выходе его последнегоразряда добавления появится импульс,переводящий триггер 9 в единичноесостояние. Уровень напряжения навыходе триггера 9 разрешает прохождение импульсов добавления черезэлемент И 11 на одну выходную шинуустройства. Теперь импульсы добавления, поступающие на одну входную шину устройства, проходят на его выходбез усреднения.Сброс триггера 9 в нулевое состояние, те. запрещение прохожденияимпульсов добавления на выход устройства, осуществляется сигналом свыхода одного из разрядов вычитаниямногоразрядного реверсивного счетчика 8 через коммутатор 7, Коммутация выхода соответствующего разряда вычитания многоразрядного реверсивного счетчика 8 со сбросовым входомтриггера 9 устанавливается коммутатором 7 в зависимости от того, накаком из выходов дешифратора 5 появится уровень напряжения.Совершенно аналогичным образомпроисходит формирование импульсоввычитания на другой выходной ши не (работа триггера 10 аналогичнаработе триггера 9, а элемента И 12работе элемента И 11).Таким образом, в зависимости отвеличины разницы числа импульсов 1 добавления и вычитания (т.е. показаний счетчиков 3 и 4), поступившихна входы устройства за время междудвумя импульсами на выходе датчика1, сброс триггеров 9 и 10 осуществляется сигналом, появившемся навполне определенном выходе реверсивного счетчика 8,Предлагаемое устройство обладает в сравнении с известным более 25 высокой точностью усреднения и скоростью установления синхроннзма прииспользовании в системах передачидискретной информации.30формула изобретенияУсредняющее устройство с блокировкой для фазирования дискретнойинформации по авт. св. М 527833,о т л и ч а ю щ е е с я тем, что,с целью повышения точности усреднения, введены датчик времени, элемент задержки, два счетчика, двакоммутатора и дешифратор, причем40 выход датчика времени соединен с одним входом дешифратора и через элемент задержки е первыми входамисчетчиков, вторые входы которых соединены с первым и вторым входами уст 4 ройства, выходы счетчиков соединеныс соответствующими входами дешифра"тора, выходы которого соединены свходами коммутаторов, соответствующие разряды добавления и вычитания50 реверсивного счетчика через коммутаторы соединены с вторыми входамитриггеров.Источники информации,принятые во внимание при экспертизе55 1. Авторское свидетельство СССРВ 527833, кл. Н 04 1. 17/00, 1974Заказ 1172 б/45 Тираж 684 Годписл ППП Патент , г. Ужгород, ул. Проектная

СмотретьЗаявка

2908314, 08.04.1980

ПРЕДПРИЯТИЕ ПЯ А-3327

БОЛОТИН ГРИГОРИЙ КУЗЬМИЧ, САЛЬНИКОВА ЛАРИСА ИВАНОВНА

МПК / Метки

МПК: H04L 17/00

Метки: блокировкой, дискретной, информации, усредняющее, фазирования

Опубликовано: 07.01.1982

Код ссылки

<a href="https://patents.su/3-896785-usrednyayushhee-ustrojjstvo-s-blokirovkojj-dlya-fazirovaniya-diskretnojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Усредняющее устройство с блокировкой для фазирования дискретной информации</a>

Предыдущий патент: Устройство для передачи дискретной информации

Следующий патент: Устройство для регистрации дискретной информации

Случайный патент: Устройство для пробивки отверстий в потолке