Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 884110

Авторы: Беляев, Бондарос, Проскуряков, Язбурскис

Текст

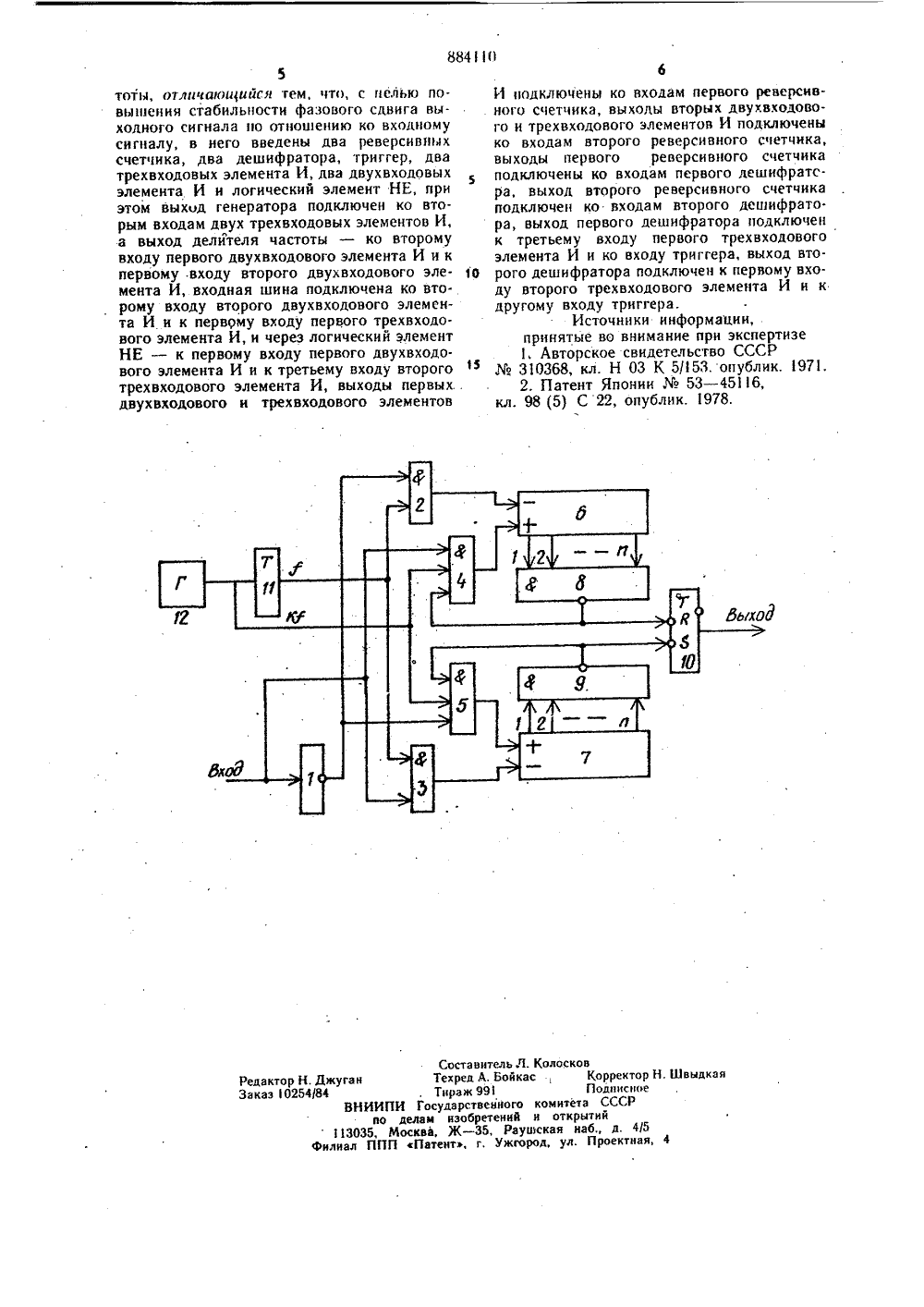

ОП ИСАНИЕ ИЗЬВРЕТЕН ИЯ Союз СоветскихСоциалистическихРеспублик 1884110 АВТОРСКОМ ЕТЕЛЬСТВУ(5) М, Кл.з 895986 18-21 03 К 5/153 Гфеударстееемл кемлтвт СССР во деллм лзлбретлллй и еткрмтий(54) ФОРМ ИРОВАТЕ ПУЛЬСОВ ФИзобретение относится к импульсной тех- порядок выше частоты входного сигнала, нике и может использоваться, например, в а частота Г 2 на порядок выше частоты качестве формирователя опорного напряже- П, две переменные схемы ПС и ПС 2 для ния для демодуляции и модуляции сигналов измерения длительности входного сигнала в двухканальных Системах с амплитудно-фа- в двойном коде с использованием сигналов зовой модуляцией и одноканальным управле- Г 1 н Г 2, схему умножения, на вход которой кием. подается сигнал с ПС 1 и сигнал управленияИзвестен формирователь импульсов, со- кратностью умножения, задаваемой с пуль- держащий генератор пилообразных импуль- та управления через схему формирования сов, источник постоянного напряжения, два, сигнала кратности, схему запоминания, на пороговых устройства, два генератора пря- вход которой поступает сигнал с выхода моугольных импульсов, выходы источников умножителя и управляющий сигнал от тригпостоянного напряжения и пилообразных им Е гера, схему сравнения, на выходе которой пульсов подключены ко входу двух порого- формируется импульс задержки, при условых устройств, выходы которых подключены вии совпадения сигналов на входах от ПС 2 ко входу двух генераторов прямоугольных и схемы запоминания, Относительная длиимпульсов 1 Ц.,:тельность задержки определяется отношеЙедостатком такого формирователя им- нием частотгенераторов Г 1 и Г 2, умноженпульсов является низкая точность относи- ным на коэффициент кратности 2.Ительного фазового сдвига входного и выходНедостаток известного устройства сос. ного сигналов при дрейфе частоты входногоНаиболее близким по своей сущности тех- тонт в зависимости фазового сдвига выходническим решением к предлагаемому изоб-, ных импульсов относительно входных прн ретению является формирователь импульсов,. 20 изменении частоты входного сигнала.который включает в себя два генератора им- Цель изобретения - повышение стабильпульсов Г и Г 2, частоты которых выбраны .; ности фазового сдвига выходногосигнала так, что частота Г 1, по крайней мере, на по отноаенню ко входному сигналу.3Поставленная цель достигается тем, что в формирователь импульсов, содержащий генератор, подключенный к делителю частоты, введены два реверсивных счетчика, два дешифратора, триггер, два трехвходовых элемента И, два двухвходовых элемента И 5 и логический элемент НЕ, при этом выход генератора подключен ко вторым входам двух трехвходовых элементов И, а выход делителя частоты - ко второму входу первого двухвходового элемента И и к первому входу второго двухвходового элемента И,в входная шина подключена ко второму входу второго двухвходового элемента И и к первому входу первого трехвходового элемента И и через логический элемент НЕ - к первому входу первого двухвходового элемента И и к третьему входу второго трехвходового элемента И,. выходы первых двухвходового и трехвходового элементов И подключены ко входам первого реверсивного счетчика, выходы вторых двухвходового и трехвходового элементов И подключены ко 20 входам второго реверсивного счетчика, выходы первого реверсивного счетчика подключены ко входам первого дешифратора, выход второго реверсивного счетчика подключен к входам второго дешифратора, выход первого дешифратора подключен к третьему входу первого трехвходового элемента И и ко вхо- . ду триггера, выход второго дешифратора под ключен к первому входу второго трехвходового элемента И и - к другому входу триггера. . 30На чертеже представлена структурнаясхема формирователя импульсов.Устройство состоит из логического элемента НЕ 1, двух двухвходовых элементовИ 2 и 3, двух трехвходовых элементов И4 и 5, двух реверсивных счетчиков 6 и 7,двух дешифраторов 8 и 9 на элементах И -НЕ, триггера 10, делителя частоты 11, генератора 12,Выход генератора 12 подключен ко вторым входам двух трехвходовых элементов 40И и через делитель частоты 11 - ко второму входу первого двухвходового элемента И 2 и к первому входу второго двухвхо-,дового элемента И 3, Вход устройства 1подключен ко второму входу второго двухвходового элемента И 3, к первому входу4первого трехвходового элемента И 4 и черезлогический элемент НЕ 1 - к первому входу первого двухвходового элемента И 2 и ктретьему входу второго трехвходового элемента И 5, Выходы первых двухвходовогои трехвходового элементов И 2 и 4 подключены ко входам первого реверсивногосчетчика 6, выходы вторых двухвходового итрехвходового элементов И 3 и 5 - ковходам второго реверсивного счетчика 7Выходы первого реверсивного счетчика 6 55подключены ко входам первого дешифрато.ра 8, выходы второго реверсивного счетчика 7 - ко входам второго дешифратора 9. 4Выход первого дешифратора 8 подключен к третьему входу первого трехвходового элемента И 4 и ко входу триггера 10, выход второго дешифратора 9 подключен к первому входу второго трехвходового элемента И 5 и к другому входу триггера 10, выход которого является выходом устройства.Подлежащий сдвигу сигнал поступает непосредственно на сигнальные входы элементов 3 и 4 и через первый 4 трехвходовый и второй 3 двухвходовый элементы И, и через элемент НЕ- на сигнальные входы первого 2 двухвходового и второго 5 трехвходового элементов Й.Пусть сначала выходной триггер находится в нулевом состоянии, а в счетчиках 6 и 7 записаны максимальные числа (т. е. во всех разрядах счетчика занесены единицы).Следовательно, йа выходах дешифраторов 8 и 9 будут сигналы с уровнем логического нуля, и схемы 4 и 5 будут закрыты по третьим входам.Пусть на сигнальный вход поступает сигнал с уровнем логической единицы, элемент И 3 открывается и через него счетные импульсы поступают на вцчитающий вход счетчика 7,Как только содержимое счетчика уменьшается на единицу, на выходе дешифратора 9 появляется. открывающий элемент 5 сигнал. Однако эта схема остается закрытой по сигнальному входу, Содержимое счетчика 7 уменьшается в течение положительного полу- периода входного сигнала. В тот момент, когда на сигнальном входе окажется отрицательная полуволна, элемент И 3 закрывается, но открываются элементы И 2 и 5. Че. рез элемент И 2 счетные импульсы поступают на вычитающий вход счетчика 6 (в счетчике 6 начинается процесс, аналогичный процессу в счетчике 7, но с задержкой на полупериод входного сигнала), а через элемент И 5 импульсы поступают на суммирующий вход счетчика 7.В этот момент на выходе дешифратора 9 сигнал равняется логическому нулю, вследствие чего элемент И 5 закрывается, а выходной триггер опрокидывается в единичное состояние, Обратно в нулевое состояние триггер возвращается через полупериод частоты несущей с помощью дешифратора 8, когда закончится аналогичный процесс в счетчике 6.Таким образом, процессы вычитания и суммирования счетных импульсов в счетчиках 6 и 7 повторяются со сдвигом на часть полупериода входного сигнала, а на выходе триггера 10 будет сигнал, аналогичный вход. ному, но сдвинутый по фазе относительно входного сигнала,Формула изобретенияформирователь импульсов, содержащий генератор, подключенный к делителю час88410 Составит Техред А. Тираж 991 Государствен ам изобрет ква, Ж - 35,Патент, г.ель Л. КолосковВойкас . Корректор НПодписноеного комитета СССРений и открытийРаушская набд. 4/5Ужгород, ул, Проектная,ыдк Редактор Н. ДжуганЗаказ 10254/84ВНИИПИпо дел113035, Моефилиал ППП5тоти, отлпчающийгя тем, что, с целью повышения стабильности фазового сдвига выходного сигнала по отношению ко входному сигналу, в него введены два реверсивнцх счетчика, два дешифратора, триггер, два трехвходовых элемента И, два двухвходовых элемента И и логический элемент НЕ, при этом выход генератора подключен ко вторым входам двух трехвходовых элементов И, а выход делителя частоты - ко второму входу первого двухвходового элемента И и к первому .входу второго двухвходового эле О мента И, входная шина подключена ко второму входу второго двухвходового элемента И и к первому входу первого трехвходового элемента И, и через логический элемент НЕ - к первому входу первого двухвходового элемента И и к третьему входу второго трехвходового элемента И, выходы первых . двухвходового и трехвходового элементов И подключены ко входам первого реверсивного счетчика, выходы вторых двухвходового и трехвходового элементов И подключеныко входам второго реверсивного счетчика,выходы первого реверсивного счетчикаподключены ко входам первого дешнфратсра, выход второго реверсивного счетчикаподключен ко входам второго дешифрато.ра, выход первого дешифратора подключенк третьему входу первого трехвходовогоэлемента И и ко входу триггера, выход второго дешифратора подключен к первому входу второго трехвходового элемента И и кдругому входу триггера.Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССР310368, кл. Н 03 К 5/ 53. опублик. 1971.2, Патент Японии53 - 45116,кл. 98 (5) С 22, опублик. 1978.

СмотретьЗаявка

2895986, 24.03.1980

ВОЕННОВОЗДУШНАЯ ИНЖЕНЕРНАЯ ОРДЕНОВ ЛЕНИНА И ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ КРАСНОЗНАМЕННАЯ АКАДЕМИЯ ИМ. ПРОФ. Н. Е. ЖУКОВСКОГО

БЕЛЯЕВ ВАСИЛИЙ МАКАРОВИЧ, БОНДАРОС ЮЛИЯ ГРИГОРЬЕВНА, ПРОСКУРЯКОВ ВАЛЕНТИН ИВАНОВИЧ, ЯЗБУРСКИС АЛЬГИРДАС БРОНИСЛАВОВИЧ

МПК / Метки

МПК: H03K 5/153

Метки: импульсов, формирователь

Опубликовано: 23.11.1981

Код ссылки

<a href="https://patents.su/3-884110-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Устройство для временного разделения двух импульсных сигналов

Следующий патент: Устройство задержки

Случайный патент: Специализированная микроэвм