Устройство для вычисления функции е

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

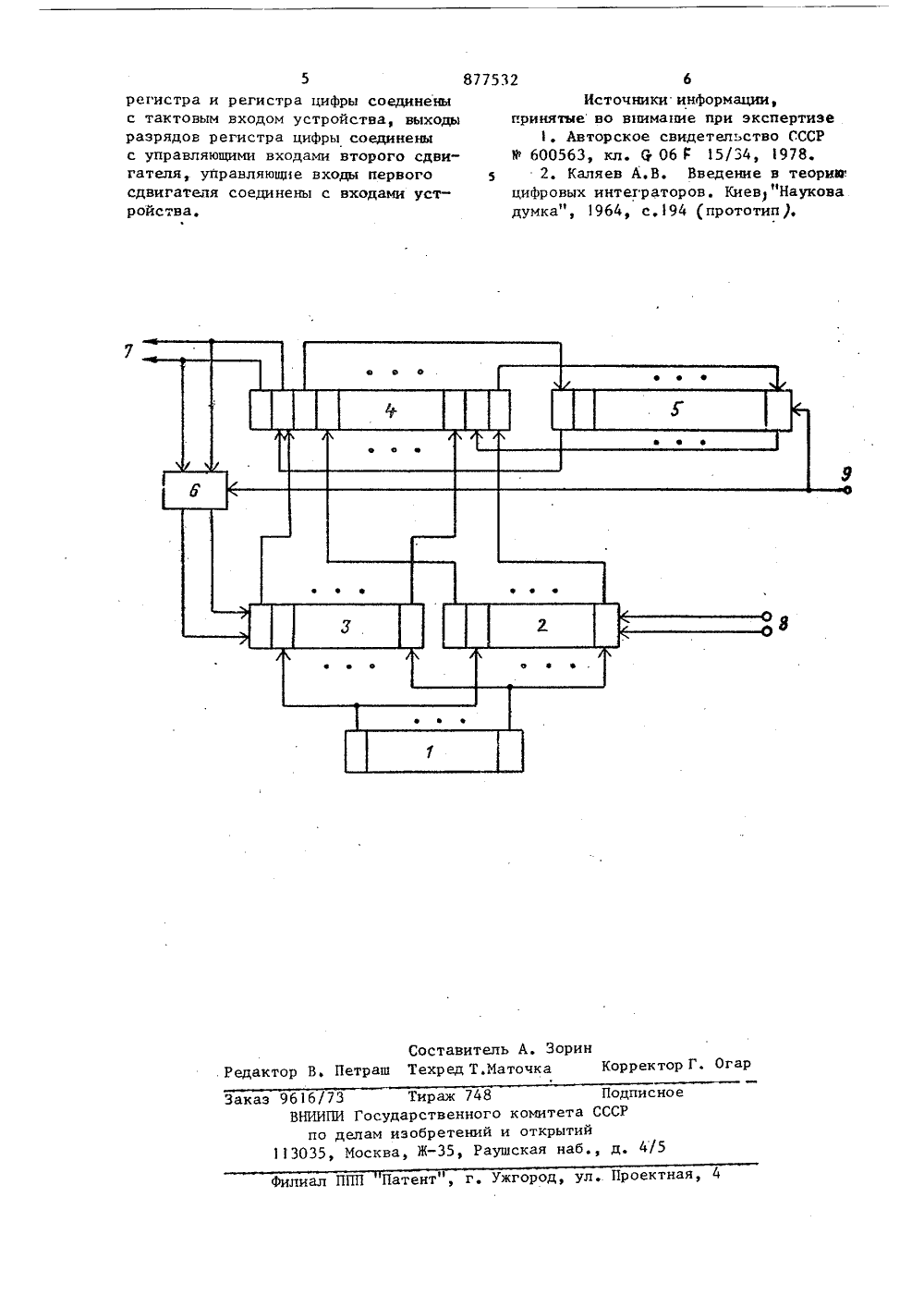

Союз СоветскикСоциалистичвскикРеслублик ОП ИСАНИИ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТИЗЬСТВУ и 877532(23) Приоритет 6 06 Р 7/556 Ввударвтаакай квиитвт СССР ао двлви квабрвтеинй и открытий(72) Авторы изобретения Киевский ордена Ленина политехнический институт им 50-летия Великой Октя 5 фьской социалистической революции(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ е Изобретение относится к цифровойвычислительной технике и может быть применено в специализированных вычислительных устройствах.Известно устройство для вычисленияфункции е , содержащее регистры,счетчики, сумматоры, логические злементы 11,Однако указанное устройство ввидубольших аппаратных затрат и низкого.10быстродействия нецелесообразно приме"нять в тех случаях, когда требуетсяполучить значения е для некоторойвозрастающей последовательности значенийХ . = Х + Е Ъ,(, 1 = ( ,1 к)1Наиболее близким по техническойсущности к предлагаемому является уст.ройство, содержащее и-разрядный регистр приращений, где и - разрядностьприращения аргумента), (и+1) - разрядный первый сдвнгатель и и+4)разрядный сумматор 121. Недостатком известного устройства является то, что для вычисления функ-хции е в Й точках требуется выполнить Н шагов, длительность каждого из которых равна времени трех сложений и одного умножения, а также низкое быстродействие.Цель изобретения - увеличение быстродействия.Поставленная цель достигается тем, что в устройство, содержащее и-разрядный регистр приращений (где и- раз рядность приращения аргумента),(и+1) разрядный первый двигатель и (а+4)- разрядный сумматор, дополнительно вве. дены второй (и+1) - разрядный сдвига- тель, (и+2) - разрядный воспомогательный регистр и двухразрядный рет гистр цифры, причем выход 1-го разря;. да регистра приращений (1=1,2 + +и) подключен к (1+1)-му входу перво. го и второго сдвигателей, выход )-го разряда первого сдвигателя =1,2, и+1) подключен к (1+3)-му разряду=1,2п+2) подключен ко входу 1-гсвыход ю -го разряда вспомогательного регистра (щ 1,2. . .и+2)соединен со входом(в=1,2п+2) соединен со входом(в+1)-го разряда сумматора, выходыпервого и второго разрядов которогосоединены со входами первого и второго разрядов регистра цифры и выходами устройства, управляющие входывспомогательного регистра и регистрацифры соединены с тактовым входом устройства, выходы разрядов регистрацифры соединены с управляющими входа.ми второго сдвигателя, управляющиевходы первого сдвигателя соединеныс входами устройства,20На чертеже представлена блок-схема устройстваУстройство содержит регистр 1 приращений, сдвигатели 2 и 3, сумматор4, вспомогательный регистр 5 и ре-.гистр 6 цифры, выходы 7-; входы 8, тактовый вход 9.Устройство работает следующим образом.В исходном состоянии в регистреприращения 1 записан код величины1- %/2, где Ь удовлетворяет условию2/3(1, а в регистрах 5 и б записаны нули. Формула изобретения В каждом 1-ом цикле вычисления на входы 8 поступает цифра у операнда У имеющая вес 2 где М - количество разрядов, после которых Фиксируется запятая в УИ 4, и принимаацая значение из множества 0,1,2;, Цифра у управляет работой сдвигател 2 таким образом что последний осуществляет передачу кода регистра 1 со сдвигом на один разряд влево, если у =2, без сдвига, если у =1, и код регистра не выдается, если у =О. Аналогичным образом цифра, записанная в регистре 6, управляет работой сдвигателя 3. В сумматоре 4 складываются коды, поступающие с регистра 5 и сдвигателей 2 и 3 и в двух его старших разрядах формируетйя и выдается на выходы 7 цифра результата У 4, имеющая вес 21 ф". Цикл заканчивается сигналом по тактовому входу 9, по которому код двух старших разрядов сумматора 4 принимается на регистр 6, а,код 30 35 40 45 50 55 2остальных разрядов заносится и регистр 5.Устройство позволяет формировать на выходе значения искомой Функции и (И+1) -й точке с задержкой на один цикл относительно ввода в устройство соответствующих разрядов функции в К-й точке. Это позволяет при последовательном соединении устройств приступать к выполнению очередного шага не после окончания предыдущего шага, а непосредствен" но после получения первых разрядов результата этого шага. Таким образом, процессы интегрирования на й, И+1, Я+2)-м и т.д, шагах при исполь. зовании предлагаемого устройства могут быть совмещены во времени, и время выполнения М шагов составитТ=(2 М+ +И)1 Ггде и - разрядность представления Функций 6 - время суммирова) Ения, а среднее время выполнения одного шага интегрирования при достаточно большом количестве шагов М практически не зависит от разрядности Функций и стремится к ТС =21,СР Устройство для вычисления функции -у,е , содержащее и-разрядный регистр приращений (где и - разрядность приращения аргумента), п+1) - разрядный первый сдвигатель и (и+4) - разрядный сумматор, о т л и ч а ю щ е е с ятем, что, с целью повышения быстро"действия, в него введены второй (и+1)разрядный. сдвигатель, (и+2) -разрядный вспомогательный регистр и двухразрядный регистр цифры, причем выход 1-го разряда регистра приращений(1=1,2п) подключен к 1+1)-мувходу первого и второго сдвигателей,выход )-го разряда первого сдвигателя (1=1,2,р+1) подключен к (+3)разряду сумматора, выход -го разряда второго сдвигателя (1=1,2 п+1)подключен к (1+1)-му разряду сумматора, выход (1+2)-го разряда которого (1=1,2 и+2) подключен ко входу 1-го разряда вспомогательногорегистра, выход а-го разряда вспомогательного регистра (в=1,2,. и+2)соединен со входом (а+1)-го разрядасумматора, выходы первого и второгоразрядов которого соединены со входами первого и второго разрядов ре-.гистра цифры и выходами устройства,управляющие входы вспомогательного. Редак Под тета СССРТираж 748 Государственного елам изобретений Москва, Ж, Рауш сно аказ 9616/7 ВНИИПИ по 113035, ткрыт 4/ я на филиал ППП Патент", г. Ужгород, ул, Проектна регистра и регистра цифры соединеныс тактовым входом устройства, выходыразрядов регистра цифры соединеныс управляющими входами второго сдвигателя, управляющие входы первогосдвигателя соединены с входами устройства,6Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРФ 600563, кл. 9 06 Г 15/34, 1978.2. Каляев А.В. Введение в теориюцифровых интеграторов. Киев 1"Науковадумка", 1964, с.94 (прототип ),

СмотретьЗаявка

2841359, 14.11.1979

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50 ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

ЖАБИН ВАЛЕРИЙ ИВАНОВИЧ, КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, КОЗАК ВЛАДИМИР СИДОРОВИЧ, ПОКАРЖЕВСКИЙ АЛЕКСАНДР СЕРГЕЕВИЧ, СКОЧКО АЛЕКСАНДР ПЕТРОВИЧ, ТАРАСЕНКО ВЛАДИМИР ПЕТРОВИЧ, ШВЕЦ ЕВГЕНИЙ МИХАЙЛОВИЧ, ЩЕРБИНА АЛЕКСАНДР АНДРЕЕВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, функции

Опубликовано: 30.10.1981

Код ссылки

<a href="https://patents.su/3-877532-ustrojjstvo-dlya-vychisleniya-funkcii-e.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции е</a>

Предыдущий патент: Устройство для вычисления функции z= х +у

Следующий патент: Генератор псевдослучайных последовательностей

Случайный патент: Устройство для определения максимального и минимального из п чисел, представленных в системе остаточных классов