Устройство для определения максимального и минимального из п чисел, представленных в системе остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 603987

Авторы: Полисский, Факторович

Текст

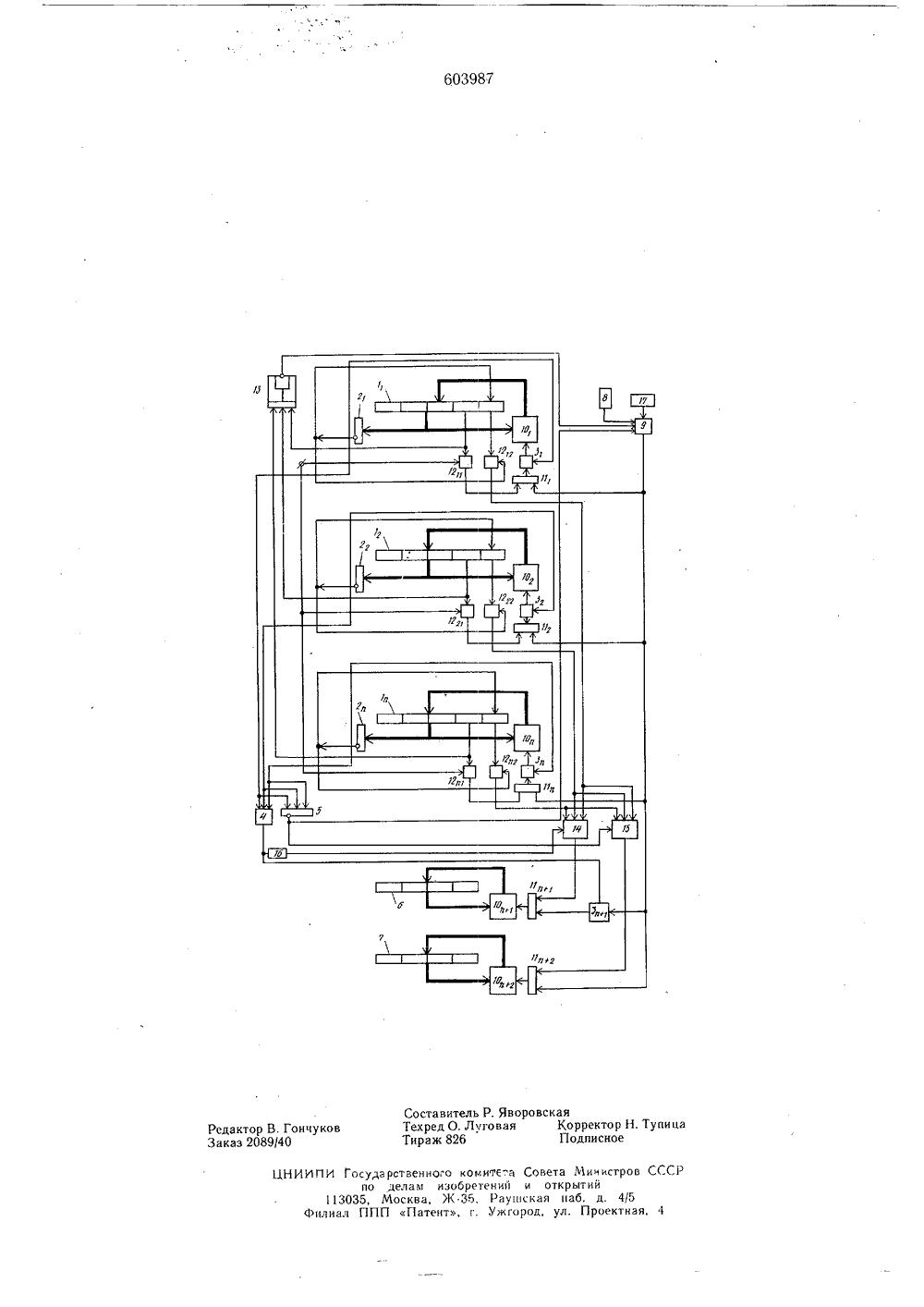

01) 603987 Союз СоветскихСоциалистическихРеспублик ОП ИСАНИЕ ИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(5 3 1 8-24 7/04 Государственный комитет Соввтв Министров СССР по делан изобретений и открытий23) Приоритет43) Опубликовано 25.04.78545) Дата опубликования оп 53) У юллетень1 д ания Я,ОЦ.И 681.32 088.8)(72) Авторы изобретения М. Г, Факторович и Ю. сскии 71) Заявитель Научно-исследовательский автоматизации черно 4) УСТРОЙСТВО ДЛ И МИНИМАЛЬН В СИСТЕМЕ ОС ОПРЕДЕЛЕ О ИЗУЧИ АТОЧНЫХ Изобретение отки и вычислительиспользовано дляавтоматики и цифрнах, работающихсов,нен с одним из мента И, друго ходом и-входно Недостатко ствие, обуслов результата сра личество такто наибольшего ч Целью изоб стродействия увходног единен о элсроден чения ть ко чению Извести ставле ржаще ви е бь Это достигается тем, что в предложенное устройство введены (п + 2) сумматоров, (п 2) входных элементов ИЛИ, и пар выходных элементов И, второй и-входовой элемент ИЛИ-НЕ, две схемы сравнения, элемент задержки, блок памяти, причем выходы и сумматоров соединены с первыми входами соответствующих регистров сравниваемых чисел, первые и вторые выходы которых соединены со входами соотвстствующих сумматоров и выходных элементов ИЛИ - НЕ, инверсные выходы которых соединеныы со вторыми входами соответствующих разрядов регистров сравниваемых чисел и с одним из входов второго из каждой пары выходных элементов И, выходы которых соединены с и входами первой и второй схем сравнения, (и+ 1) -ный вход первой из которых через элсносится к области автоматиной техники и может быть обработки данных в схемах овых вычислительных маши- в системе остаточных класо устройство для сравнения чи нных в системе остаточных клас е регистры сравниваемых чисе нени я. Недостатком его является то, что оно поз 10 воляет лишь устанавливать совпадение или несовпадение двух чисел по величине и вследствие этого не дает представления об их количественном соотношении (больше, меньше, равно). 15Наиболее близким техническим решением к предложенному является устройство, содержащее и регистров сравниваемых чисел, и выходных элементов ИЛИ - НЕ, прямые выходы которых соединены с первыми входами соответствующих входных элементов И, со входа 20 ми и-входового элемента И и со входами первого и-входового элемента ИЛИ-НЕ, регистры наибольшего и наименьшего числа, генератор, выход которого соединен с одним из входов управляющего элемента И, выход которого соеди опытно-конструкторский институеталлургии НИЯ МАКСИМАЛЬНОГОСЕЛ ПРЕДСТА ВЛЕННЫ ХКЛАССОВ2входов (и + 1)-гой вход которого сого элемента И.м его является низкое быственное тем, что для полвнения необходимо затратв, равное абсолютному знаисла.ретения является повышенстройства.мент задержки соединен с выходом п-входового элемента И, а (п+1)-ный вход второй схемы сравнения соединен с инверсным выходом первого п-входового элемента ИЛИ-НЕ, вторые и третьи выходы регистров сравниваемых чисел соединены со входами соответствующих пар, выходных элементов И, а вторые выходы регистров сравниваемых чисел соединены также со входами второго п-входового элемента ИЛИ - НЕ, инверсный выход которого соединен со вторым входом управляющего элемента И, третий вход которого соединен с прямым выходом первого п-входового элемента ИЛИ - НЕ, выход каждого первого из пары выходных элементов И соединен с одним их входов соответствующих входных элементов ИЛИ, вторые входы которых соединены с выходом управляющего элемента И, а выходы каждого входного элемента ИЛИ через соответствующие входные элементы И соединены с третьими входами соответствующих сумматоров, выходы (и + 1) -ого и (п + 2) -ого сумматоров соединены со входами регистров наименьшего и наиболь шего числа, выходы которых соединены с первы ми входами (п+1)-ого и (п+2)-ого сумматора, вторые входы которых соединены с выходами соответствующих входных элементов ИЛИ, первые входы которых соединены соответственно с выходами первой и второй схемой сравнения, а вторые входы соответственно - с выходом (и+1)-ого входного элемента И и через управляющий элемент И - с выходом блока памяти.На чертеже схематически изображено предложенное устройство.Оно содержит регистры сравниваемых чисел 1 ,1,1 выходные элементы ИЛИ - НЕ 2.2;,2., входные элементы И 3 33, п-входовой элемент И 4, первый п-входовой элемент ИЛИ - НЕ 5, регистры наименьшего и наибольшего числа 6 и 7, генератор 8, управляющий элемент И 9, сумматоры 10 10,10, 10 10 входные элементы ИЛИ 11 11,11, 11,.11 пары выходных элементов И 12 122,122122,.,1212 второй и-входовой элемент ИЛИ - НЕ 13, первую и вто рую схемы сравнения 14 и 15, элемент задержки 16 блок памяти 17.Работа устройства для определения максимального и минимального из п чисел, представленных в системе остаточных классов, заключается в следующем.Сравниваемые числаА)= (а(,агр:,; )А 2= (Гх( а 2" ащ )А = (а" аг" а" )представим в видеА =КР + (х,А 2= К 2 Рт+ алА = К,Р+ а,отличаются значениями К и а (1 = 1,2,п) (1). Если из каждого числа вычесть свой остаток а от деления числа на модуль Р полученные числа .,)Д, - йф = К,РА - а = КРАп - а"= К, Р кратны Р,и отличаются одно от другого количеством Р содержащимся в числах.Если затем вычитать из сравниваемых чисел Р, в нуль раньше других обратится наименьшее из чисел. Значения а .а 2ат лп 1 тне играют роли в случае не одновременного обнуления сравниваемых чисел, так как а"(РВ случае одновременного обращения в нульнескольких чисел, наименьшим из них будетчисло с наимень 1 пим а", наибольшим - числос наибольшим Ы"К моменту начала сравнения в регистрахсравниваемых чисел 1 ,1;,,1 записаны сравниваемые числа. На выходах выходных элементов ИЛИ - НЕ 2 п 222, имеется единичныйсигнал, свидетельствующий о неравенстве сравниваемых чисел нулю,Управляющий элемент И 9 закрыт, так какотсутствует сигнал на его третьем входе (хо 20 тя бы один из остатков, записанных в гп - хразрядах регистров сравниваемых чисел, неравен нулю),На выходах и входах элементов И 4 иИЛИ - НЕ 5 имеется сигнал. На входы схемсравнения 14 и 15 остатки, записанные в(ш + 1)-ных разрядах регистров сравниваемых чисел, не поступают, так как закрыты выходные элементы И 1211212, (на вторых входах этих схем сигналы отсутствуют).После включения единичный импульс появляется на первых входах выходных элементов И,121 ,1212 , разрешая перезапись соде ржимого тп-ных разрядов регистров сравниваемых чисел через выходные элементы ИЛИ11 ,1 211., и открытые входные элементыИ 3 ,3, ,Зп на входы сумматоров 10 ,10,10где осуществляется вычитание А - аюПосле перезаписи результатов вычитанияв регистры сравниваемых чисел содержимоетп-ных разрядов всех регистров становится равным нулю и на выходе второго и-входового4 О элемента ИЛИ - НЕ 13 появляется сигнал, Управляющий элемент И 9 открывается, и, на входы сумматоров поступают значения Р с частотой генерации. Частоту генератора выбирают такой, что следующая подача значения Рна входы сумматоров осуществляется после пе 45 резаписи результатов действий сумматоров всвои регистры.Сумматоры 10,1010 осуществляют вычитание А - а,- 1 с р., а сумматоры 10, и10,. складывают поступающие на их входю чилаПроцесс вычитания - сложения продолжается до тех пор, пока одно или несколькочисел одновременно не станут равными нулю.В этот момент на инверсном выходе выходного элемента ИЛИ - НЕ 21 (1=1,2п) об 5 нулившегося регистра появляется сигнал и значение а,поступает на вход первой схемы сравнения 14, которая перезаписывает результатсравнения (в случае обнуления нескольких чисел) или само это число в сумматор 10,.При обнулении одного из регистров исчезает сигнал с выхода п-входового элемента И 4,а через элемент задержки 16 с некоторой задержкой он исчезает на (п+1) входе первой схемы сравнения 14, в результате чего нс осуществляется дальнейшее сравнение чисел в первой схеме сравнения 14.Исчезновение сигнала с выхода п-входового элемента И 4 приводит к закрыванию входного элемента И 3,., в результате чего в регистре наименьшего числа 6 оказывается записанным наименьшее из сравниваемых чисел.Единичный сигнал, появившейся на инверсном выходе соответствующего выходного элемента ИЛИ - НЕ 2 22 сбрасывает в нуль содержимое дублирующего (гп+ 1) -ого разряда своего регистра.Процесс вычитания р, продолжается до тех пор, пока не обнулятся все числа, а значит, и наибольшее из сравниваемых. В этот момент на (и+1) -ном входе второй схемы сравнения 15 появляется сигнал и сравниваются на, максимум остатки о, чисел, обнулившихся 20 в этом такте. Результат сравнения через входной элемент ИЛИ 1 .перезаписывается в сумматор 10,В регистре 7 наибольшего числа оказывается записанным наибольшее из сравниваемых чисел. Исчезновение сигнала на прямом выходе первого п-входового элемента ИЛИ в5 при- Иводит к закрытию управляющего элемента9, что обеспечивает непоступление значения О, , на входы сумматоров. Предложенное устроиство при незначитель-,Озо ных аппаратурных затратах резко повышает скорость группового сравнения чисел, выраженных в системе остаточных классов. 35 Формула изобретении Устройство для определения максимального и минимального из и чисел, представленных в системе остаточных классов, содержащее и регистров сравниваемых чисел, п выходных элементов ИЛИ-НЕ, прямые выходы которых соединены с первыми входами соответствуюших входных элементов И, со входами и-входового элемента И и со входами первого п-входового элемента ИЛИ-НЕ, регистры наибольшего и наименьшего числа, генератор, выход которого соединен с одним из входов управляюшего элемента И, выход которого соединен с одними из входов (п+ 1) -ого вкодного элемента 11, другой вход которого соединен с выкодом и-вхо дового элемента И, отличающееся тем, что, с целью повышения быстродействия, в устройство дополнительно введены (п+2) сумматоров, (и+ 2) входных элементов ИЛИ, п пар выходных элементов И, второй и-входовой элемент ИЛИ-НЕ, две схемы сравнения, элемент задержки, блок памяти, причем выходы п сумо маторов соединены с первыми входами соответствующих регистров сравниваемых чисел, первые и вторые выходы которых соединены со входами соответствуюших сумматоров и выходных элементов ИЛИ-НЕ, инверсные выходы которых соединены со вторыми входами соответствующих разрядов регистров сравниваемых чисел и с одним из вкодов второго изнкаждои пары выходных элементов И, выкоды которых соединены с и входами первой и второй скем сравнения, (и+1)-ный вход первой из которык через элемент задержки соединен с выходом и-входового элемента И, а (и + 1)- ный вход второй схемы сравнения соединен с инверсным выкодом первого и-входового элемента ИЛИ - НЕ, вторыс и третьи выкоды регистров сравниваемых чисел соединены со входами выходных элементов И соответствуюшик пар, а вторые выходы регистров сравниваемых чисел соединены со входами второго и-вкодового элемента ИЛИ - НЕ, инверсный выход которого соединен со вторым входом управляющего элемента И, третий вход которого соединен с прямым выходом первого п-входового элемента ИЛИ - НЕ, выход каждого первого из пары выходных элементов И соединен с одним из входов соответствующих входных элементов ИЛИ, вторые входы которых соединены с выходом управляющего элемента И, а выходы каждого входного элемента ИЛИ через соответствующие входные элементы И соединены с третьими входами соответствующих сумматоров, выходы (п + 1)-ого и (и + 2)-ого сумматоров соединены со входами регистров наименьшего и наибольшего числа, выходы которых соединены с первыми входами (п + 1) -ого и (и + 2 ого сумматора, вторые входы которых соединены с выходами соответствующих входных элементов ИЛИ, первые входы которых соединены соответственно с выходами первой и второй схемой сравнения, а вторые входы соответственно - с выходом (п + 1)-ого вкодного элемента И и через управляющий элемент И - с выходом блока памяти,603987 Составитель Р. Яворовская Техред О. Луговая К Тираж 826 П ге"а Совета Ь ений и открь Раушская наб Ужгород, ул. ОНИИПН Г 0 1 Фнлго ком зобрет )К-ЗБ, т, г. ректор Н. Тупицадписное министров СССтийд. 4/5Проектная, 4

СмотретьЗаявка

2336498, 22.03.1976

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ И ОПЫТНОКОНСТРУКТОРСКИЙ ИНСТИТУТ АВТОМАТИЗАЦИИ ЧЕРНОЙ МЕТАЛЛУРГИИ

ФАКТОРОВИЧ МИХАИЛ ГРИГОРЬЕВИЧ, ПОЛИССКИЙ ЮРИЙ ДАВИДОВИЧ

МПК / Метки

МПК: G06F 7/04

Метки: классов, максимального, минимального, остаточных, представленных, системе, чисел

Опубликовано: 25.04.1978

Код ссылки

<a href="https://patents.su/4-603987-ustrojjstvo-dlya-opredeleniya-maksimalnogo-i-minimalnogo-iz-p-chisel-predstavlennykh-v-sisteme-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения максимального и минимального из п чисел, представленных в системе остаточных классов</a>

Предыдущий патент: Устройство для сравнения двоичных чисел

Следующий патент: Устройство для извлечения корня третьей степени

Случайный патент: Автоматический отрезной станок для разрезки металлических, в частности, ферроникелевых, трубок