Устройство устранения неоднозначностифазы сигнала

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

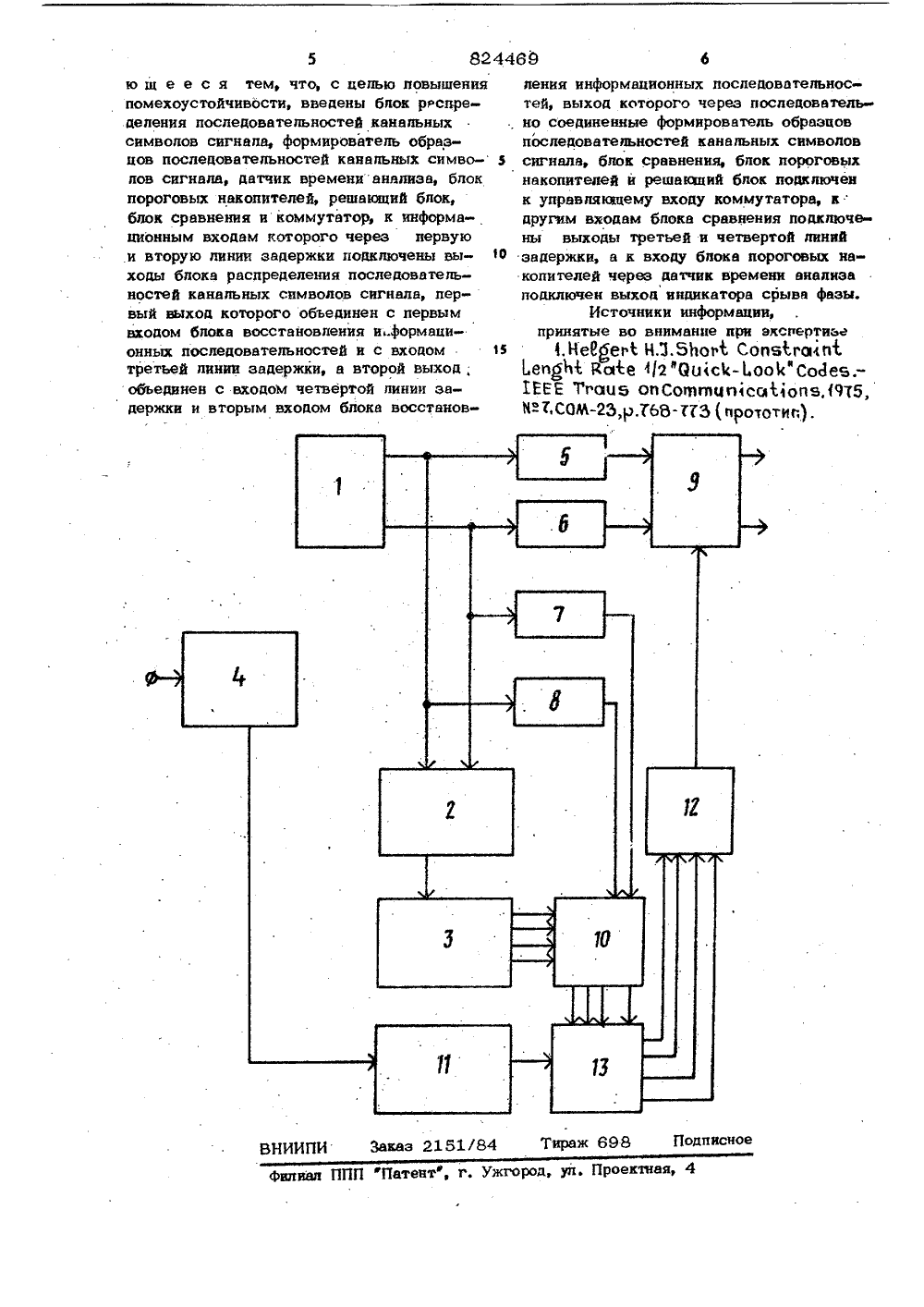

ОП ИСАНИЕИЗОБРЕТЕНИЯК . АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистнческихРеепубпнк1824469 1(22) Заявлено 03.07.79 (21) 2788284/18-09с присоединением заявки Люйвударствввай комитет СССР дв девам изобретвхиЯ в етхрмткЯ(53 У УДК 621.394, 66 2 (088 8) Дата опубликования описания 23.04.81 Авторыизобрете кет и А Одесский электротехнический институт свя им. А. С. Попова2 св ана чны ровазы, спе то р-:м Изобретение относится к электро я-эи и может использоваться в системах передачи дискретной информации по, к пам с неоднозначностью фазы и сверто м кодированием.Известно устройство устранения неоднозначности фазы сигнала в системе с фаэовой манипуляцией и сверточным копи кием, содержашее индикатор срыва фа блок восстановления информационных по доватепьностей и четыре линии заде жки 1.Однако известное устройство и еет недостаточную помехоустойчивость.Цель изобретения - повышение помехо 15 устойчивости.Поставленная цепь достигается тем, что в устройство устранения неоднозначности фазы сигнала в системе с фазовой манипуляцией с сверточным кодированием, содержашее индикатор срыва фазы, блоквосстановления информационных поспеткеатепьностей и четыре линии задержки, введены блок распределения последоватедьностей канальных символов сигнала, формирователь образцов последовательностей анапьных символов сигнала, датчик временианализа, блок пороговых накопителей, решающий блок, блок сравнения и коммутатор, к информационным входам которогочерез первую и вторую линии задержкиподключены выходы бпока распределенияпоследовательностей канальных символовсигнала, первый выход которого объединен с первым входом бпока восстановления информационных последовательностейи с входом третьей линии задержки, авторой выход объединен,. с входом четвертой линии задержки и вторым входомблока восстановления информационных поспедоватепьностей, выход которого черезпоследовательно соединенные формирователь образцов последовательностей канальных симвопов сигнала, блок сравнения, бпок пороговых накопителей и решаюший бпок подключен к управпякхцему входукоммутатора, к другим входам бпока сравнения подкпючены выходы третьей и чет824469 4которого подключены к выходам бпока 13, подает соответствующий сигнал на управляющий вход коммутатора 9, входы которого подключены последовательно через линии 5 и 6 задержки, в которых принятые последовательности задерживаются навремя анализа; к выходам блока 1 распределения последовательностей канальных символов сигнала. С выхода коммутатора 9 последовательности в правильной фазе поступают на вход декодера сверточного кода ( на чертеже не показан), Если превышение порогов (при сильных шумах в канале) происходит во всех накопитея, 1 пях блока 13, то решающий бпок 12 непринимает нового решения, до окончания й, следующих Ю тактов анализа. Такой алгоритм работы решающего блока 12 существенно повышает помехоустойчивостьщ устройства устранения неоднозначности фазы. В отсутствии перескоков фазы,анализ х принимаемых последоватейьностей канальо- ных символов производится с периодомв И тактов, есаИ произойдет перескок фазы, то с выхода индикатора 4 срыва фа зы, вход которого подключен к схеме формирования опорного колебания демодулятора сигналов фазовой манипуляции (на чера- теже не показан), на вход датчика 11зовремени анализа поступает сигнал, и отсчет времени анализа начнется с момента окончания процесса перескока.Если в декодере сверточного кода применяется гибкое решение (квантование сигль- налов на выходе демодулятора), то устройство устранения неоднозначности фазы должно содержать копичество линий задержки (аналогичных линиям 5 и 6 задержки), равное количеству уровней квантования, и несколько более сложный комму 40 .татор 9. Само устройство продолжаетработать на основнии жесткого решения. вертой линии задержки, а к входу бпока . пороговых накопителей через датчик времени анализа подключен выход индикатора срыва фазы,На чертеже представлена структурная электрическая схема предлагаемого устройства.Устройство содержит бпок 1 распреде пения последовательностей канальных сим волов сигнала, блок 2 восстановления информационных последовательностей, формирователь 3 образцов последовательностей канальных символов сигнала, индикатор 4 срыва фазы, пинии 5, 6, 7 и 8 за держки, коммутатор 9, блок 10 сравнени датчик 11 времени анализа, решающий блок 12 и блок 13 пороговых накопителеУстройство работает следующим образом.Последоватепьности принимаемых канапьных символов с выхода блока 1 распредепения последовательностей канапьны символов сигнала поступают на входы бл ка 2 восстановления информационных последовательностей, состоящего из инверс ных схем, на выходе которого формируют ся возможные варианты информационных последовательностей. Сформированные информационные последовательности поступ ют на входы формирователя 3 образцов последовательностей канапьных символов сигнала, состоящего нз сверточных кодеров поспедоватепьно соединенных с преобразователями, на выходах которого формируются врэможные варианты последовате ностей канальных символов, одна пара нэ которых совпадает (при .отсутствии ошибок в канале) с принятой канальной последовательностью. Сформированные образцы в бпоке,10 сравнения сравниваются с принятыми канальными последова тельностями, поступающими с выходов блока 1 распределения последовательностей канапьных символов сигнала и задер - жанными в линиях 7 и 8 задержки на время обработки информации в блоке 2 вос становления информационных последовательностей и в формирователе 3 образцов последовательностей канальных символов сигнала. Результаты сравнения накапливаются в блоке 13 пороговых накопителей за 50 М тактов анапиза. После окончания анализа, в накопителе, соответствующим положению фаэы колебания схемы формирования опорного колебания относительно фазы генератора на передаче, порог превышен 55 не будет, а в остальных накопителях произойдет превьпдение порога, На основе этих данных, решающий блок 12, входы Предлагаемое устройство по сравнению с известным за счет уменьшения времени установления синфазного режйма работы устройства устранения неоднозначности обладает более высокой помехоустойчивостью,Формула изобретения Устройство устранения неоднозначности фазы сигнала в системе с фазовой манипуляцией и сверточным кодированием, содержащее индикатор срыва фазы блок восстановления информационных последовательностей и четыре пинии, о тл и ч а -

СмотретьЗаявка

2788284, 03.07.1979

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТСВЯЗИ ИМ. A. C. ПОПОВА

БАНКЕТ ВИКТОР ЛЕОНИДОВИЧ, ЛЯХОВ АЛЕКСАНДР ИВАНОВИЧ

МПК / Метки

МПК: H04L 7/04

Метки: неоднозначностифазы, сигнала, устранения

Опубликовано: 23.04.1981

Код ссылки

<a href="https://patents.su/3-824469-ustrojjstvo-ustraneniya-neodnoznachnostifazy-signala.html" target="_blank" rel="follow" title="База патентов СССР">Устройство устранения неоднозначностифазы сигнала</a>

Предыдущий патент: Устройство синхронизации

Следующий патент: Автоселектор периодической последо-вательности импульсов

Случайный патент: Многоканальное устройство для приема дискретной информации