Логический модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 813409

Авторы: Борисенко, Гольбрайх, Макаровский, Фирсов, Шабельский

Текст

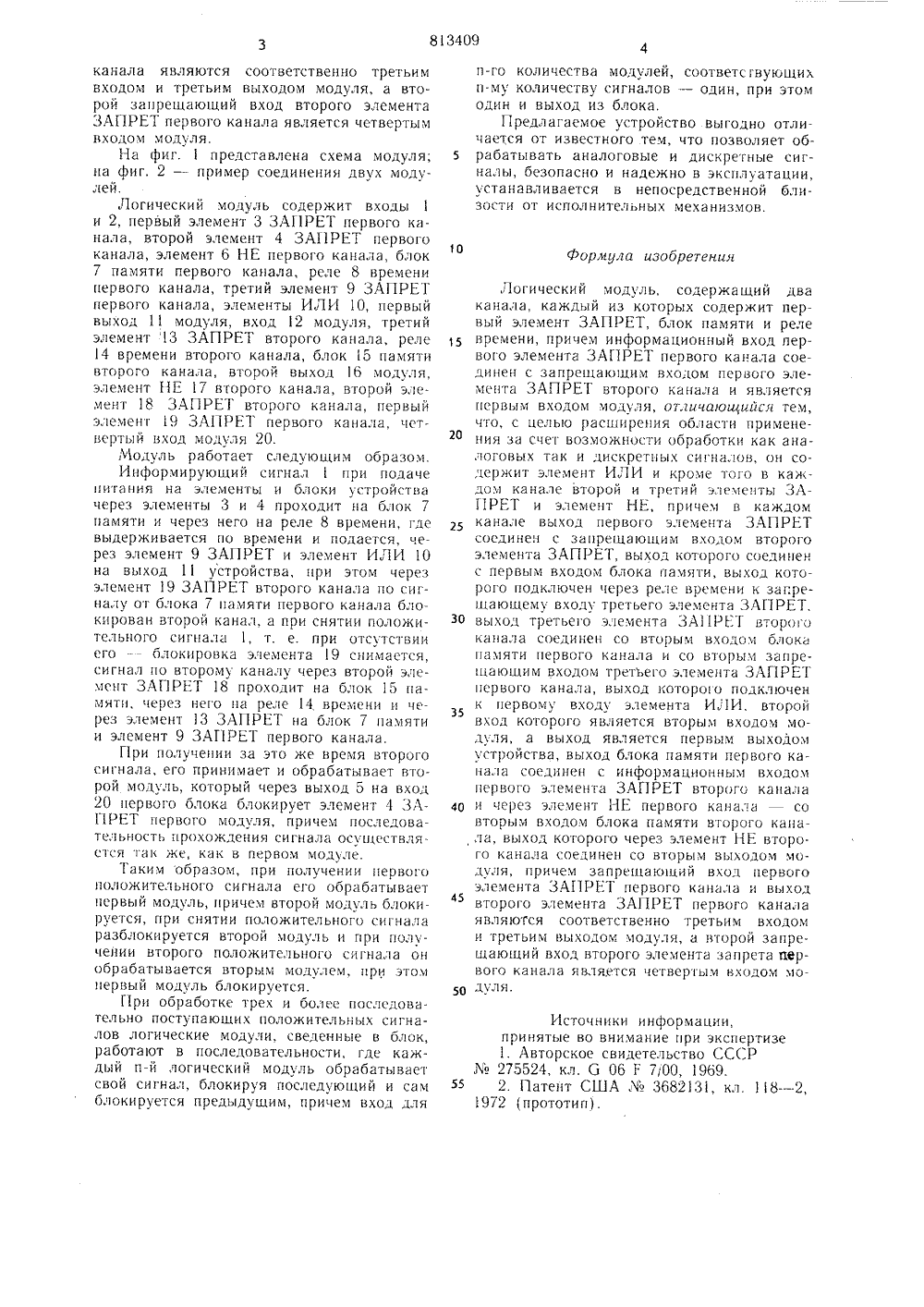

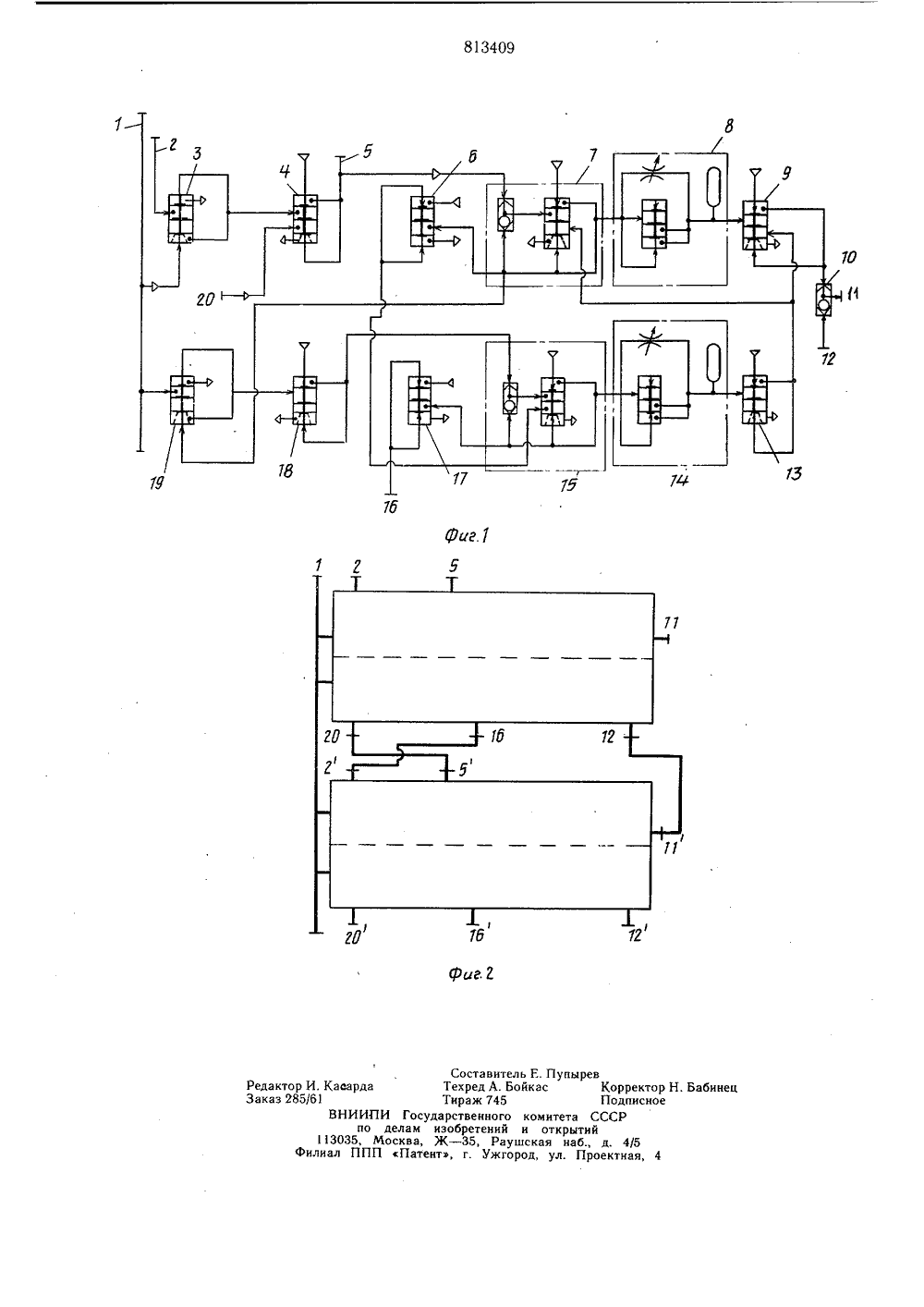

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик пц 813409(51) М. Кл.з б 06 Г 7/00 Государственный комитет Опубликовано 15.03,81. Бюллетень 10Дата опубликования описания 25.03.81 до делам изобретений и открытий(72) Авторы изобретени К. Фирсов Шабельский, В. 3. Гольб и А. Л. Макаровски Проектный институт Хотьковског 1 ст,4 ънаучно-производственного объединения Лакофаспощытйе витсл 4) ЛОГИЧЕСКИИ" МОДУЛ Изобретение относится к управлению технологическими процессами и может быть использовано, например, для управления процессом нанесения покрытий с помощью пнев мор аспылителей.Известен логический модуль, содержатций элементы И, ИЛИ, НЕ 11Недостатком его является невозможность обработки аналоговых сигналов.Наиболее близким по технической сущности и достигаемому результату к предлагаемому является логический модуль, содержащий два канала, каждый из которых содержит первый элемент ЗАГ 1 РЕТ, блок памяти и реле времени, причем информационный вход первого элемента ЗАПРЕТ первого канала соединен с запрещающим входом первого элемента НЕ второго канала и является первым входом модуля, имеющего сенсорные датчики(21.Недостатком его является невозможность отрабатывать аналоговые сигналы.Цель изобретения - расширение области применения за счет возможности обработки как аналоговых так и дискретных сигналов. Поставленная цель достигается тем, чтологический модуль содержит элемент ИЛИ и кроме того в каждом канале второй и третий элементы ЗАПРЕТ и элемент НЕ, причем в каждом канале выход первого элемента ЗАПРЕТ соединен с запрещающим входом второго элемента ЗАПРЕТ, выход которого соединен с первым входом блока памяти, выход которого подключен через реле времени к запрещающему входу третьего элемента ЗАПРЕТ, выход третьего элето мента ЗАПРЕТ второго канала соединен совторым входом блока памяти первого канала и со вторым запрещающим входом третьего элемента ЗАПРЕТ первого канала, выход которого подключен к первому входу элемента ИЛИ, второй вход которого является вторым входом модуля, а выход является первым выходом устройства, выход блока памяти первого канала соединен с информационным входом первого элемента ЗАПРЕТ второго канала и через элемент НЕ первого20 канала - со вторым входом блока памятивторого канала, причем запрещающий вход первого элемента ЗАПРЕТ первого канала и выход второго элемента ЗАПРЕТ первогоФор игг,га изобретения 5 О канала являются соответственно третьим входом и третьим выходом модуля, а второй запрещающий вход второго элемента ЗАПРЕТ первого канала является четвертым входом модуля.На фиг. 1 представлена схема модуля; на фиг. 2 - пример соединения лвух модулей.Логический модуль содержит входыи 2, первый элемент 3 ЗАПРЕТ первого канала, второй элемент 4 ЗАГ 1 РЕТ первого канала, элемент 6 НЕ первого канала, блок 7 памяти первого канала, реле 8 времени первого канала, третий элемент 9 ЗАПРЕТ первого канала, элементы ИЛИ 10, первый выход 11 модуля, вход 12 модуля, третий элемент 13 ЗАПРЕТ второго канала, реле 14 времени второго канала, блок 15 памяти второго канала, второй выход 16 модуля, элемент НЕ 17 второго канала, второй элемецт 18 ЗАПРЕТ второго канала, первый элемент 19 ЗАПРЕТ первого канала, четвертый вход модуля 20.Модуль работает следующим образом.Информирующий сигнал 1 при подаче питания на элементы и блоки устройства через элементы 3 и 4 проходит на блок 7 памяти и через него на реле 8 времени, где выдерживается по времени и подается, через элемент 9 ЗАПРЕТ и элемент ИЛИ 1 О на выход 11 устройства, цри этом через элемент 19 ЗАПРЕТ второго канала по сигналу от блока 7 памяти первого канала блокирован второй канал, а при снятии положительного сигнала 1, т. е. при отсутствии его -- блокировка элемента 19 снимается, сигнал по второму каналу через второй элемент ЗАПРЕТ 18 проходит на блок 15 памяти, через него ца реле 14 времени и че)ез элемент 13 ЗАПРЕТ на блок 7 памяти и элемент 9 ЗАПРЕТ первого канала.Г 1 ри получении за это же время второго сигнала, его принимает и обрабатывает второй модуль, который через выход 5 на вход 20 первого блока блокирует элемент 4 ЗАПРЕТ первого модуля, причем последовательность прохождения сигнала осуществляется так же, как в первом модуле.Таким образом, при получении первого положительного сигнала его обрабатывает первый модуль, причем второй модуль блокируется, при снятии положительного сигнала разблокируется второй модуль и при получении второго положительного сигнала он обрабатывается вторым модулем, цри этом первый модуль блокируется.Г 1 ри обработке трех и более последовательно поступающих положительных сигналов логические модули, сведенные в блок, работают в последовательности, где каждый и-й логический модуль обрабатывает свой сигнал, блокируя последующий и сам блокируется предыдущим, причем вход для г 5 2 о 25 зо 35 40 45 и-го количества модулей, соответствующих п-му количеству сигналов - один, при этом один и выход из блока.Предлагаемое устройство выгодно отличается от известного тем, что позволяет обрабатывать аналоговые и дискретные сигналы, безопасно и надежно в эксплуатации, устанавливается в непосредственной близости от исполнительных механизмов. Логический модуль, содержащий два канала, кажлый из которых содержит первый элемент ЗАПРЕТ, блок памяти и реле времени, причем информационный вход первого элемента ЗАПРЕТ первого какала соединен с запрешакццим входом первого элемента ЗАПРЕТ второго канала и является первым входом модуля, от.гичаюигийея тем, что, с целью расширения области применения за счет возможности обработки как аналоговых так и дискретных сигналов, он содержит элемент ИЛИ и кроме того в каждом канале второй и третий элементы ЗАПРЕТ и элемент НЕ, причем в каждом канале выход первого элемента ЗАПРЕТ соединен с запрещающим входом второго элемента ЗАПРЕТ, выход которого соелицен с первым входом блока памяти, выход которого подключен через реле времени к загрещакицему входу третьего элемента ЗАПРЕТ. выход третьего элемента ЗА 11 РЕТ второго канала соединен со вторым входом блока памяти первого канала и со вторым запрещающим входом третьего элемента ЗАГ 1 РЕТ гервого канала, выход которого подключен к первому входу элемента ИЛИ, второй вход которого является вторым входом модуля, а выход является первым выходом устройства, выход блока памяти первого канала соединен с информационным входом первого элемента ЗАПРЕТ второго канала и через элемент НЕ первого канала со вторым входом блока памяти второго канала, выход которого через элемент НЕ второ. го канала соединен со вторым выходом модуля, причем запрегцаюгций вход первого элемента ЗАПРЕТ первого канала и выход второго элемента ЗАПРЕТ первого канала являются соответственно третьим входом и третьим выходом модуля, а второй запрещающий вход второго элемента запрета первого канала является четвертым входом моИсточники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР275524, кл. Сг 06 Г 700, 1969.2. Патент США3682131, кл. 118 - .2,1972 (прототип).813409 Риг фГ Сост Техре Тираж И Государстве делам изобрет осква, Ж - 35 Патент, г.Редактор И. КаЗаказ 285/61 абинец ВНИИП по 113035, М Филиал ПППавитель Е. Пупыревд А, Бойкас Корректор Н745 Подписноенного комитета СССРений и открытийРаушская наб., д. 4/5Ужгород, ул. Проектная, 4

СмотретьЗаявка

2623228, 24.04.1978

ПРОЕКТНЫЙ ИНСТИТУТ ХОТЬКОВСКОГОНАУЧНО-ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ"ЛАКОКРАСПОКРЫТИЕ"

ФИРСОВ СЕРГЕЙ КОНСТАНТИНОВИЧ, ШАБЕЛЬСКИЙ ВЛАДИМИР АНДРЕЕВИЧ, ГОЛЬБРАЙХ ВЛАДИМИР ЗАХАРОВИЧ, БОРИСЕНКО СТЕПАН ИЛЛАРИОНОВИЧ, МАКАРОВСКИЙ АНАТОЛИЙ ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: логический, модуль

Опубликовано: 15.03.1981

Код ссылки

<a href="https://patents.su/3-813409-logicheskijj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Логический модуль</a>

Предыдущий патент: Преобразователь кодов из системыостаточных классов b двоичныйпозиционный код

Следующий патент: Универсальный логический модуль

Случайный патент: Способ обогащения угольной мелочи