Устройство для вычисления логарифмических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 771672

Авторы: Толокновский, Штейнберг

Текст

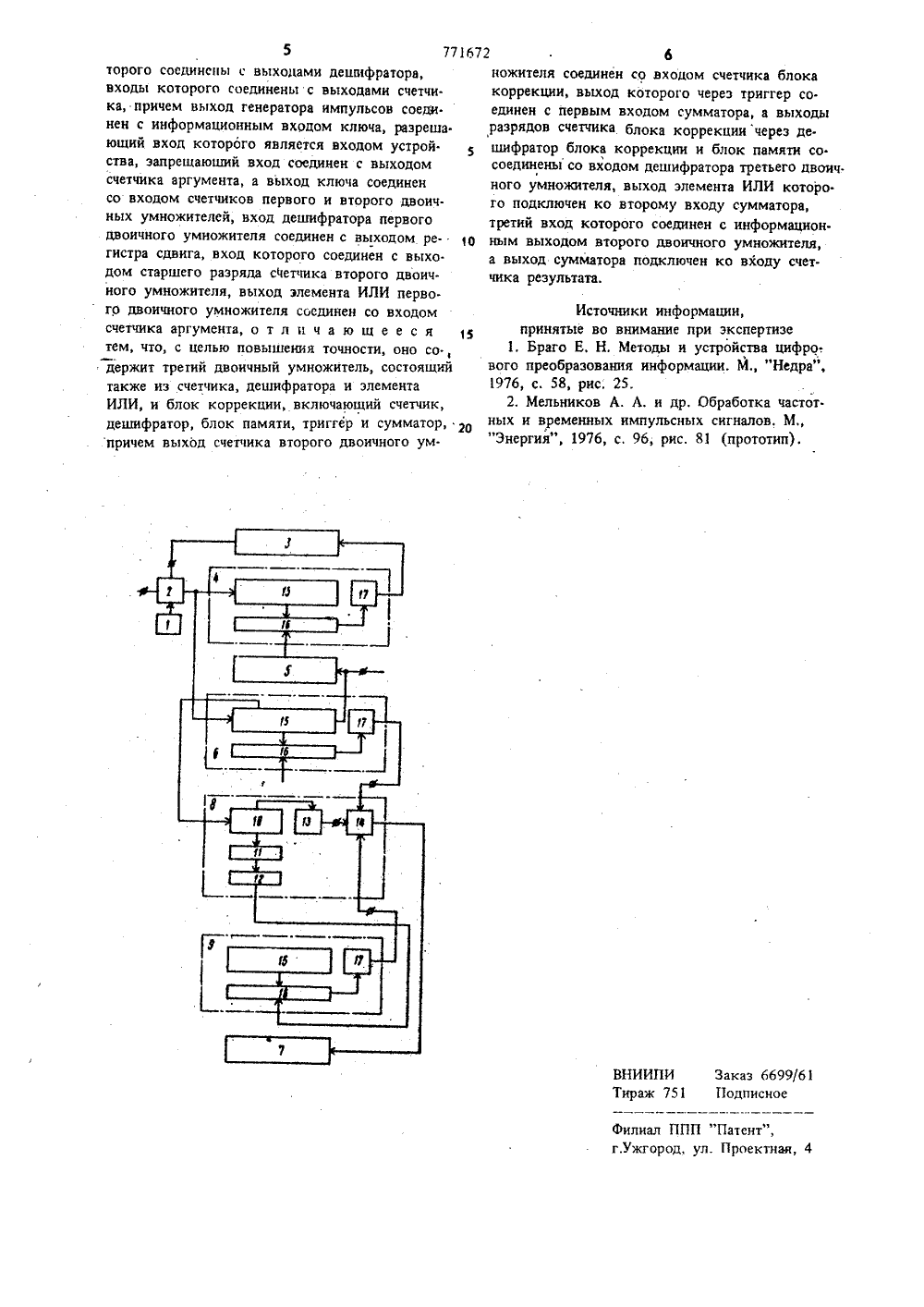

ОПИСАНИЕ ИЗОБРЕТЕН Ия Союз СоеетскмхСоцмалмстмческмхРеслублмк 11 771672 К А 8 ТОРСКОМУ С 8 КДЕТЕЛЬСТ 8 У(28) Приоритет но делам изобретений и открытий(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМИЧЕСКИХ ФУНКЦИЙ Изобретение относится к вычислительной технике, а именно к устройствам для воспроизве. дения и вычисления логарифмических функций методом кусочно-линейной аппроксимации.Известны устройства для функционального преобразования информационных сигналов в ви.5 де унитарных кодов 11,.содержащие управляемый делитель, счетчик участков, блок памяти и схему его управления. Такие устройства хотя и обеспечивают кусочно-линейную аппрокси.1 О мацию с фиксированным шагом по выходной переменной, однако имеют существенный недо статок - табличное задание функции, что при повышенных требованиях к точности приводит к увеличению приборных затрат и снижению надежности.15Наиболее близким по технической сущности к предложенному является устройство для воспроизведения логарифмических функций - . аппроксимирующей функции 21, содержащее ге 20 нератор импульсов, ключ, счетчик аргумента, счетчик результата, регистр сдвига, первый и второй двоичные умножители, каждый из ко. торых состоит из счетчика, дешифратора и эле мента ИЛИ, входы которого соединены с выхо. дами дешифратора, входы которого соединены с выходами счетчика, причем выход генератора импульсов соединен с информационным входом ключа, разрешающий вход которого является входом устройства, запрещающий вход соединен с выходом счетчика аргумента, а выход ключа соединен со входами счетчиков первого и второго двоичных умножителей.Вход дешифратора первого двоичного умно. жителя соединен с выходом регистра сдвига, вход которого соединен с выходом старшего разряда счетчика второго двоичного умножителя, выход элемента ИЛИ первого двоичного умно- жителя соединен со входом счетчика аргумента.Недостатком устройства является низкая точ. ность вследствие того, что аппроксимирующая функция имеет ступенчатую форму.Цель изобретения - повышение точности.Поставленная цель достигается тем, что в уст. ройство, содержащее генератор импульсов, ключ, счетчик аргумента, счетчик результата, регистр сдвига, первый и второй двоичные умножители, каждый из которых состоит из счетчика, дешиф.7716ратора и элемента ИЛИ, вхбды которого соеди.иены с выходами дешифратора, входы которогосоединены с выходами счетчика, причем выходгенератора импульсов соединен с информационным входом ключа, разрешающий вход которо.го является входом устройства, запрещающийвход соединен с выходом счетчика аргумента,а выход ключа соединен со входами счетчиковпервого и второго двоичных умножителей, входдешифратора первого двоичного умножителя 10соединен о выходом регистра сдвига, вход которого соединен с выходом старшего разрядасчетчика второго двоичного умножителя, выходэлемента ИЛИ первого двоичного умножителясоединен со входом счетчика аргумента, допол. 15нительно ввеДены третий двоичный умножитель,состоящий также из счетчика, дешифратора иэлемента ИЛИ, и блок коррекции, включающийсчетчик, дешифратор, блок памяти, триггер исумматор. При этом выход счетчика второго 20двоичного умножителя соединен со входомсчетчика блока коррекции, выход которого через триггер соединен с первым входом сумматора. Выходы разрядов счетчика блока коррек.ции через дешифратор блока коррекции и блок 25памяти соединены со входом дешифратора треть 6его двоичного умножителя, выход элемента ИЛИкоторого подключен ко второму входу сумматора, третий вход сумматора, соединен с инфор.мационным выходом второго двоичного умножителя, а выход сумматора, подключен ко вхо.ду счетчика результата.Структурная схема предложенного устройства приведена .на чертеже.Устройство содержит генератор 1 импульсов;ключ 2; счетчик 3 аргумента; первый двоичный умножитель 4; регистр 5 сдвига; второйдвоичный умножитель б; счетчик 7 результата;блок 8 коррекции; третий двоичный умножи.тель 9 Блок 8 коррекции включает в себясчетчик 10, дешифратор 11, блок 12 памяти,триггер 13 и сумматор 14 (импульсов). Двоичные .умножители состоят из счетчика 15, дешифратора 16, элемента ИЛИ 17,Предложенное устройство работает следующим 45образом.Коэффициент пересчета счетчика 3 аргументаустанавливается равным заданному значению аргумента, в регистр 5 сдвига записывается единица, а триггер 13 устанавливается в состояние,при котором сумматор 14 импульсов фиксиру.ется в режиме сложения. На управляющих вхо.дах двоичного умножителя 9 устанавливаетсяткод первого углового коэффициента корректи.рующей функцииПри подаче сигнала пуска на ключ 2 он от.пирается и счетные импульсы с выхода генера.тора 1 поступают на вход двоичных умножите.лей 4, 6 и 9, Устройство обрабатывает аппроксимирующую функцию на первомучастке. Приотработке каждого участка коррекции на входсчетчика 10 поступает по одному импульсу, чтоприводит к переключению кодов угловых коэф.фициентов на управляющих входах двоичногоумножителя 9, При отработке первой половиныпервого участка аппроксимации и, соответствен.но, первой половины участков коррекции кор.ректирующие импульсы, поступающие на входсумматора 14 импульсов, суммируются с импуль.сами приращения, Скорректированное приращение функции интегрируется в счетчике 7 резуль.татаВ момент окончания отработки первой по.ловины участков коррекции, что соответствуетпрохождению точки максимальной погрешности,на вход триггера 13 со счетчика 10 поступаетимпульс, в результате чего триггер 13 перебрасывается и устанавливает сумматор 14 импульсов в режим вычитания. В момент окончанияотработки первого участка аппроксимации и,соответственно, второй половины участков коррекции счетчик 10 и триггер 13 приходят в исходное состояние, на вход регистра 5 сдвигапоступает единица, и устройство осуществляетотработку второго участка аппроксимации.Для выполнения условия аппроксимацииЬу =.1 п 2 на управляющих входах двоичногоумножителя 6 устанавливается код числа М == 1 п 2 = 0,693 с точностью до определения знака после запятой, благодаря чему при переполнении .на выход двоичного умножителя б посту.пает число импульсов, равноеЬу = Ь 2 = 693,а на вход регистра сдвига - единица, что означает окончание отработки очередного участкааппроксимации с шагом Ьу = п 2 и обеспечи.вает требуемое изменение углового коэффициен.та вдвое на каждом последующем участке. Можно видеть, что при поступлении на вход счетчика 7 результата очередного числа импульсовЬу число импульсов, поступающее на вход счетчика 3 аргумента, увеличивается вдвое.Сравнение предложенного и известйЬго устройств показывает, что предложенное отличается повышенной (до заданной величины) точностью вычисления, что улучшает эксплуатационные характеристики и позволяет использоватьвего при обработке информационных сигналовс точностью до сотых долей процента.Формула изобретенияУстройство для вычисления логарифмическихфункций, содержащее генератор импульсов,ключ, счетчик аргумента, счетчик результата,регистр сдвига, первый и второй двоичные умножители, каждыи из которых состоит из счет.чика, дешифратора и элемента ИЛИ, входыко.77167 Заказ 6699/61Подписное ВНИИПИТираж 751 Патент Филиал ПП г.ужгород,роектны 5торого соединены с выходами дешифратора, входы которого соединены с выходами счетчика, причем выход генератора импульсов соедй. нен с информационным входом ключа, раэреша. ющий вход которого является входом устрой. ства, запрещающий вход соединен с выходом счетчика аргумента, а выход ключа соединен со входом счетчиков первого и второго двоичных умножителей, вход дешифратора первого двоичного умножителя соединен с выходом регистра сдвига, вход которого соединен с выходом старшего разряда сМетчика второго двоич. ного умножителя, выход элемента ИЛИ перво. го двоичного умножителя соединен со входом счетчика аргумента, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, оно со., держит третий двоичный умножитель, состоящий также из счетчика, дешифратора и элемента ИЛИ, и блок коррекции, включающий счетчик, дешифратор, блок памяти, триггер и сумматор, .причем выход счетчика второго двоичного ум 2 6ножителя соединен со входом счетчика блока коррекции, выход которого через триггер со. единен с первым входом сумматора, а выходы разрядов счетчика блока коррекции через де. шифратор блока коррекции и блок памяти со. соединены со входом дешифратора третьего двонч. ного умножителя, выход элемента ИЛИ которо. го подключен ко второму входу сумматора, третий вход которого соединен с информационным выходом второго двоичного умножителя, а выход сумматора подключен ко входу счет. чика результата. Источники информации,принятые во внимание при экспертизе1. Браго Е, Н. Методы и устройства цифро вого преобразования информации, М., "Недра, 1976, с. 58, рис. 25.2, Мельников А. А. и др. Обработка частот. ных и временных импульсных сигналов. М., "Энергия", 1976, с. 96, рис, 81 (прототип).

СмотретьЗаявка

2709186, 26.12.1978

ПРЕДПРИЯТИЕ ПЯ Р-6378

ТОЛОКНОВСКИЙ ВЯЧЕСЛАВ РОДИОНОВИЧ, ШТЕЙНБЕРГ ВАЛЕРИЙ ЭМАНУИЛОВИЧ

МПК / Метки

МПК: G06F 17/10

Метки: вычисления, логарифмических, функций

Опубликовано: 15.10.1980

Код ссылки

<a href="https://patents.su/3-771672-ustrojjstvo-dlya-vychisleniya-logarifmicheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления логарифмических функций</a>

Предыдущий патент: Цифровое устройство для воспроизведения кусочно-линейных функций

Следующий патент: Устройство для классификации сигналов

Случайный патент: Устройство для синхронизации импульсов