Цифровой интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

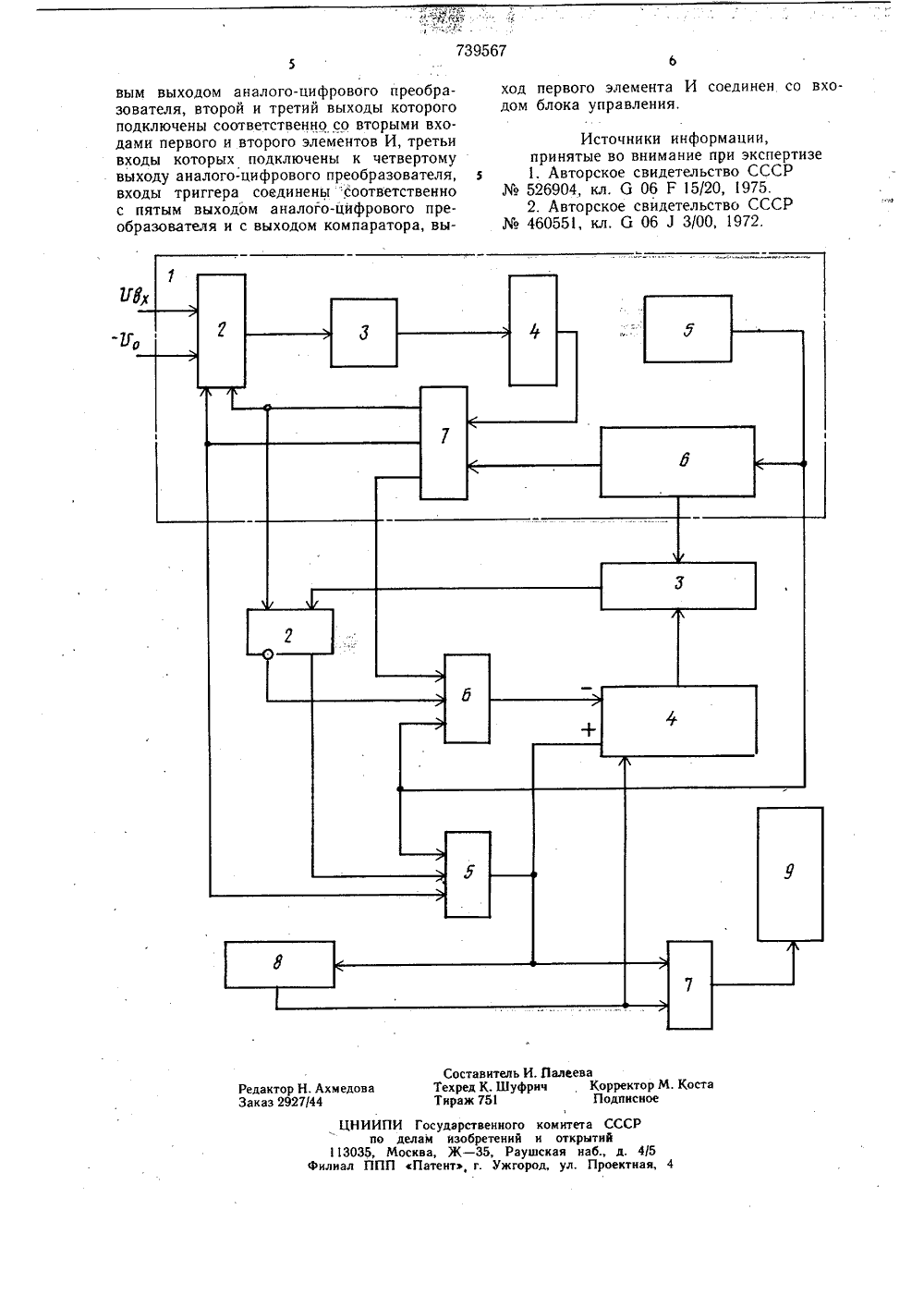

ОП ИСАН щ 739567 Союз СоветскихСоциалистическихРеспублик ИДЕТ ЕЛЬСТВУ ТОРСКО 61) Дополнительное к авт. свид-ву -22) Заявлено 13.02.78 (21) 2578991/18-2(23) Приори убликовано 05,06.80. Бюллетеньа опубликования описания 15.06.80 53) УДК 681.14 (088.8) делам изобретеии и открытий. Гуревич, Л, А. Русинов, В. Н. Соколов, Н. А. Сягаев и В. Н. Чернышев 2) Авторы изобретения инградский ордена Трудового Красного Знамени технологически институт им. Ленсовета(54) ЦИФРОВОЙ ИНТЕГРАТОР иводит к тки сигточносИзобретение относится к вычислительнойтехнике и предназначено для автоматизации процесса обработки хроматографической информации.Известны устройства, содержащие аналого-цифровой преобразователь, блок управления, регистр базисного сигнала и счетчик интеграла 1),Недостатками известных устройств является то, что используемые в них цифровые следящие системы коррекции базисногосигнала либо сложны, либо их работа принципиально возможна только в сочетании сразвертывающим преобразователем, отличающимся низкой помехоустойчивостью,Наиболее близким по технической сущности к данному изобретению является цифровой интегратор, содержащий аналого-цифровой преобразователь, выполненный в видеразвертывающего преобразователя, блокуправления, счетчик интеграла и цифровойследящий корректор базисного сигнала 2.Недостатком известного интегратора является то, что в нем следящий корректорбазисного сигнала может работать толькос аналого-цифровым преобразователем развертывающего типа, низкая помехоустойчиость преобразования которого п онижению общей точности обра алов в промышленных условияхЦель изобретения - повышен Поставленная цель достигается тем, что в цифровой интегратор, содержащий аналого-цифровой преобразователь, счетчик интеграла, блок управления, регистр, триггер, первый и второй элементы И, первые входы которых соединены соответственно с первым и вторым выходами триггера, выходы первого и второго элементов И соединены соответственно с первым и вторым входами регистра, блок управления, выход которого соединен с третьим входом регистра и с первым входом третьего элемента И, выход которого подключен ко входу счетчика интеграла, второй вход третьего элемента И соединен с выходом первого элемента И, аналого-цифровой преобразователь выполнен интегрирующим, и в интегратор введен компаратор, причем первый вход компаратора соединен с выходом регистра, второй вход компаратора - с первым выходом аналого-цифрового преобразователя, второй и третий выходы которого подключены7395671 20 25 формула изобретения о 45-соответственно со вторыми входами первогои второго элементов И, третьи входы которых подключены к четвертому выходу аналого-цифрового преобразователя; входы триггера соединены соответственно с пятым выходом аналого-цифрового преобразователя и с выходом компаратора, выход первого элемента И соединен со входом блока уп. равления.На чертеже представлена блок-схема интегратора, который содержит интегрирующий аналого-цифровой преобразователь 1, триггер 2, компаратор 3, регистр 4, элементы И 5 - 7, блок 8 управления, счетчик 9 интеграла,Цифровой интегратор работает следую.-щим образом. Напряжение с выхода хроматографа )вы поступает на преобразователь 1, Цикл преобразования аналоговой величины;, = .;-,в цифровую делится на три подтакта, причем - время первого подтакта представляет собой.-=. -половину цикла преобразования и равно сум,.:ме второго и третьего подтакта,Числовой эквивалент аналогового сигнала 11 вх поступает на регистр 4 через управляемую компаратором 3 следящую систему (триггер 2, элемент И 5 или элемент И 6), Компаратор 3 сравнивает код базисного значения 116 с сИгнала хроматографа, хранящийся в регистре 4, с текущим значением кода счетчика 9 и при равенстве этих кодов выдает сигнал на второй вход триггера 2, переводя последний в единичное состояние, Обратно в нулевое состояние триг- ЗО гер 2 возвращается сигналом с выхода узлауправления преобразователя 1 в начале каждого нового цикла преобразования. В первый цикл преобразования значение кода Убс в регистре 4 равно нулю (т. е. 1.1 в, больше 116), и в начале второго подтакта этого цикла импульс с выхода компаратора 3 поступает на триггер 2, который открывает первый элемент И 5, разрешенный сигналом с выхода узла управления преобразователя 1. Тактовые импульсы с генератора преобразователя 1 поступают через элемент И 5 на шину сложения регистра 4 базисного сигнала, выполненного реверсивным. Младшие разряды регистра 4 являются буферными, а код базисного сигнала 1.16 с снимается со старших разрядов. Поэтому к началу второго цикла преобразования в регистре 4 будет записан код только части 3 с. Сигнал с выхода компартора 3 придет позже, чем в первом цикле, число импульсов, поступивших в регистр 4 уменьшится и будет уменьшаться за счет того, что из текущего значения 1.1 в будет вычитаться все увеличивающееся промежуточное значение 116, из регистра 4, Отслеживание базисного сигнала кончается, когда 11 б, в регистре 4 будет равным 11 р . При этом сигнал на выходе коммутатора 3 появляется в момент окончания второго подтакта. Поступление импульсов в регистр 4 по шине сложения прекращается и возобновится только тогда, когда 11 щ, станет больше 116 из регистра 4.При уменьшении входного сигнала 1 вх меньше Уб)во время второго подтакта сигнал с компаратора 3 не поступает, и триггер 2 остается в нулевом состоянии, подаваяразрешение на элемент И 6. В момент начала третьего подтакта сигнал с выхода узла управления преобразователя 1 открывает элемент И 6. Импульсы с генератора преобразователя 1 поступают по шине вычитания в регистр 4, уменьшая его содержимое, пока сигнал с компаратора 3 не установит триггер 2 в единичное состояние и запретит элемент И 6. Поступление импульсов по шине вычитаниг в регистр 4 замедляется в последующие циклы преобразования и прекращается при 1 Хщ, равном 1.16 из регистра 4.Слежение за базисным сигналом хроматографа осуществляется при отсутствии полезного сигнала (пика), что определяется блоком 8 управления. При обнаружейии пика начинается коррекция входного сигнала на базисный и интегрирование. Блок 8 запрещает поступление импульсов в регистр 4, где запоминается накопленное значение 1.)бс. Одновременно блок 8 открывает элемент И 7,через который с выхода элемента И 5 в счетчик 9 начинают поступать импульсы, представляющие собой числовой эквивалент разности 13-06. Введение компаратора, т. е. создание новаго цифрового следящего корректора базисного сигнала, могущего работать с аналого-цифровым преобразователем интегрирующего типа, выгодно отличает данный цифровой интегратор от прототипа, так как при повышении точности коррекции базисного сигнала происходит значительное уменьшение погрешности аналого-цифрового преобразования от действия шума и помех. Цифровой интегратор, содержащий аналого-цифровой преобразователь, счетчик интеграла, блок управления, регистр, триггер,первый и второй элементы И, первые входы которых соединены соответственно с первым и вторым выходами триггера, выходы первого и второго элементов И соединены соответственно с первым и вторым входами регистра, блок управления, выход которого соединен с третьим входом регистра и с первым входом третьего элемента И, выход которого подключен ко входу счетчика интеграла, второй вход третьего элемента И соединен с выходом первого элемента И, отличающийся тем, что, с целью повышения точности, аналого-цифровой преобразователь выполнен интегрирующим, в интегратор введен комп аратор, причем первый вход компаратора соединен с выходом регистра, второй вход компаратора - с пер739567 Составитель ИТехред К. ШуфрТираж 751 алеева Корректор М Коста Подписное едактор Н. Ахмедоваказ 2927/44 митета СССРоткрытийая наб., д. 4/5ул. Проектная, 4 ЦНИИП по 113035,нлиал ППИ Государственного к делам изобретений и осква, Ж - 35, РаушсПатент, г. Ужгород вым выходом аналого-цифрового преобразователя, второй и третий выходы которого подключены соответственно со вторыми входами первого и второго элементов И, третьи входы которых подключены к четвертому выходу аналого-цифрового преобразователя, входы триггера соединены соответственно с пятым выходом аналого-цифрового преобразователя и с выходом компаратора, выход первого элемента И соединен со входом блока управления. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР526904, кл. б 06 Г 15/20, 1975.2. Авторское свидетельство СССР460551, кл. 6 06 1 3/00, 1972.

СмотретьЗаявка

2578991, 13.02.1978

ЛЕНИНГРАДСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ТЕХНОЛОГИЧЕСКИЙ ИНСТИТУТ ИМ. ЛЕНСОВЕТА

ГУРЕВИЧ АЛЕКСАНДР ЛЬВОВИЧ, РУСИНОВ ЛЕОН АБРАМОВИЧ, СОКОЛОВ ВАЛЕРИЙ НИКОЛАЕВИЧ, СЯГАЕВ НИКОЛАЙ АНДРЕЕВИЧ, ЧЕРНЫШЕВ ВИКТОР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06J 1/02

Метки: интегратор, цифровой

Опубликовано: 05.06.1980

Код ссылки

<a href="https://patents.su/3-739567-cifrovojj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой интегратор</a>

Предыдущий патент: Цифровой интегратор

Следующий патент: Устройство для аппроксимации функций

Случайный патент: Способ получения невыпрямляющего контактного покрытия на кремнии