Программно-логический регулятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

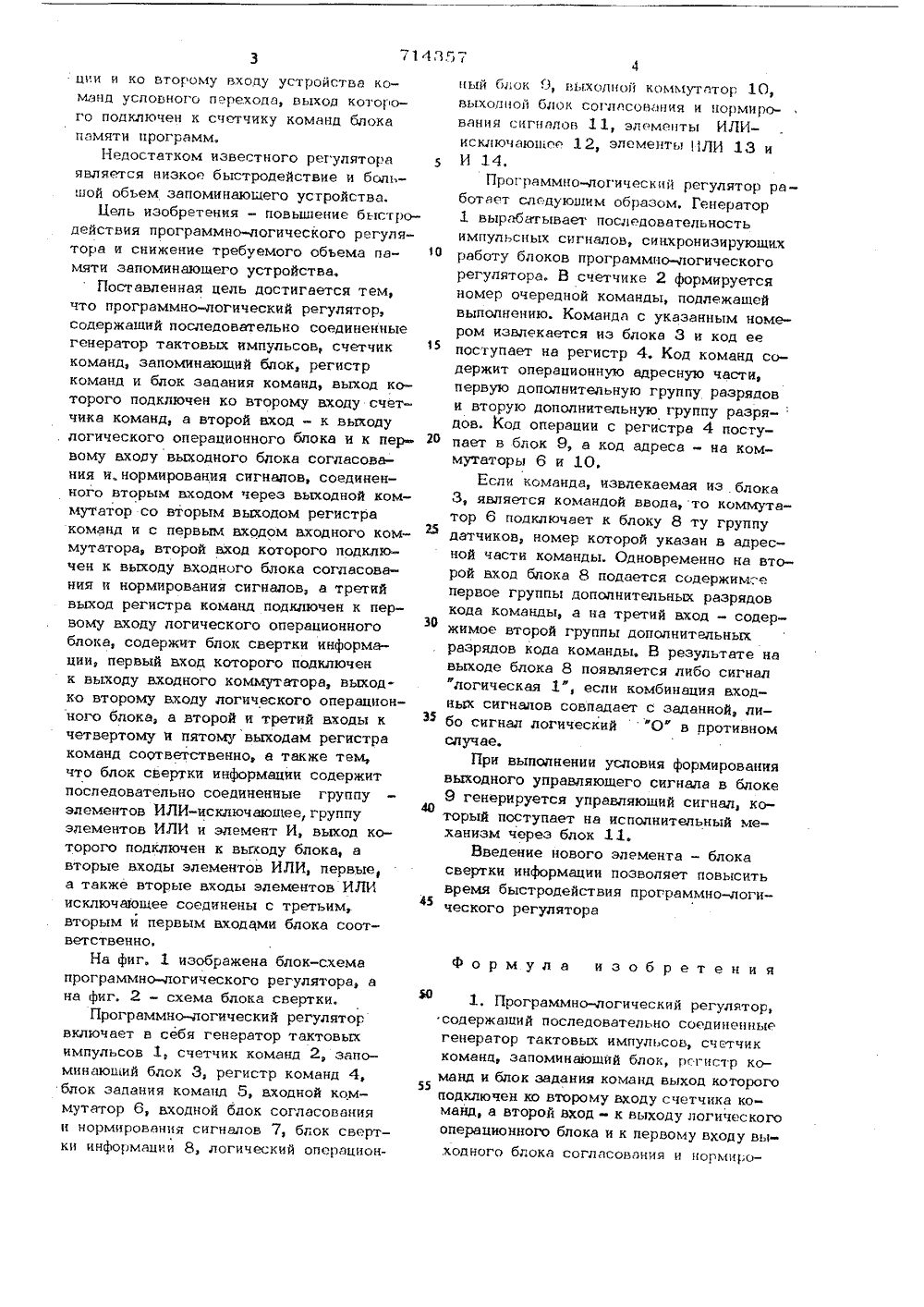

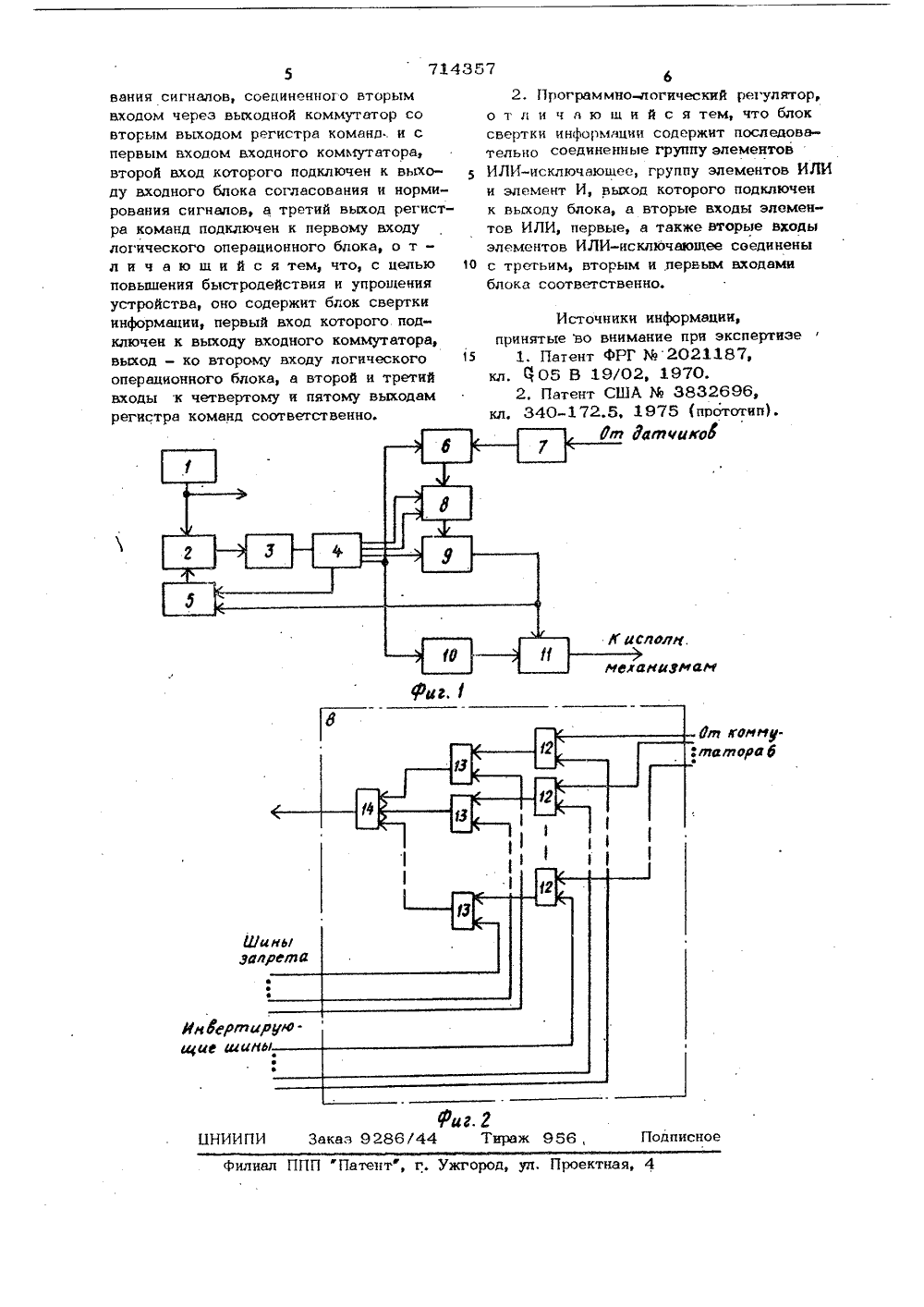

Союз Советски кСоциалистическихРеспублик П САНИИ ЗОВРЕТЕН ИЯ ВТОРСКОМУ СВИДЕ 7 ЕПЬСТВУ(22) Заявлено 01,04. 77 (21) 2468632/18-24с присоединением заявки М Кл,2 5 В 19/18 5 В 23/02 Ввударетмец 3 иавтвт ь.ь.ФР ее дащн имбретвнвк н фткрвив(23) П риорите бликовано 05.02,80. Бюллетень М а опубликования описания 10.02.8 621,388. 8) Н. М. Голубев, В, А. Сечкин., В, С. Чидсон,и И. Яковлев 72) Авторы изобретения 71) Заявитель И-ЛОГИЧЕСКИЙ РЕГУЛЯТО Изобретение относится к автоматическим системам регулирования и управления работой оборудования,Известен программно-логический регулятор, воспринимающий информацию от5двухпозиционных датчиков и формирующийна основе анализа этой информации управляющие сигналы для исполнительных механизмов 1. В состав регулятора в качестве основных блоков входят: блок памяти программ, блок ввода информациии блок вывода управляющих сигналов,Блоки ввода и вывода содержат устройства преобразования и коммутации сигналов.Наиболее близким по технической сущности к предложенному изобретению являетса программно-логический регулятор,который содержит генератор тактовыхимпульсов, блок памяти программ, состоящий из счетчика команд, запоминающегоблока, регистра команд и блока командусловного перехода, логический операционный блок, а также блоки ввода н вывода информации, состоящие каждый из входного (выходного) коммутатора и блоков согласования и нормирования входных и выходных сигналов соответственно 1 2, Генератор тактовых импульсовподключен к синхронизируюшим входамсчетчика команд и других блоков, входящих в устройство. Счетчик команд подключен к запоминающему устройству, выход которого подключен к регистру команд. Регистр команд в свою очередьподключен к входному коммутатору, выходному коммутатору, логическому операционному блоку и к червому входу уст-.ройства команд условного перехода,. Входной коммутатор по входу соединен с устройством согласования инормированияблока ввода информации, а по выходу слогическим операционным блоком. Выходной коммутатор соединен с устройствомсогласования и нормирования блока вывода информации. Выход логического операционного блока подключен к информационному входу устройства. согласования и нормирования блока вывода информации и ко второму входу устройства команд условного перехода, выход которого подключен к счетчику команд блокапамяти программ.Недостатком известного регулятораявляется низкое быстродействие и большой объем запоминающего устройства,Бель изобретения - повышение быстродействия программно-логического регулятора и снижение требуемого объема памяти запоминающего устройства,Поставленная цель достигается тем,что программно-логический регулятор,содержащий последовательно соединенныегенератор тактовых импульсов, счетчиккоманд, запоминающий блок, регистркоманд и блок звцания команд, выход которого подключен ко второму ьходу счетчика команд, а второй вход - к выходу. логического операционного блока и к первому ьходу выходного блока согласования и, нормирования сигналов, соединенного вторым ьходом через выходной коммутатор со вторым выходом регистракоманд и с первым ьходом входного коммутатора, второй ьход которого подключен к выходу входного блока согласования и нормирования сигналов, а третийвыход регистра команд подключен к первому входу логического операционногоблока, содержит блок свертки информации, первый ьход которого подключенк выходу входного коммутатора, выходко второму входу логического операционного блока, а второй и третий ьходы кчетвертому и пятому выходам регистракоманд соответственно, а также тем,что блок свертки информации содержитпоследовательно соединенные группуэлементов ИЛИ-исключающее, группуэлементов ИЛИ и элемент И, выход которого подключен к выходу блока, авторые ьходы элементов ИЛИ, первые,а также вторые входы элементов ИЛИисключающее соединены с третьим,вторым и первым входами блока соответственно.На фиг. 1 изображена блок-схемвпрограммно-логического регулятора, ана фиг. 2 - схема блока свертки.Программно-логический регуляторвключает в себя генератор тактовыхимпульсов 1, счетчик команд 2, запоминающий блок 3, регистр команд 4,блок задания команд 5, входной коммутатор 6, ьходной блок согласованияи нормирования сигналов 7, блок свертки информации 8, логический операционный блок О, выходной коммутатор 10,выходной блок согласования и нормирования сигналов 1 1 элементы ИЛИисключаюшо 12, элементь, ИЛИ 13 и5Программно-погический регулятор работает следующим образом, Генератор1 вырабатывает последовательностьимпульсных сигналов, сиьхроиизирующих1 О работу блоков программно логическогорегулятора. В счетчике 2 формируетсяномер очередной команды, подлежащейвыполнению. Команда с укаэанным номером извлекается из блока 3 и код ее15поступает нв регистр 4. Код команд содержит операционную адресную части,первую дополнительную группу разрядови вторую дополнительную группу разря-дов. Код операции с регистра 4 посту 20 пает в блок 9, а код адреса - на коммутаторы 6 и 10,Если команда, извлекаемая иэ блока3, является командой ввода, то коммутв 25тор 6 подключает к блоку 8 ту группудатчиков, номер которой указан в адресной части команды. Одновременно на второй вход блока 8 подается содержимоепервое группы дополнительных разрядов30кода команды, а на третий ьход - содержимое второй группы дополнительныхразрядов кода команды, В результате навыходе блока 8 появляется либо сигнал"логическая 1", если комбинация ьходных сигналов совпадает с заданной, ли 35бо сигнал логическийО в противномслучае.При выполнении условия формированиявыходного управляющего сигнала в блоке9 генерируется управляющий сигнал, который поступает на исполнительный механизм через блок 11,Введение нового элемента - блокасвертки информации позволяет повыситьвремя быстродействия программно-логи 45ческого регулятораформула изобретения501. Программно-логический регулятор,содержащий последовательно соединенныегенератор тактовых импульсов, счетчиккоманц, запоминающий блок регистр комвнд и блок задания команд выход которогоподключен ко второму входу счетчика команд, а второй вход - к выходу логическогооперационного блока и к первому входу вы.ходного блока согласования и иормиро714357 ОЛЛ Олт вьчиуталтора 4 Фиг. ГЦНИИ ПИ Заказ 9286/44 Тира 6 одписно Проектная, 4 ванин сигналов, соединенното вторымвходом через выходной коммутатор совторым выходом регистра команд и спервым входом входного коммутатора,второй вход которого подключен к выходу ВхОднОГО блока согласования и нормирования сигнелов, а третий выход регистра команд подключен к первому входулогического операционного блока, о т -л и ч а ю ш и й с я тем, что, с цельюповышения быстродействия и упрощенияустройства, оно содержит блок сверткиинформации, первый вход которого подключен к выходу входного коммутатора,выход - ко второму входу логическогооперационного блока, а второй и третийвходы к четвертому и пятому выходамрегистра команд соответственно. илиад ППП "Патент", г. У 62. Программно-логический регулятор,отли чаюшийсятем,чтоблоксвертки информации содержит последовательно соединенные группу элементовИЛИ-исключающее, группу элементов ИЛИи элемент И, выход которого подключенк выходу блока, а вторые входы элементов ИЛИ, первые, а также вторые входыэлементов ИЛИ-исключающее соединены 10 с третьим, вторым и первым входамиблока соответственно. Источники информации,принятые во внимание при экспертизе 15 1. Патент фРГ М 2021187, кл, 405 В 19/02, 1970.2. Патент США % 3832696, кл. 340-172.5, 1975 (прототип).Р Ратчико 8

СмотретьЗаявка

2468632, 01.04.1977

ПРЕДПРИЯТИЕ ПЯ В-8208

ГОЛУБЕВ НИКОЛАЙ МИХАЙЛОВИЧ, СЕЧКИН ВИТАЛИЙ СЕРГЕЕВИЧ, ЧИДСОН ВАЛЕРИЙ СЕРГЕЕВИЧ, ЯКОВЛЕВ ИГОРЬ ВИКТОРОВИЧ

МПК / Метки

МПК: G05B 19/045, G05B 19/406, G05B 23/02

Метки: программно-логический, регулятор

Опубликовано: 05.02.1980

Код ссылки

<a href="https://patents.su/3-714357-programmno-logicheskijj-regulyator.html" target="_blank" rel="follow" title="База патентов СССР">Программно-логический регулятор</a>

Предыдущий патент: Круговой интерполятор

Следующий патент: Следящая система программного управления станком

Случайный патент: Способ отбора фотопериодически нейтральных форм ячменя