Устройство для возведения в квадрат п-разрядных двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

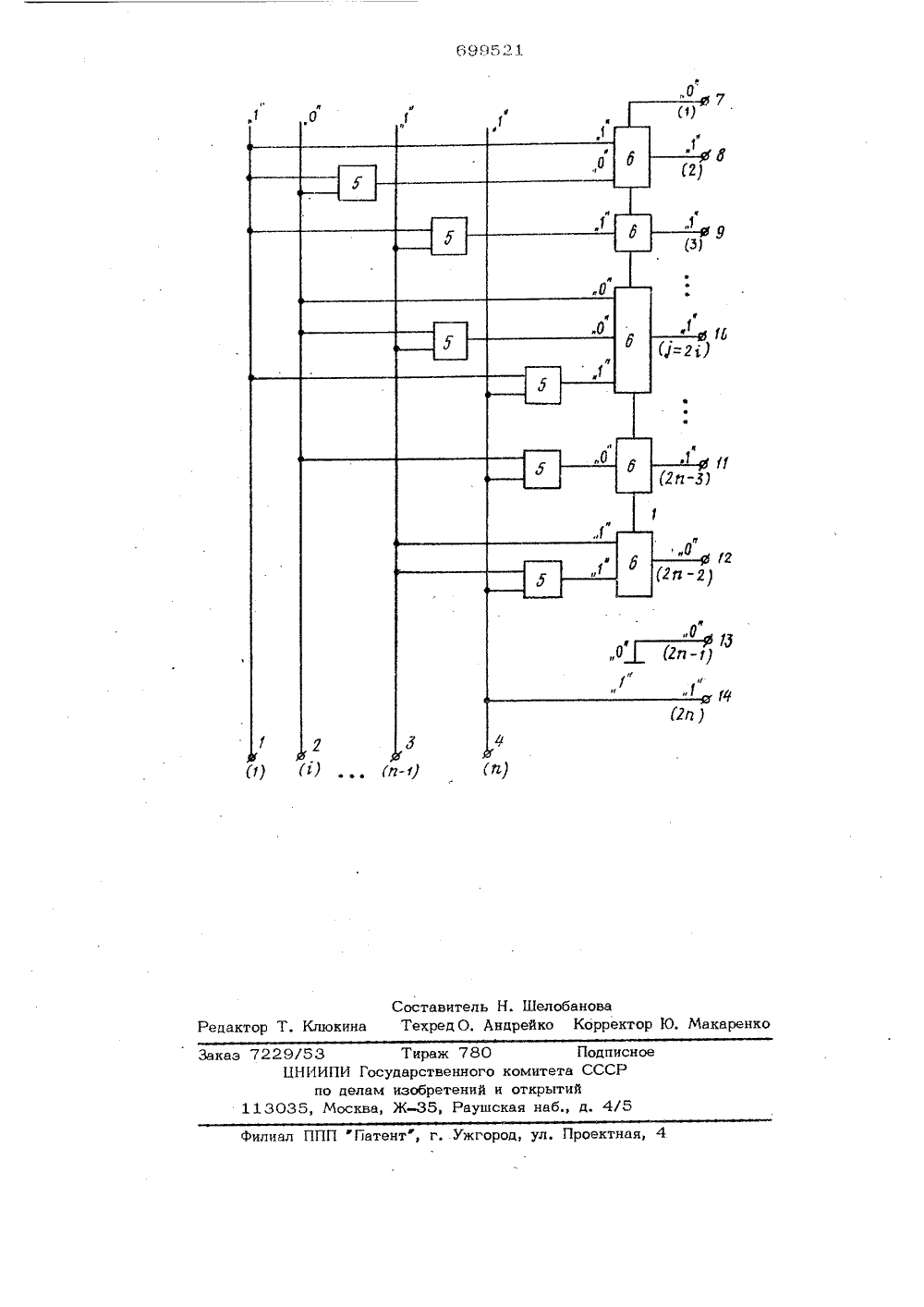

(22) Заявлено 3 3.7 6629/18 аявпи Ж рисоединение Гваудвратввнны ваивтв СССР па делам нзабрвтвнкй и аткрытнй23) Приоритет Опубликов Бюллетень РВ 43 3) УДК 681,325) Авторыизобретения титут электродинамики АН Украинской СС аявитель СТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРИ -РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ вычислительной технике, предназначено для возведения в квадрат Я -разрядныхдвоичных чисел и может быть использовано в информационно-измерительных системах в качестве решающего блока )для оперативной обработки информации,Известны устройства, позволяющие получать на их выходах значение кода, равное квадрату входной величины, представляющих собой совокупность логических схем, количество и связи между которыми определяют аппаратурные затраты и быстродействие всей схемы в целом )11.Из известных устройств наиболее близким к изобретению по своей технической сущности является устройство длявозведения в квадрат )т - разрядных двоичных чисел, содержащее одноразрядныесумматоры, последовательно соединенныемежразрядными связями переноса, входыкоторых соединены с выходами элементов И, а выходы - с 1 -ыми ,(3 а 1 зобретение относится к цифровой Волошин, В. ф. Евдокимовесяц и Ю. А, Плющ 2 и) выходами устройства, (2)-1)-ый и 2 тт-ый выходы устройства подключены соответственно к шине информационного нуля и к т 1-ому входу устройства 21.Недостатком данного устройства являются большие аппаратурные затраты.Цель изобретения - упрощение устройства.Это достигается тем, что в устройстве для возведения в квадрат т -разрядных двоичных чисел, содержащем одноразряд ные сумматоры, последовательно соединенные межразрядными связями переноса, входы которых соединены с выходами элементов И, а выходы - с -ыми (=1 2 т 1-2) выходами устройства, (2 М)-ый и 2 т-ый выходы устройства подключены соответственно к шине информационного нуля и к тьому входу устройства, т-ый вход ( 1 1тт ) устройства соединен непосредственно с входом одноразрядного сумматора, выход суммы которого соединен с=21 выходом устройства, 3 -ый вход устройства (с д 2,3, 1) соединен с первыми входами (В-) )-ого элементов И, вторые входы которыхподключены к-ому (к=1,2 Я)входу устройства.На чертеже представлена фуКцио 1 а -ная схема предлагаемого устройства дляслучая возведения в квадрат четрехразрядных чисел (=4),Устройство содержит входы 1-4,элементы И 5, одноразрядные сумматоры 6, выходы 7-14,Устройство работает следуюиИм образом,На вход 1 поступает значение старшего разряда возводимого в квадрат числа,а значение старшего разряда результатаснимается с выхода 7. На вход 4 поступает значение младшего разряда возводимого в квадрат числа, а значение младшего разряда результата снимается с вы 20хода 14 Например, при поступлении навходы 1-4 устройства четырехразрядного кода Х=1011 на выходы 7-14 поокончанию переходных процессов в схеме25установится значение кода У-"01111001,соответствующее квадрату исходного значения входного кода Х (состояния элементов схемы (см. на чертеже).Количество элементов И при четырех 30разрядном представлении информации равно шести. При реализации известного устройства потребовалось бы девять элемен-тов И-НЕ и шесть элементов НЕ.При и -разрядном представлении инфор 35мации для реализации схемы известного.устройства необходимоИф+Иь 1 элементов И-НЕ и 2, -2 элементов НЕ. Предложенная схема устройства реализуется2с использованием ф элементов И.Ф2 Гаким образом, испоьзоиИие предло жеП 10 й схемы устройства позвол 5 ет су цОственио уменьшить апиаратурные затраты, что, в свою очередь, позволяет повысит, надежность работы и уменьшить потребляемую мощность устройства в целом,Формула изобретенияУстройство для возведения в квадратИ -разрядных двоичных чисел, содержащее одноразрядные сумматоры, последовательно соединенные межразряднымисвязями переноса, входы которых соединены с выходами элементов И, а выходыс-ми ( 1 в 1 , 2 11 -2) выходами устройства, (2 и)-ый и 2 и-ый выходыустройства подключены соответственнок шине информационного нуля и к 11-омувходу устройства, о т л и ч а ю щ е е -с я тем, что, с целью упрощения, 1-ыйвход (1 =1 ъ) устройства соединеннепосредственно с входом одноразрядного сумматора, выход суммы которогосоединен с=. 2(, выходом устройства,-ый вход устройства (3 =2,3 Ъ) соединен с первыми входами ( -1)-огоэлементов И, вторые входы которых подключены к К-ому (кщ 1,2-1) входуустройства.Источники информаций,принятые во внимание при экспертизе1, Прангишвили И, В, и др. Микроэлектроника и однородные структуры дляпостроения логических и вычислительныхустройств, . М., фНаука", 1967, с. 180.2. Авторское свидетельство СССР позаявке Мо 2475297/24 от 31.10.7759 с 50 з 7229/53 Тираж 7 ЦНИИПИ Государственн по делам изобретен 113035, Москва, Ж, Ра

СмотретьЗаявка

2596629, 30.03.1978

ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АН УКРАИНСКОЙ ССР

ВАЙНШТЕЙН ЯКОВ МОИСЕЕВИЧ, ВОЛОШИН ВИТАЛИЙ ИВАНОВИЧ, ЕВДОКИМОВ ВИКТОР ФЕДОРОВИЧ, ЗУБЕНКО ИВАН ФЕДОРОВИЧ, МЕСЯЦ ВЛАДИМИР ВАСИЛЬЕВИЧ, ПЛЮЩ ЮРИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: возведения, двоичных, квадрат, п-разрядных, чисел

Опубликовано: 25.11.1979

Код ссылки

<a href="https://patents.su/3-699521-ustrojjstvo-dlya-vozvedeniya-v-kvadrat-p-razryadnykh-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для возведения в квадрат п-разрядных двоичных чисел</a>

Предыдущий патент: Преобразователь двоичного кода в двоично-десятичный

Следующий патент: Многоканальное устройство для приоритетной селекции импульсов

Случайный патент: Способ холодного облагораживания сульфатной предгидролизной целлюлозы