Способ считывания выходного кода аналого-кодового преобразователя комбинированного уравновешивания

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 668086

Авторы: Погрибной, Рожанковский

Текст

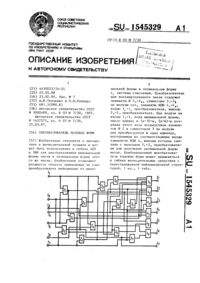

ОПИСАНИЕ ИЗОБРЕТЕН ИЯ Союз Советских Социалистических Республик(61) Дополнительное авт, свнд-ву -21) М. Кл.Н 03 К 13/О 22) Заявлено 03,08.76 1) 2398345/18. с присоединением зая Гееударатеееай наинтет СССР па делам нзебретеннй н еткрытнй(53) УДК 681.325 (088.8 та опубликова ия описания 15.06.7 72) Авторы изобретения. Погрибной и И. ожанковскии ут АН Украинской ССР 71) Заявитель зико- механический ин(54) СПОСОБ СЧИТЫВАНИЯ ВЫХОДНОГО, КОДА АНАЛОГО - КОДОВОГО ПРЕОБРАЗОВАТЕЛЯ КОМБИНИРОВАННОГО УРАВНОВЕШИВАНИ омент равенства соответствующих внения такого способа является неполие высокого быстродействия ное использо Изобретение относится к области автоматики и вычислительной техники и может быть использовано в быстродействующих системах с промежуточным аналого-кодовым преобразованием, в частности в бортовых системах.Известен способ считывания кода с выхода следящих аналого. кодовых преобразователей, содержащих один компаратор (нуль орган). В таких преобразователях считывание выходного кода производится непосредственно после отработки входного аналогового сигнала с помощью блока считывания, управляемого импульсами, генерируемыми компаратором в момент равенства входного и уравновешивающего напряжений. Подобным же образом осуществляют и съем кода с выхода тех аналого-кодовых преобразователей, в которых входная величина пре. образуется в пропорциональный интервал времени. заполняемый импульсами образцовой частоты, количество которых затем подсчитывают с помощью счетчика. Съем показаний со счетчика осуществляют также после прихода управляющего импульса, который генерируется схемой величин,Недостаток такого способа - возможность его использования только для преобразователей, построенных по способу последовательного счета, которые характеризуются малым быстро. действием. В более быстродействующих аналого- кодовых преобразователях рассмотренный спо. соб съема кода не может найти применения, что ограничивает область его практического ислользования 1.Наиболее близким техническим решением к изобретению является способ считывания выходного кода аналого-кодовых преобразователей поразрядного кодирования, обладающих высоким быстродействием. Максимальное количество тактов отработки у и-разрядного преобразователяпоразрядного кодирования равно и. Известньй способ обеспечивает считывание кода на протя. жении и + 1 такта при поступлении на компаратор и + 1 импульса с генератора тактовых импульсов 2.Недостатком668083аналого кодовых преобразователей поразрядного кодирования с индивидуальнымИ компарато.рами в каждом разряде (комбинированногоуравновешивания).Целью изобретения является повышение бы.стродействия.Поставленная цель достигается тем, что поспособу считывания выходного кода аналогокодового преобразователя комбинированногоуравновешивания, основанному на съеме кода 1 опутем стробированного считывания, съем кодаосуществляют непосредственно вслед за окончанием последнего изменения состояния самогомладшего разряда, для чего каждое изменениесостояния младшего разряда преобразуют в 15импульс, который на время своей длительностизапрещает считывание кода, причем длительностьэтого импульса выбирают равной длительностиодного такта отработки процесса аналого-кодо.вого преобразования. 20На фиг. 1 приведена блок-схема устройства,реализующего предлагаемый способ; на фиг,2показаны временные зависимости сигналовосновных блоков устройства,Устройство содержит п.разрядный аналогокодовый преобразователь комбинированногоуравновешивания 1, определитель 2 положитель.ного знака производной и определитель 3 отрицательного знака производной, два одновибрато.ра 4, 5, двухвходовой элемент ИЛИ 6 и элементзоЗАПРЕТ 7 с и сигнальными входами и однимзапрещающим. Каждый из выходов всех разря.иов аналого-кодового преобразователя соединенс соответствующим сигнальным входом элемен.та ЗАПРЕТ 7, кроме того, выход самого млад.щего (и-го) разряда соединен с входами опре.делителей 2 и 3 знаков производной. Выходыпоследних соединены через соответствующиеодновибраторы 4, 5 и двухвходовой логическийэлемент ИЛИ б с запрещающим входом элемен ота ЗАПРЕТ.Работает устройство следующим образом.Если на входе аналого-кодового преобразо.вателя 1 происходит изменение преобразуемогосигнала (Ос в моменты т, и т на фиг, 2),которое отрабатывается за Х тактов, то соответственно Х раз изменяется амплитуда сигнала на выходе млашпсго разряда (О, на фиг.2).С помощью определителей 2 и 3 знаков производной, в качестве которых могут быть ис 5 Опользованы, например, дифференцирующие це 6пи, выделяются положительные и отрицатель.ные фронты напряжения О причем на выходеопределителей появляются импульсы О и О 3,соответствующие положительным и отрицательным фронтам. Импульсы О и Оз запускаютсоответствующие одновибраторы 4, 5, которыеформируют управляющие импульсы длительнос.ти т - О 4, О,. В этом случае на выходе элемента ИЛИ б появляются импульсы Огдлительность которых равна Хт. Эти импульсына время своей длительности запрещают съемвыходного кода с выхода аналого. кодовогопреобразователя и одновременно сигнализируютоб отсутствии достоверной информации на вы.ходе устройства. Съем кода осуществляетсянепосредственно после окончания запрещающего импульса длительности Х т,Таким образом, предложенный способ позволяет осуществлять съем выходного кода аналого. кодового преобразователя комбинированного уравновешивания после окончания аналого-кодо вого преобразования через интервал времени, не превышающий длительности одного такта отработки. входного сигнала указанным аналого- кодовым преобразователем.Формула изобретенияСпособ считывания выходного кода аналого. кодового преобразователя комбинированного уравновешивания, основанный на съеме кода путем стробированного считывания, о т л и ч аю щ и й с я тем, что, с целью повышения быст. родействия, съем кода осуществляют непосред. ственно вслед за окончанием последнего изменения состояния самого младшего разряда, для чего каждое изменение состояния младшего раз. ряда преобразуют в импульс, который на время своей длительности запрещает считывание кода, причем длительность этого импульса выбирают равной длительности одного такта отработки процесса аналого-кодового преобразования.Источники информации, принятые во внимание при экспертизе1. Гитис Э. И, Преобразователи информации для электронных цифровых вычислительных устройств, М"Энергия", 1975, с. 297.2. Там же, с, 302.668086 яющ юлИ оставитель А. Воител ехред Н. Андреичук ктор Т, Юрчиков орректор С, Патрушева Тираж 1059 ПЦНИИПИ Государственного комитета СС по делам изобретений и открытий 13035, Москва, Ж - 35, Раушская наб Заказ 3483/50 сное

СмотретьЗаявка

2398345, 03.08.1976

ФИЗИКО-ТЕХНИЧЕСКИЙ ИНСТИТУТ АН УКРАИНСКОЙ ССР

ПОГРИБНОЙ ВЛАДИМИР АЛЕКСАНДРОВИЧ, РОЖАНКОВСКИЙ ИГОРЬ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: H03K 13/03

Метки: аналого-кодового, выходного, кода, комбинированного, преобразователя, считывания, уравновешивания

Опубликовано: 15.06.1979

Код ссылки

<a href="https://patents.su/3-668086-sposob-schityvaniya-vykhodnogo-koda-analogo-kodovogo-preobrazovatelya-kombinirovannogo-uravnoveshivaniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ считывания выходного кода аналого-кодового преобразователя комбинированного уравновешивания</a>

Предыдущий патент: Аналого-цифровой сглаживающий преобразователь

Следующий патент: Устройство парафазного цифроаналогового преобразования с самоконтролем

Случайный патент: Валковая мельница