Аналого-цифровой преобразователь поразрядного кодирования

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 657607

Авторы: Оранжереев, Фетисов

Текст

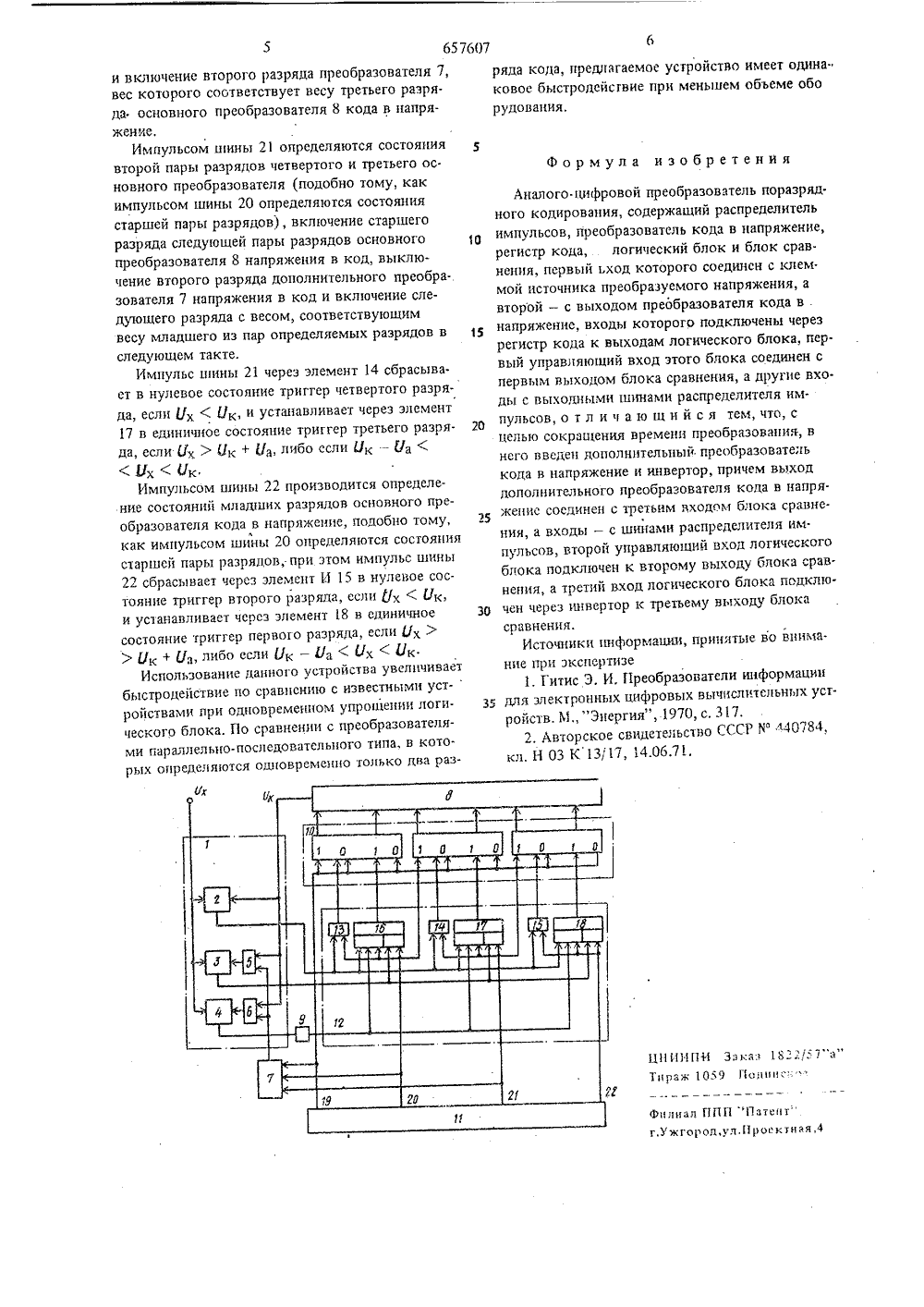

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) Заявлено 26.04 76 (21) с присоединением заявки(23) Приоритет 03 К 13 17 ааударстаенный намнтет СССР аа делам нэааретеннй н аткрытнйОпубликовано 15 04 79 Бюллет 14 3) у 325 8.8 Дата опубликовани исания 19.04.79 Авторыизобретени(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛ ПОРАЗРЯДНОГО КОДИРОВАНИЯ Изобретение относится к импульсной аналогоцифровой технике и может быть использованов аналого-цифровых преобразователях постоянных напряжений, обеспечивая при простое текин.ческой реализации высокое быстродействие.Известно устройство для преобразования аналоговой информации в цифровую параллельнопоследовательного типа с совмещением методовсчитывания и поразрядного кодирования, обладающее более высоким быстродействием, чемпреобразователи поразрядного кодирования, содержащее распределитель импульсов, преобразователь кода в напряжение, схему сравнения илогический блок 11.Недостатком известного устройства являетсяувеличение количества оборудования по сравнению с преобразователями, выполненными по ме.тоду поразрядного кодирования.Известен аналого-цифровой преобразовательпоразрядного кодирования, содержащий блоксокращения тактов и сквозного переноса схемысравнения, преобразователь кода в напряжение,регистр, распределитель импульсов и логическийблок 121,В этом устройстве сокращение времени преобразования происходит.за счет того, что в зависимости от величины преобразуемого сигнала обес.печиваетсясокращение или пропуск некоторыхтактов уравновешивания. Однако при довольно 5 значительном усложнении устройства выигрышв быстродействии невелик, Так, например, впятиразрядном преобразователе среднее числотактов на одно преобразование при равномерномзаконе распределения преобразуемых напряжед ния составляет 4,5, а выигрыш в быстродействии - 10%, что является недостатком известного устройства,Цель изобретения - увеличение быстродействия преобразования.Для достижения этой цели в аналого.цифро. вой преобразователь поразрядного кодирования содержащий распределитель импульсов, преобразователь кода в напряжение, регистр кода, логический блок и блок сравнения, первый вход которого соединен с клеммой источника преобразуемого напряжения, а второй - с выходом преобразователя кода в напряжение, входы ко. топого подключены через регистр кода к выхо7607 3 65дам логического блока, первый управляющийвход этогс блока соединен с первым выходомблока сравнения, а другие вхсдв - с выходными шинами распределителя импульсов, введендополнительный преобразователь кода в напряжение и инвертор, причем выход дополнитель.ного преобразователя кода в напряжение соеди.нен с третьим входом блока, сравнения, а входы - с шинами распределителя импульсов, второй управляющий вход логического блокаподключен к второму выходу блока сравнения,а третий вход логического блока подключен че.рез инвертор к третьему выходу блока сравнения.На чертеже изображена структурная схемапредлагаемого устройства.Для примера взят шестиразрядный преобразователь, содержащий блок сравнения 1, состоящийиз нуль-органов 2 - 4 и аналоговых блоков сложения 5 и блока вычитания б, дополнительный преобразователь 7 кода в напряжение, основнойпреобразователь 8 кода в напряжение, инвертор9, регистр 10, распределитель 11 импульсов логического блока 12, состоящего из элементовИ 13 - 15, элементов 2 И.ИЛИ 16 - 18, входныешины 19 - 22 распределителя импульсов,Первый вход блока сравнения 1 соединен систочником преобразуемого напряжения, второйвход - с выходом преобразователя 8; входпоследнего через регистр 10 кода соединен с выходом блока 12; первый управляющий вход блока 12 соединен с первым выходом блока сравнения 1, а доугие входы - с выходами распределителя 11 импульсов; выход дополнительногопреобразователя 7 соединен с третьим входомблока сравнения 1, а входы этого преобразователя - с шинами распределителя 11, второй уп.равляющий вход блока 12 соединен с вторымвыходом блока сравнения 1 измеряемого напря.жения с суммой напряжения, а третий вход ло.гическогс блока 12 через инвертор 9 подключенк третьему выходу блока 1 измеряемого напряжения с разностью натряжений преобразователей8 и 7; выход аналогового блока сложения 5 сое.динен с входом нуль-органа 3, а выход аналогового блока вычитания 6 - с входом нуль-органа4; шина 19 распределителя 11 соединена с установкой единицы старшего и установкой нулейостальных разрядов триггеров регистра кода; ашины 20 - 22 - с установочными входами групппо два разряда регистра 10 кодов через логический блок 12, причем шины 20 - 22 соединены свходом установки нуля старшего из группы триггера через двухвходовые элементы И 13 - 15,другие входы которых соединены с выхадомблока сравнения 1 измеряемого напряжения снапряжением преобразователя 8, а с входамиустановки единицы младших из групп триггеровчерез элементы 2 ИИЛИ 16 - 18; другие входы элементов 2 И.ИЛИ 16 8 у двухвходовых эле.ментов И соединены с вторым входом блока 12,у трехвходовых элементов И - один с первым,а другойс третьим входами логического бло. ка 12; шины 20 и 21 соединены со входами ус. тановки единицы соответственно триггеров четвертого и второго разрядов регистра 10 кодов.На первом выходе блока сравнения 1 (выход нуль-органа 2) вырабатывается сигнал "Г, если УхУк, и сигнал "0", если Ух: Ук, где цх - измеряемое напряжение; Ук - напряжение компенсации на выходе основного преобраэо.вателя 8. На втором выходе блока сравнения 1 (выходнуль-органа 3) вырабатывается сигнал "1", еслиУх ) Ук + Уа и сигнал "0", если УхЦк++ Уа, где Уа - напряжение на выходе преобра. эователя 7 кода в напряжение; Ок+Оа - напряжение на выходе алалогового блока сложения 5 На третьем выходе блока сравнения 1 (выход нуль органа 4) вырабатывается сигнал "1", если УхЫк - Уа и сигнал 0", если УхУк -- Уа где Цк - Уа - напряжение на выходе аналогового блока вычитания 6.Импульсом с шины 19 устанавливаются в ре. гистре 10 все разряды, кроме старшего, в нулевое состояние, шестой разряд устанавливается в единичное состояние, в преобразователе 7 устанавливается в единичное состояние старший разряд, вес которого соответствует весу пятого разряда основного преобразователя кода в. на. пряжение, остальные два разряда устанавливаются в нулевое состояние. Импульсом с шины 20 производится установка шестого и пятого разрядов регистра 10 в состояние, определяемое соотношением напряжений на выходе блока сравнения 1.Если Ух ) Ук и Ых ) Ук . Уа, то шестой раэ. ряд остается в единичном состоянии, а пятый устанавливается в единичное состояние через двухвходовый элемент И элемента 2 И-ИЛИ 16,Если УхУк и УхУк + Уа, тс шестой раз. ряд остается в единичном состоянии, а пятый в нулевом, так как на установочные входы обо. их триггеров импульс шины 20 не проходит.Если ЦхЦк и Ух ) Ук - Ыа то шестой разряд устанавливается в нулевое состояние через элемент 13, а пятый - в едини пгсе состоя. ние через трехвходовый элемент И элемента 2 И-ИЛИ 16.Если ЦхУк и йУк - Уа, то шестой разряд устанавливается в нулевое состояние че. рез элемент И 13, а пятый остается в нулевом состоянии, поскольку импульс шипы 20 через элемент 2 И-ИЛИ 16 не проходит.)Одновременно импульсом шины 20 производится установка в единичное положение четвертого разряда регистра 10 и выключение третьего657607 ППП Патент л,уя.проектная Фияиаг г,ужго и включение второго разряда преобразователя 7, вес которого соответствует весу третьего разря.да основного преобразователя 8 кода в напря.жение.Импульсом шины 21 определяются состояния второй пары разрядов четвертого и третьего ос.новного преобразователя (подобно тому, как импульсом шины 20 определяются состояния старшей пары разрядов), включение старшего разряда следующей пары разрядов основного преобразователя 8 напряжения в код, выключение второго разряда дополнительного преобразователя 7 напряжения в код и включение следуюшего разряда с весом, соответствующим весу младшего из пар определяемых разрядов в следуюШем такте.Импульс шины 21 через элемент 14 сбрасывает в нулевое состояние триггер четвертого разря. да, если 4/х ( Цк, и устанавливает через элемент 17 в единичное состояние триггер третьего разряда, если СУх ) Цк + Уа, либо если Ц - Ца ( Ух кИмпульсом шины 22 производится определение состояний младних разрядов основного преобразователя кода в напряжение, подобно тому,лкак импульсом шины 20 определяются состояния старпей пары разрядов, при этом импульс шины 22 сбрасывает через элемент И 15 в нулевое состояние триггер второго разряда, если Цх ( Ук, и устанавливает через элемент 18 в единичное состояние триггер первого разряда, если 1/х: ) Ц, + Ца, либо если Цк - Ца ( У ( Цк,Использование данного устройства увеличивает быстродействие по сравнению с известными уст-ройствами при одновременном упрощении логического блока. По сравнении с преобразователями параллельно-последовательного типа, в которых определяются одновременно только два разряда кода, предлагаемое устройство имеет одина.ковое быстродействие при меньшем объеме оборудования. Формула изобретения Аналого цифровой преобразователь поразряд.ного кодирования, содержащий распределительимпульсов, преобразователь кода в напряжение,регистр кода, логический блок и блок срав.ненця, первый ьход которого соединен с клем.мой источника преобразуемого напряжения, авторой - с выходом преобразователя кода в .напряжение, входы которого подключены черезрегистр кода к выходам логического блока, первый управляющий вход этого блока соединен спервым выходом блока сравнения, а другие входы с выходилми шинами распределителя им.пульсов, о т л и ч а ю ьц и й с я тем, что, сцелью сокращения времени преобразования, внего введен дополнительный преобразователькода в напряжение и инвертор, причем выходдополнительного преобразователя кода в напряженис соединен с третьим входом блока сравнения, а входы - с шинами распределителя им.пульсов, второй управляюгций вход логическогоблока подключен к второму выходу блока срав.нения, а третий вход логического блока подктпозо чен через ицвертор к третьему выходу блокасравненияИсточники информации, принятые во вцима.ние при экспертизе1. Гитис Э. И. Преобразователи информацииЗ 5 для электронных цифровых вычислительных устройств. М., "Энергия", 1970, с. 317.2, Авторское свидетельство СССР Ч 40784,кл. Н 03 К 13/17, 14.06,71, 1 ПИ Залая 18 ./: 7"1)аж 1059 1 олиие

СмотретьЗаявка

2351926, 26.04.1976

ПРЕДПРИЯТИЕ ПЯ А-1586

ОРАНЖЕРЕЕВ ВАЛЕРИЙ МИХАЙЛОВИЧ, ФЕТИСОВ ВЯЧЕСЛАВ КОНСТАНТИНОВИЧ

МПК / Метки

МПК: H03K 13/17

Метки: аналого-цифровой, кодирования, поразрядного

Опубликовано: 15.04.1979

Код ссылки

<a href="https://patents.su/3-657607-analogo-cifrovojj-preobrazovatel-porazryadnogo-kodirovaniya.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой преобразователь поразрядного кодирования</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Аналого-цифровой преобразователь

Случайный патент: Устройство для вихретокового контроля