Устройство для коррекции фазы цифровых сигналов записи и считывания

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 644408

Автор: Андре

Текст

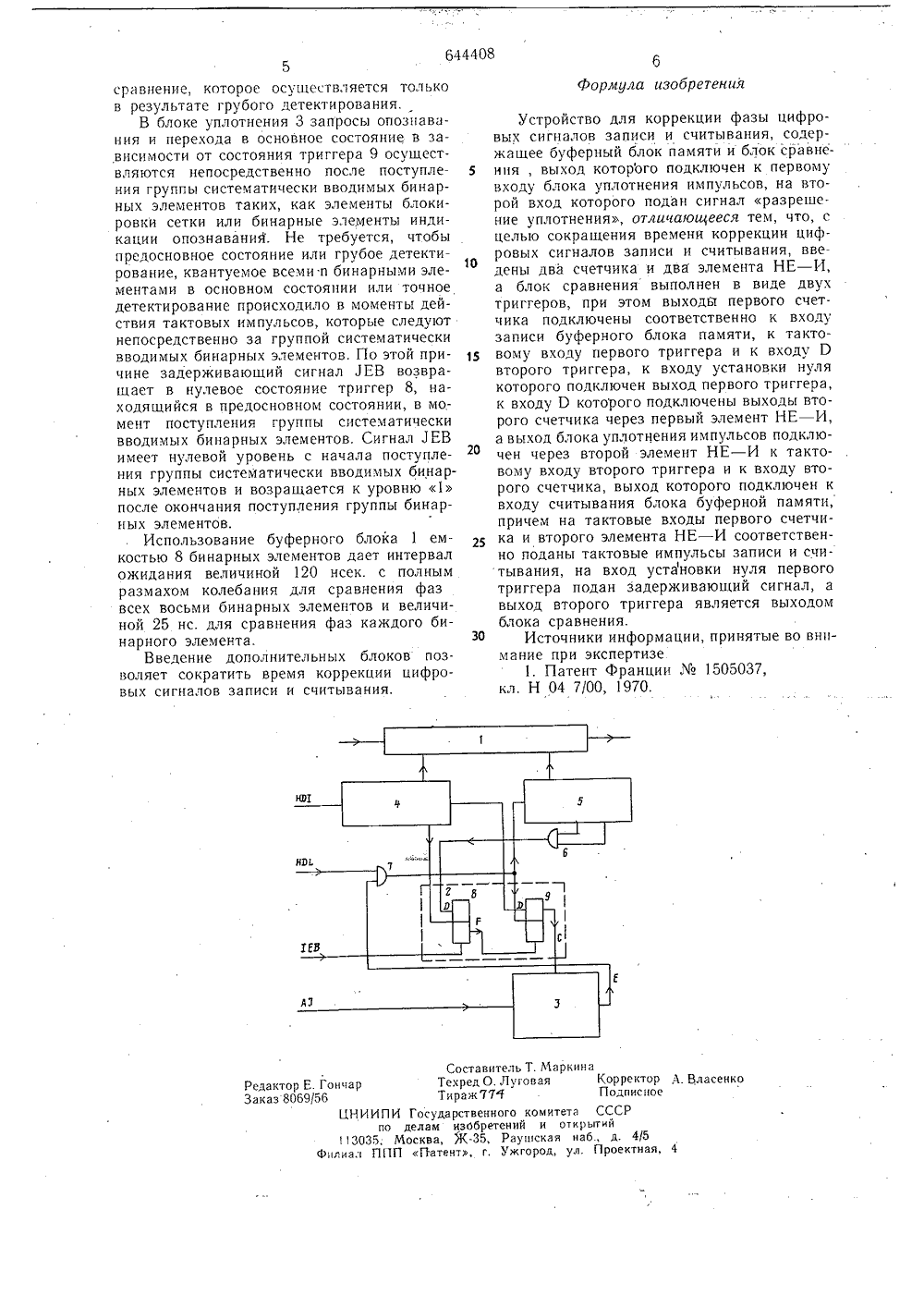

ОП ИСАНИ ЕИЗОБРЕТЕН ИЯИ ПАТЕНТУ Союз Советских Сощиалистических Респубпик(22) Заявлеио 15,04,7 енту 51) М, Кл. 23431 54 32) 18,.04, 1 331 франц 2 оритет Н 04 Е 7/02 осударственный коиетет СССР по делам нзобретеннй н открытий) УДК 62 публиковаио 25. 01. 79,Бюллетень3 ата опубликования описания 28,01.7 2 (088(72) Автор изобретены ИностранецАндре Огюст А(франция)ИностраннСосьете Анони ая фирмам де Тел(71) Заявитель мюника УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ФАЗЬЦИФРОВЫХ СИГНАЛОВ ЗАПИСИИ СЧИТЫВАНИЯ 2 цифро содер равне Изобретение относится к технике связи и может использоваться в устройствах опознавания цифровой последовательности, в частности в устройствах для сравнения фаз сигналов записи и считывания.Известно устройство для коррекции фазы цифровых сигналов записи и считывания, содержащее буферный блок памяти и блок сравнения, выход которого подключен к первому входу блока уплотнения импульсов, на второй вход которого подан сигнал разрешение уплотнения, однако данное устройство имеет большое время коррекции цифровых сигналов записи и считывания 1.Цель изобретения - сокращение времени коррекции цифровых сигналов записи и считывания.Для этого в устройство для коррекции фазы цифровых сигналов записи и считывания, содержащее буферный блок памяти и блок сравнения, выход которого подключен к первому входу блока уплотнения импульсов, на второй вход которого подан сигнал разрешение уплотнения, введены два счетчика и два элемента НЕ - И, а блок сравнения выполнен в виде двух триггеров, при этом выходы первого счетчика подключены соответственно к входу записи буферного блока памяти, к тактовому входу первого триггера и к входу 0 второго триггера, к входу установки нуля которого подключен выход первого триггера, к входуИ которого подключены выходы второго счетчика через первый элемент НЕ - И, а выходблока уплотнения импульсов подключен через второй элемент НЕ - И к тактовому вхо- О ду второго триггера и к входу второго счетчика, выход которого подключен к входу считывания блока буферной памяти, причем на тактовые входы первого счетчика и второго элемента НЕ - И соответственно поданы тактовые импульсы записи и считывания, на вход установки нуля первого триггера подан задерживающий сигнал, а выход . второго триггера является выходом блока сравнения.На чертеже изображена структурнаяэлектрическая схема предложенного устройства.Устройство для коррекции фазывых сигналов записи и считывания жит буферный блок 1 памяти и блок сция 2, выход которого подключен к первомувходу блока уплотнения 3 импульсов, ца второй вход которого подан сигнал разредецце уплотнения, а также два счетчика 4,5 и два элемента НЕ И 6 и 7, а блок сравнения 2 выполнен в виде двух триггеров 8 и 9, 5при этом выходы первого счетчика 4 подключены соответственно к входу записи буферного блока 1 памяти, к тактовому входупервого триггера 8 и к входу Р второготриггера 9, к входу установки нуля которогоподключен выход первого триггера 8, к входу Р которого подключены выходы второгосчетчика 5 через первый элемент НЕ - И 6,а выход блока уплотнения 3 импульсов подключен через второй элемент НЕ - И 7 ктактовому входу второго триггера 9 и к 15входу второго счетчика 5, выход которогоподключен к входу считывания буферногоблока 1 памяти, причем на тактовые входыпервого счетчика 4 и второго элементаНЕ - И 7 соответственно поданы тактовыеимпульсы записи и считывания, на входустановки нуля первого триггера 8 поданзадерживающий сигнал, а выход второготриггера 9 является выходом блока сравнения 2,С помощью предлагаемого устройствавозможно числовое сравнение фаз тактовых сигналов записи и тактовых сигналовсчитывания в дискретные моменты сравнения, причем эти моменты появляются благодаря переходам сравниваемых тактовых сигналов. Устройство позволяет производитьгрубое сравнение фаз или детектированиеперехода в основное состояние посредством квантования моментов сравнения, соответствующих и бинарным элементам и точное сравнение фаз или детектирование перехода в основное состояние посредствомквантования моментов сравнения, равныходному бинарному элементу, причем точноесравнение приводится в действие в результате грубого сравнения.Точное сравнение является необходимым, . 40так как одно грубое сравнение может вопределенных частотных условиях вызватьчрезмерный интервал ожидания во времяуплотнения, Кроме того, благодаря устройству возможна предварительная оценка сдвига фаз, достаточная для осуществления опознания.Устройство работает следующим образом.В олок сравнения 2 поступают тактовыесигналы от счетчиков 4 и 5. Блок сравнения2 выдает сигнал С, передаваемый в блок 5 очлотнения 3. В блоке уплотнения переходв основное состояние осуществляется введением в буферный блок 1 запроса опознавания. Осуществление этого опознавания или.введение одного бинарного элемента вызывает скачок фазы на длительность одногобинарного элемента и, таким образом, выход из осйовного состояния. Сигнал Е стирация длительности одного тактового импульса, вызывающий выход из основного состояния, вводится через элемент НЕ - И 7.В блок уплотнения 3, кроме того, поступает сигнал разрешения опознаванияЛЛ, формируемый во время выработки сеткис помощью импульса сетки в промежутоквремени, предназначенный для бинарногоэлемента опознавания. В блоке уплотнения3 запоминается сигнал С и восстанавливается сигнал Г, когда в запоминающееустройство поступает сигцал А.Сдвиг фаз между тактовыми сигналамизаписи НРЗ и считывания НР 1., достаточендля осуществления грубого детектированияи тем более, точного детектирования. Сигнал ., поступающий из счетчика 4, представляет собой сигнал с частотой Ге/и, гдеи - число тактов считывания, На вход триггера 8 поступает сигнал Я, а также сигнал6, полученный на выходе элемента НЕ - И6, на который приходят два сигнала от счетчика 5, и представляющий собой импульсотрицательной полярности с длительностью,равной 1/Ре во все п отрезков тактовогопериода считывания, Поскольку переднийфронт сигнала 8 лежит вне длительностиимпульса сигнала 6, то выход триггера 8остается в нулевом состоянии и, таким образом, блокирует в нулевом состоянии выход триггера 9,Более значительный сдвиг фаз междутактовым сиГналом записи НРЗ, с частотойГе и тактовым сигналом считывания НР 1со средней частотой Ре. Передний фронт сигнала 8 сравнивается с состоянием сигнала 6, и выход триггера 8 переходит в состояние 1, т. е. в основное состояние. Сигнал, выходящий с выхода триггера 8, приводит в действие триггер 9 основного состояния. В этот момент выход триггера 9, на вход тактового устройства которого поступают тактовые сигналы записи НР,1 и тактовые сигналы считывания НР 1., остается в нулевом состоянии и не готов перейти в основное состояние. Переход в основное состояние триггера 9 происходит в момент, когда сдвиг фазы достаточен и когда, таким образом, передний фронт тактового сигнала считывания НР 1. по времени соответствует части 1 тактового сигнала записи НРЗ: Таким образом, посредством триггера 9 осуществляется переход в основное состояние, т. е. переход этого триггера 9 в состояние 1, начйная с момента перехода в предосновное состояние, в любой момент тактового сигнала считывания НР 1 когда сдвиг фаз становится достаточным. Полученный таким образом период ожидания является минимальным, Триггер 8 осуществляет сравнение по фазе всех п бинарных элементов. Это - грубое детектирование. Триггер 9 осуществляет сравнение по фазе всех бинарных элементов; это - точное644408 Формула изобретения Т. М оная Составител Техред О. Л Тираж 77 Государственного делам изобретени осква, К.35, Ра Патент, г. Ужина Корректор А. Власенко Подписное Редактор Е. Гончар Заказ 8069(56 а С ЦНИИП по 113035; филиал ПГ/5ная, 4 наб., л. П сравнение, которое осуществляется только в результате грубого детектирования.В блоке уплотнения 3 запросы опознавания и перехода в основное состояние в зависимости от состояния триггера 9 осуществляются непосредственно после поступления группы систематически вводимых бинарных элементов таких, как элементы блокировки сетки или бинарные элементы индикации опознаваний. Не требуется, чтобы предосновное состояние или грубое детектирование, квантуемое всеми и бинарными элементами в основном состоянии или точное детектирование происходило в моменты действия тактовых импульсов, которые следуют непосредственно за группой систематически вводимых бинарных элементов. По этой причине задерживающий сигнал ЗЕВ возвращает в нулевое состояние триггер 8, находящийся в предосновном состоянии, в момент поступления группы систематически вводимых бинарных элементов. Сигнал 1 ЕВ имеет нулевой уровень с начала поступления группы систематически вводимых бинарных элементов и возращается к уровню 1 после окончания поступления группы бинарных элементов.Использование буферного блока 1 емкостью 8 бинарных элементов дает интервал ожидания величиной 120 нсек. с полным размахом колебания для сравнения фаз всех восьми бинарных элементов и величиной 25 нс. для сравнения фаз каждого бинарного элемента.Введение дополнительных блоков позволяет сократить время коррекции цифровых сигналов записи и считывания. Устройство для коррекции фазы цифровых сигналов записи и считывания, содержащее буферный блок памяти и блок сравне 5 ния, выход которого подключен к первомувходу блока уплотнения импульсов, на второй вход которого подан сигнал разрешение уплотнения, отличающееся тем, что, сцелью сокращения времени коррекции циф 10ровых сигналов записи и считывания, введены два счетчика и два элемента НЕ - И,а блок сравнения выполнен в виде двухтриггеров, при этом выходы первого счетчика подключены соответственно к входузаписи буферного блока памяти, к такто 15 вому входу первого триггера и к входу Рвторого триггера, к входу установки нулякоторого подключен выход первого триггера,к входу Р которого подключены выходы второго счетчика через первый элемент НЕ - И,а выход блока уплотнения импульсов подклю 20чен через второи элемент НЕ - И к тактомвому входу второго триггера и к входу второго счетчика, выход которого подключен квходу считывания блока буферной памяти,причем на тактовые входы первого счетчика и второго элемента НЕ - И соответственно поданы тактовые импульсы записи и считывания, на вход установки нуля первоготриггера подан задерживающий сигнал, авыход второго триггера является выходомблока сравнения.Источники информации, принятые во внимание при экспертизе1. Патент Франции Мо 1505037,кл, Н 04 7/00, 1970.

СмотретьЗаявка

2343154, 15.04.1976

Иностранец Андре Огюст Авено, Иностранная фирма "Сосьете Аноним де Телекоммюникас, вш: о№31дя, ^^iIiГ; ^^, ОН-"ifjlff, SiiSJiMO-fPi

АНДРЕ ОГЮСТ АВЕНО

МПК / Метки

МПК: H04L 7/02

Метки: записи, коррекции, сигналов, считывания, фазы, цифровых

Опубликовано: 25.01.1979

Код ссылки

<a href="https://patents.su/3-644408-ustrojjstvo-dlya-korrekcii-fazy-cifrovykh-signalov-zapisi-i-schityvaniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для коррекции фазы цифровых сигналов записи и считывания</a>

Предыдущий патент: Устройство для защиты трехфазного электродвигателя компрессорной установки от перегрузки

Следующий патент: Частотный детектор цветовых телевизионных сигналов

Случайный патент: Сустав манипулятора