Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 607222

Авторы: Барбакова, Игнатьев, Кисельников, Мясников, Торгашев

Текст

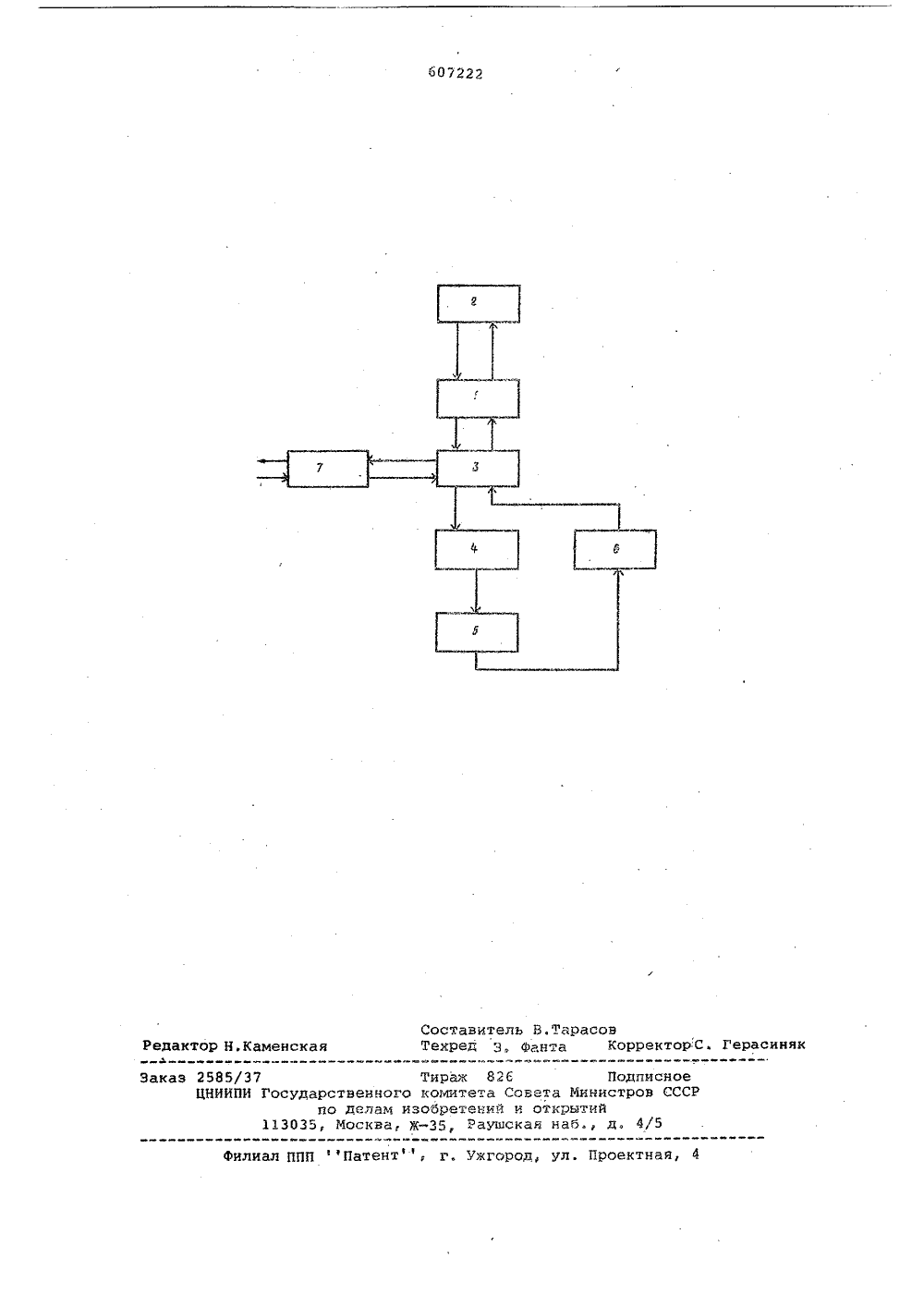

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических Республик/О Гааударатввнный комитетСовета Мнниатрав СССРво данам иэаоретвнийи атнрытнй 3) в 1 риорит ДК 681. 325(43) Опубликовано 150578,Бюллетень ла 1 (45) Лата опубликования описания 26047 2) Авторы изобретен.В,Барбакова, М.Б.Игнатьев, В.М.Кисельников В.А.Мясников и В.А.Торгашев тенинградский институт авиа и Государственный Комитет и риборостроениятехнике при СИ СССР нно аук О 11 нсс ого устройства ействие.вляется повыще игается тем, ство введены ерации ипричем трея через блок и и блок асчен ко входу-схема метический вной памя 4 форми 5 ассоциаи микропро- теративной выполнениитующим обрая сл полнен оминаю в блок 3.ый кодможетных споИзобретение относится к областивычислительной техники и может бытьиспользовано при построении процессоров с микропрограммным управлением,Известен процессор вычислительных 5систем 11, в работе которого используется микропрограммный принцип выполнения операций,Наиболее близким по техническойсущности к изобретению является процессор с микропрограммным управлением2, содержащий арифметический блок,блок сверхоперативной памяти, блокуправления, блок памяти микропрограмми блок управления оперативной памятью, 15причем выход блока сверхоперативнойпамяти соединен с первым входом арифметического блока, первый выход которого подключен к первому входу блокауправления, первый выход которого со- Ю.единен со входом блока управления оперативной памятью, выход которого подключен ко второму входу блока управления, второй выход которого соединенсо вторым входом арифметического блока, второй выход которого подключенко входу блока сверхоперативной памяти, выход блока памяти микропрограммсоединен с третьим входом блока управления. Недостатком известнявляется низкое быстродЦелью изобретения яние быстродействия.Поставленная цель дастчто в предлагаемое устройблок Формирования кода опблок ассоциативной памятитий выход блока управлениФормирования кода операцисоциативной памяти подклюблока памяти микропрограмм,На чертеже представлена блпроцессора.Она включает в себя арифблок 1, блок 2 сверхоператити,. блок 3 управления, блокрования кода операции, блоктивной памяти, блок 6 памятграмм и блок 7 управления опамятью.Работа процессора приопераций организуетс еузом.Код команды, подлежащий выпоступает из оперативного эапщего устройства через блок 7Команда содержит обобщенноперации и адреса операндов (быть применен любой из известсобов адресации), Обобщенный код операции, который не содержит информации о виде обрабатываемых операндов, поступает затем в блок 4, По адресам, содержащимся в коде комаьды, блок 3 через блок 7 вызывает из оперативной памяти системы"начальные байты;операндов, содержащие их характеристики, в частности - указания на вид операндов.Виды операндов, как и обобщенный 10 код операции, поступают в блок 4, который модифицирует обобщенный код операции видов Ьперандов, Формируя тем самым конкретный код операции.Эта модификация может выполняться, в ц частности, как слияние обобщенного кода операции и вида, операндов.,Сформированный код операции поступает в блок 5, где используется в, ка- Я четсве ассоциативного признака для поиска адреса микропрограммы операции.Найденный адрес подается в блок 6. Микропрограмма из блока б поступает в блок 3, который осуществляет управ ление Работой блока 1. Блок 2 осуществляет в ходе выполнения микропрограммы хранение операндов, промежуточных данных и результатов вычислений.Данный принцип организации процес сора обеспечивает следующие преимущества. При использовании обобщенных кодов операций повышается уровень внутреннего языка вычислительной системы, в результате чего уменьшается необходимость вмешательства программиста в работу низших уровней операционной системы, Возрастает унифицированность программного обеспечения; так как при использовании обобщенных кодов операций подпрограммы становится в значи тельной степени инвариантны по отношению к видам обрабатываемой информации. Как следствие униФикации программ - уменьшается их количество и снижается вероятность ошибок при обращении к ним 45 т.е. возрастает надежность математического обеспечения. Надежность возрастает и эа счет упрощения структуры транслятора, который при использовании данного принципа организации процессора не должен заниматься обработкой описаний. Номенклатура различных операций, выполняемых процессором, может быть гибко расширена, так как предлагаемый снособ Формирования кодов операций допускает увеличение длины этих кодов и сочетание всего многообразия обобщенных кодов операций с кодами видов операндов.Формула изобретенияПроцессор, содержащий арифметический блок, блок сверхоперативной памяти, блок управления, блок памяти мик" ропрограмм и блок управления оператив ной памятью, причем выход блока сверхюперативной памяти соединен с первым входом арифметического блока, первый выход которого подключен к первому входу блока управления, первый выход которого соединен со входом блока управления оперативной памятью, выход которого подключен ко второму входу блока управления, второй выход которого соединен со вторым входом арифметического блока, второй выход которого подключен ко входу блока сверхоперативной памяти, выход блока памяти микропрограмм соединен с третьим входом блока управленя, о т л и ч а ю - щ и й с я тем, что, с целью повышения быстродействия, в него введены блок Формирования кода операции и блок ассоциативной памяти, причем третий выход блока управления через. блок формирования кода операции и блок ассоциативной памяти подключен ко входу блока памяти микропрограмм.Источники информации, принятые во внимание при экспертизе:1. ШелихоВ А,А , Селиванов Ю.П.Вычислительные машины, М., Энергия, 1973 ф с. 22.2. Флорес А. Организация вычислительных машин, М., Мир, 1972, с. 295.т 9: Е Вщ ЭФ3 ЭЕ Е т Тираж 826 Подписное енного коьжтета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Эаказ 25 В 5/37 цНИИПИ Государств илиал ППП фПатент", г. Ужгород, ул. Проектная, 4 Составитель В.Тарасоведактор Н,Каменская Техреду Э, Фанта КорректорС. Герасиняк

СмотретьЗаявка

2052305, 27.08.1974

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ, ГОСУДАРСТВЕННЫЙ КОМИТЕТ ПО НАУКЕ И ТЕХНИКЕ ПРИ СМ СССР

БАРБАКОВА ИРИНА ВЛАДИМИРОВНА, ИГНАТЬЕВ МИХАИЛ БОРИСОВИЧ, КИСЕЛЬНИКОВ ВЛАДИМИР МАКСИМОВИЧ, МЯСНИКОВ ВЛАДИМИР АЛЕКСАНДРОВИЧ, ТОРГАШЕВ ВАЛЕРИЙ АНТОНОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: процессор

Опубликовано: 15.05.1978

Код ссылки

<a href="https://patents.su/3-607222-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Устройство для контроля двухтактного двоичного счетчика

Следующий патент: Цифровой функциональный преобразователь

Случайный патент: Стреляющий плавкий предохранитель