Цифровой линейный интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

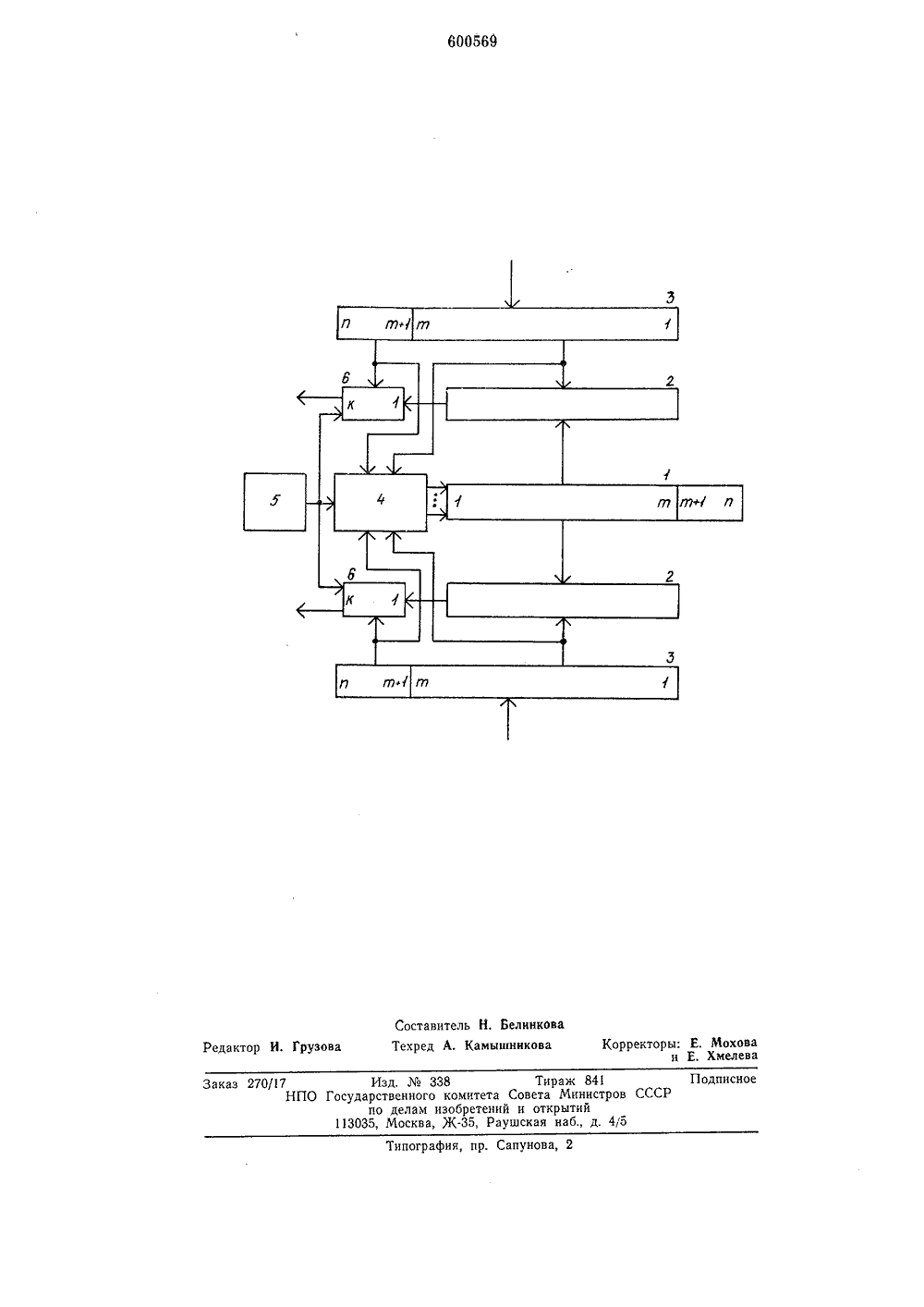

ъ ) ОПИСАНИЕ ИЗОБРЕТЕН ИЯ рц 600569 Соаэ Советским Социалистическим Реслублик(45) Дата опубликования описания 21.04.7 Государствеииыи иомнте Совета Министров СССРло делам изобретенийи открытийФ. Г, Мильнер, И. М, Кулинец " информационно-вычислитель бильного транспорта Белору ехнической кибернетики АН и С. В. Степый центр Мской ССРБелорусской Главныи авто мо т) ЦИФРОВОЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР 2 входы суммирок выходам старподынтегральных младших разрясхем, а входы к выходу генеКоличество таислу регистрове. числу коорвляется интерпоятора - униаждой кооререполнения этому выхоязаны с вхомеханизмов,Выхо тарные динать соотве ды пер дами п Цель изобретения -нтерполятора.Для этого внтерполятора п вышение точност Изобретение относится к автоматике и вычислительной технике, а именно к устройствам управления перемещением исполнительных органов станков с программным управлением, технологических роботов, чертежных автоматов и т. д.Известен по основному авт. св,259492 цифровой линейный интерполятор 11, содержащий генератор тактовых импульсов, регистры подынтегр альных функций, связанные с логическими схемами, и делитель частоты, выходом подключенный к логическим схемам, которые в своей совокупности образуют линейный интерполятор на двоичных умножителях. В состав интерполятора также входит логическая схема анализа приращений, первые входы которой соединены с соответствующими выходами регистров подынтегральных функций, второй вход - с выходом тактового генератора, а выходы - с соответствующими входами делителя частоты.Однако данному интерполятору свойственна методическая погрешность интерполирования, выражающаяся в отклонении траектории исполнительного органа от теоретической прямой. состав цифрового линейного о авт. св,259492 введены накапливающие сумматоры, вания которых подключены ших разрядов регистров функций, входы переносов5 дов - к выходам логических разрешения суммирования - ратора тактовых импульсов ких сумматоров равно ч подынтегральных функций, т0 динат, по которым осущест лирование. дные сигналы интерпол коды перемещений для к - снимаются с выхода п ствующего сумматора, по еполнения сумматоров св риводов исполнительных 20 На чертеже приведена структурная схемацифрового линейного интерполятора.В его состав входит п-разрядный делитель1 частоты, выходы т младших разрядов которого подключены к входам логических схем 25 2, вторыми входами соединенных с выходамит младших разрядов л-разрядных регистров 3 подынтегральных функций приращений.В своей совокупности т младших разрядоврегистров 3, логические схемы 2 и т млад ших разрядов делителя 1 частоты образуютсхему линейного интерполятора на двоичных умножителях.Выходы всех разрядов регистров 3 подключены к входам логической схемы 4 анализа приращений, к входу которой также подсоединен генератор 5 тактовых импульсов, а выходы схемы 4 анализа приращений - к соответствующим входам делителя 1 частоты, Выходы И=т - и старших разрядов регистров 3 соединены с входами суммирования накапливающих lг-разрядных сумматоров 6, входы переноса младших разрядов которых подключены к выходам соответствующих логических схем 2, а входы разрешения суммирования - к соответствующим выходам генератора 5 тактовых импульсов. Число й выбирается исходя из общего числа разрядов и, которыми задаются проекции интерполируемой прямой, таким образом, чтобы выполнялось равенство2 й уя ( л .; - О,5б Зб/что гарантирует получение величины методической погрешности, меньшей чем шаг интерполирования.Работает интерполятор следующим образом.В исходном состоянии накапливающие сумматоры 6 и делитель 1 частоты сброшены в 0, а в регистры 3 занесены величины соответствующих координатных приращений, Будем считать, что разряды регистров 3 и делителя 1 частоты пронумерованы от 1 до п начиная с младших.Схема 4 осуществляет анализ величин всех приращений, хранящихся на регистрах 3, начиная со старших разрядов. Анализ проводится на наличие 0 одновременно во всех более старших разрядах, чем данный, одновременно во всех регистрах подынтегральных функций. При этом, в зависимости от результатов анализа, схема анализа приращений подключает выход генератора 5 тактовых импульсов к входам соответствующих разрядов делителя 1 частоты. Так, если для всех реГистров приращений х, хп 1, , хд= 0(= - 1, О, 1 и - 1) и хотя бы для одного изних х.,= 1, то схема анализа приращенийподключает выход генератора тактовых импульсов к входу (с+2)-го разряда делителячастоты,По каждому управляющему импульсу генератора 5 разрешается суммирование содер 10 жимого й старших разрядов регистров 3 с содержимым Й-разрядных накапливающих сумматоров 6. Этот же импульс через схему 4 поступает на вход соответствующего, например1-го, разряда делителя частоты, опрашивающего при помощи соответствующей логической схемы 2 двоичных умножителей (т - 1+1)младших разрядов регистров 3. Выходныесигналы логических схем 2 поступают на входы переносов младших разрядов соответст 20 вующих сумматоров 6. Сигналы переполнения сумматоров 6 (сигналы переноса из старшего разряда) являются выходными сигналами интерполятора по каждой координате, Интерполирование продолжается до появления25 сигнала переполнения делителя частоты.Включение в состав линейного интерполятора накапливающих сумматоров позволяетповысить точность отработки интерполируемой прямой,30Формула изобретенияЦифровой линейный интерполятор по авт.св.259492, отличающийся тем, что, сцелью повышения точности интерпол ятора,З 5 в него введены накапливающие сумматоры,входы суммирования которых подключены квыходам старших разрядов регистров подынтегральных функций, входы переносов младших разрядов - к выходам логических схем,40 а входы разрешения суммирования - к выходу генератора тактовых импульсов.Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССР259492,45 кл. 6 066 7/30, 1968.Редактор И. Грузова Типография, пр. Сапунова, 2 Заказ 270/17 Изд Мо 338 Тираж 841 Подписное НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

2119841, 27.02.1975

ГЛАВНЫЙ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНЫЙ ЦЕНТР МИНИСТЕРСТВА АВТОМАБИЛЬНОГО ТРАНСПОРТА БЕЛОРУССКОЙ ССР, ИНСТИТУТ ТЕХНИЧЕСКОЙ КИБЕРНЕТИКИ АН БЕЛОРУССКОЙ ССР

МИЛЬНЕР ФРИДРИХ ГРИГОРЬЕВИЧ, КУЛИНЕЦ ИОСИФ МЕНАШЕВИЧ, СТЕПОЧКИН СЕРГЕЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06G 7/30

Метки: интерполятор, линейный, цифровой

Опубликовано: 30.03.1978

Код ссылки

<a href="https://patents.su/3-600569-cifrovojj-linejjnyjj-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой линейный интерполятор</a>

Предыдущий патент: Устройство для интегрирования малых токов

Следующий патент: Устройство для моделирования линий с распределенными параметрами

Случайный патент: Резиновая смесь на основе карбоцепного каучука