Процессор управляющей вычислительной машины

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

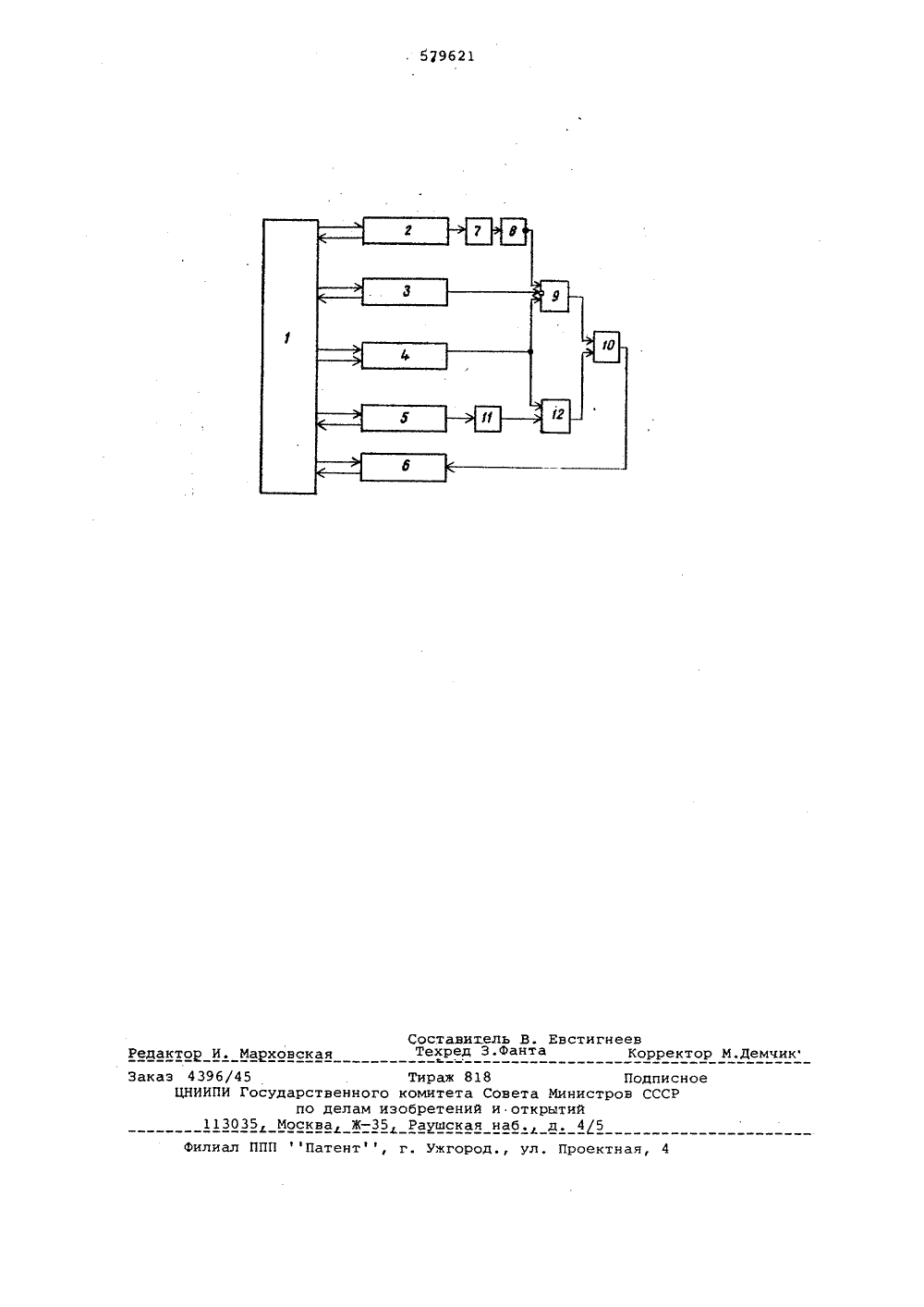

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социапистнческих Республик) Дополнительное к авт. св в 22) Заявлено 17,12,75 (21) 2300408/1с присоединением заявки23) Приоритет е068 1 аврааратваааый аааатвтВвввта Маааатрав 60 СРав ааааа азаврвтааааа атарытаа) Дата опубли ния описания З 01177.Плах оусов, В.Н. Белый, Э.В. Купченко,ый, К.Г. Самофалов и 10,8. Щерб;.н.,Киевский ордена Ленина политехническии институ; м. 50-летия Великой Октябрьской социалистическ.й революцииЧИСЛИтЕЛВНОИ сится к вычисли- ожет быть исполь. х вычислительных Изобретение от тельной технике и зовано в управляю комплексах,5 ят гракза ими остикся 111 г о рнфметико-ларегистр 2 Фор я операцуй Известно устройство защиты па содержащее аридметико-логический блок и регистры для запоминания ничных адресов совокупности ячее памяти, в котором адресная часть проса и памяти сравнивается с эт раничными адресами и, в зависим т результатов сравнения, доступ памяти разрешается или запрещаетОднако в этом устройстве необходимы дополнительные регистры для запоминания граничных адресов памяти.Наиболее близким к изобретению по технической сути является входящий в набор агрегатных модулей АСВТ-М процессор управляющей вычислительной машины М, содержащий регистр фо мйрования фаз выполнения операций,регистр текущего адреса, регистр номера команды, регистр кода операций, устройство защиты памяти, входы-выходы которых подключены к соответствующим выходам-входам арифметико-логического устройства 2. Однако в этом устройстве не осуществляется защита постоянных программ от ошибочного к ним обращения.Целью изобретения является повышение надежности работы процессора.Для этогд в процессор дополнительно введены элементы ИЛИ, два элемента И, элемент НЕ, первый дешифратор и второй дешифратор, вход которопр подключен к выходу регистра кода операций, а выход - к первому входу первого элемента И, второй вход которого подключен к выходу старшего разряда регистра номера команды и к первому входу второго элемента И, второй вход которого соединен с выходом стар шего разряда регистра текущего адреса, а третий - через первый инвертор и первый дешифратор подключен к выходу регистра формирования фаз выполнения операций, выходы первого и второго элементов И подсоединены к входам элемента ИЛИ, выход которого подключе к устройству защиты памяти.На чертеже изображена блок-схема процессора управляющей вычислительной машины.Процессор содержи агическое устройствомирования фаз выполн ирегистр 3 текущего адреса, регистр 4 номера команды, регистр 5 кода операций, устройство б защиты памяти, дешифратор 7, элемент НЕ 8, элемент И 9, элемент ИЛИ 10, дешифратор 11 и элемент И 12.Процессор работает следующим обра.зом.Оперативное запоминающее устройство, с которым процессор обменивается информацией, состоит из двух равных10 областей, Адреса ячеек памяти первой и второй области различаются по значению старшего двоичного разряда номера ячейки. В первой области ОЗУ размещаются постоянные программы, защищаемые от ошибочного к ним обращения. Вторая область ОЗУ отводится для размещения сменных программ. Если процессор выполняет адресную команду, расположенную во второй области оперативного запоминающего устройства и осуществляет ошибочное обращение по адресу к первой области запоминающего устройства, то появляются сигналы на прямом выходе триггера старше го разряда регистра 4 номера команды и на инверсном выходе триггера старшего разряда регистра 3 текущего адреса. Эти сигналы присутствуют на двух входах элемента И 9. 30Если при этом процессор находится не в фазе прерывания,т.е.на выходах регистра 2 формирования фаз выполнения операций и соответственно на входах дешифратора 7 отсутствует комбинация сигналов, соответствующая фазе прерывания, то отсутствует сигнал на выходе дешифратора, и после элемента НЕ 8 присутствует сигнал на третьем входе элемента И 9, Наличие сигналов на всех входах элемента И 9 обуславливает появление сигнала на выходе этого элемента,который через элемент ИЛИ 10 поступает на вход устройства б защиты памяти.В результате устройство б запрещает обращение к первой области памяти, прерывает исполнение текущей сменной программы, содержащей ошибочное обращение, и осуществляет передачу управления команде, записанной в ячейкепамяти с фиксированным адресом, соответствующим причине прерывания.Аналогично осуществляется защита первой области памяти от выполнения некоторых запрещенных безадресных 55команд, содержащихся в сменных программах.К таким командам относятсвкаманды установки и снятия масок,Останов и другие, исполнение которых может нарушить содержимое первой области памяти. При наличии на выходах триггеров регистра 5 кода операции и соответственно на входах дешифратора 11 одного из кодов запрещенной операции на выходе дешифратора 11 появляется сигнал, поступающий на один из входов элемента И 12, Сигнал с прямого выхода триггера старшего разряда регистра номера команды поступает на второй вход элемента И 12, Этот сигнал появляется во всех случаях, когда подлежащая исполнению команда размещена во второй области памяти. Наличие сигналов на двух входах элемента И 12 обуславливает появление сигнала на ее выходе. Этот сигнал через элемент ИЛИ 10 поступает на вход устройства защиты памяти б,Формула изобретенияПроцессор управляющей вычислительной машины, содержащий регистр формирования фаз выполнения операций, регистр текущего адреса, регистр номера команды, регистр кода операций, устройство защиты памяти, входы-выходы которых подключены к соответствующим выход 1 м-входам арифметико-логического устройства, о т л и ч а ющ и й с я тем, что, с целью повышения надежности работы процессора, в него дополнительно введены элемент ИЛИ, два элемента И, элемент НЕ,первый дешифратор и второй дешифратор, вход которого подключен к выходу регистра кода операций, а выход - к первому вход первого элемента И, второй вход которого подключен к выходу старшего разряда регистра номера команды и к первому входу второго элемента И, второй вход которого соединен с выходом старшего разряда регистр 4 текущего адреса, а третий через первый инвертор и первый дешифратор подключен к выходу регистра формирования фаз выполнения операций, выходы первого и второго элементов И подсоединены к входам элемента ИЛИ, выход которого подключен к устройству защиты памяти.Источники информации, принятые во внимание при экспертизе:1. Патент Франции Ф 2027419, кл. 8 06 Е 9/00, 12.12.1969.2, Архитектура М, НИИУВМ, Северодонецк, 1972.579621 Составитель В. ЕвстигнеевРедактор И. Марховская Техред З.фанта Корре 4396/45ЦНИИПИ Госуда За исноеСР 13035 Моск лиал ППП Патентф, г. Ужгород., ул. Проектна Тираж 818 енного комитета С елам изобретений ЖРаушская

СмотретьЗаявка

2300408, 17.12.1975

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

БЕЛОУСОВ КОНСТАНТИН НИКОЛАЕВИЧ, БЕЛЫЙ ВЯЧЕСЛАВ НИКОЛАЕВИЧ, КУПЧЕНКО ЭРИСТ ВАСИЛЬЕВИЧ, ПЛАХОТНЫЙ НИКОЛАЙ ВИКТОРОВИЧ, САМОФАЛОВ КОНСТАНТИН ГРИГОРЬЕВИЧ, ЩЕРБИНА ЮРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: вычислительной, процессор, управляющей

Опубликовано: 05.11.1977

Код ссылки

<a href="https://patents.su/3-579621-processor-upravlyayushhejj-vychislitelnojj-mashiny.html" target="_blank" rel="follow" title="База патентов СССР">Процессор управляющей вычислительной машины</a>

Предыдущий патент: Резервированный генератор

Следующий патент: Цифровое устройство для воспроизведения функции

Случайный патент: Устройство для наложения заготовок боковин на сборочный барабан