Дешифратор параллель-последовательного кода длины с основанием к

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 579609

Автор: Келлер

Текст

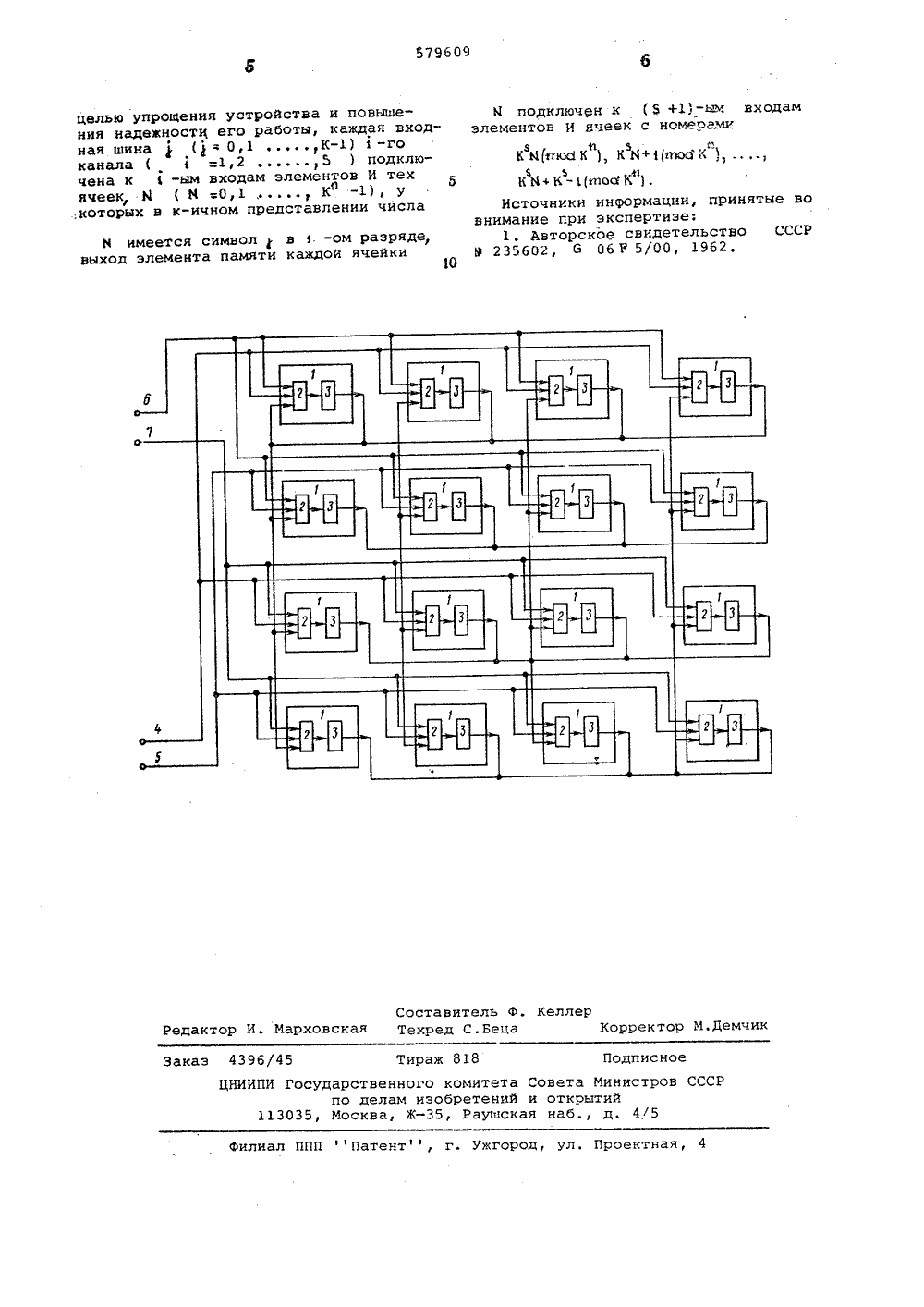

О П И Г-А Н И Е ИЗОБРЕТЕНИЯ Союз Советских Социалистических Республикее 1 деретееееы 1 витетйеэата йиетраз ЗИРае делен азабретеевйе етеряте К( 1=1,2входам элеме0,1представлени1 Ь 1-ом РазРЯдждой ячейкодам элеме ая входная ш) 1 -ГО Канал) подключенИ тех ячееккоторых в К-ила имеется сиход элементаподключенИ ячеек с ном наа 1 И+1(п и УК Фу нтов Н(ххЯ К )5 е и+К - 1 (ОЗ К 1(й= о ора Рас ых рядо в в пор что вчейки с Ячейки дешифра5К горизонталькальных столбцномеров И такрасполагаются олагаются в и К" " верти дке возраста ервом столбц номерами мвол памят к (5 и чи е, ви Й я(61) дополнительное к (Ы) Заявлено 11.12,72 (2 с присоединением заяв (23) ттриоритет - (43) Опубликовано 0111 (45) Дата опубликовани 1Изобретение относится к вычислительной технике.Известен дешифратор параллельно- последовательного кода длины п с осно.раннем К, содержащий 8 входных каналов, каждый из которых содержит К входных шин, регистр сдвига из К ячеек, каждая из которых содержит и следовательно соединенные элемент И и элемент памяти (1) .Однако этот дешифратор является сложным и имеет низкую надежность.Цель изобретения - упрощение устройства и повышение его надежности.Это достигается благодаря повыше нию регулярности структуры. Регулярность структуры и совмещения функций разнотипных узлов отвечают требованиям технологии изготовления больших интегральных схем. 20 К НФо л ), З Н +1(ока К ),К Й+ К - 1 (пихт К" ) . Дешифратор параллельно-последовательного кода длины и с основанием К, передаваейого по 6 параллельным каналам, выполняется на основе регистПра сдвига из К ячеек, каждая из которых содержит последовательно соединенные 5 +1- входовой элемент И и элемент памяти. Каждый из Ь входных кана лов содержит по К ахадных шин, каждая-аи входная шина (1 = 0,1 К) 1 = 1,2 , 8 канала подключена к 1 -ым входам элементов И тех яче ек Ят ( т( =0,1 , К -1), у которых в К-ичном представлении числая имеется символв-ом разряде. Выход элемента памяти каждой ячейки Я подключен к ( ь +1) -ым входам элементов И ячеек с номерамиЙ=0,1 , К,во втором столбцес номерами К, Кф+1. 2 Кз -3 ит.дСхема дешифратора параллельно-последовательного кода при и=4, К : 2,Ь :2 изображена на чертеже.Дешифратор содержит К = 2 = 1 б ячей 4ек 1 регистра сдвига. Каждая ячейкасос"оит из последовательно соединенных трехвходового элемента И 2 и элемента 3 памяти, Каждый из 5 :2 входных каналов содержит по К : 2 входных шин 4, 5 и б, 7. Шины б и 7 - этосоответственно нулевая и единичная шины первого канала, шины 4 и 5 - зтосоответственно нулевая и единичная шины второго канала.Каждая 1 -ая ( = 0,1) входная шина1 -го (1 = 1,2) канала подключена к 1. -ымвходам элементов И тех ячеек, у которых в двоичномпредставлении числа И 20имеется символв ( -ом разряде. По -этому нулевая(:О) шина б первогоканала соединена с первыми входами элементов И ячеек 1 О,1 11 ь 1 в 1 ч1 а(оничная (:1) шина 7 первого канала соединена с первыми входами элементов И ячеек 1, 1 111 щ 1 и м 15нулевая (= 0) шина 4 второго каналасоединена со вторыми входами ячеек1 г 1 1 ь 1 в 1 ю 1 г 14единичная( = 1) шйна 5 второго канала соединена со вторыми входами ячеек 1,1,1 з,1111, 1Выход элемента памяти каждой ячейкиЯ подключен к третьим входам элемен-рМтов И ячеек с номерами1( Н(пад Я") = 4 И(пюа 16)11 И+1(вс( К") х 41(+ 1(иоб 16),б йК К 2(пкс( К ) 41(+2(иихф 161,К И+К(лоб К )" 4 М+Зйпод 1 Ц,Поэтому выходы элементов памятиячеек 1,14,16, 1 ц соединены с третьи- фми входами элементов И ячеек 1,11 г,1, выходы элементов памяти ячеек 11 з 1 д, 1 соединены с третьими входами элементов И ячеек 14 1 з (ь ЬяОвыходы элементов памяти ячеек 1,11 д 14 СОЕДИНЕНЫ С третьими входамиэлементов И ячеек 1 в, 1, 1 о1и,наконец, выходы элементов памяти ячеек 1,1, 4 ц, 1,з соединены с третьими входами элементов И ячеек1 ь 1 ьШины сдвига и установки в начальное состояние на чертеже не показаны.Устройство работает следующим обра 6 О зом.Перед началом работы все элементы памяти ячеек устанавливаются в состояние 1, бб" При приеме символа 0 ф по первоиу каналу на нулевую шину б подается сигнал 1, а при приеме символа 1 по первому каналу на единичную шину 7 сигнал 1. Точно также, при приеме символа Оф по второму каналу на нулевую шину 4 подается сигнал ф 1 ф, а при приеме символа 1 по второму каналу на единичную шину 5 - сигнал 141Рассмотрим пооцесс дешиФрирования коМбинации 0110 ( М :б), передаваемой по двум параллельным каналам ( 1 ц ) . Так как на первом такте символ,0 принимается в первом канале и символ 1 во втором канале, то на нулевую шину 1 и единичную шину 5 подаются сигналы 1, а на единичную шину 7 и нулевую шину 4 - сигналы 0. В результате, после подачи первого сдвигаю- щего импульса (после первого сдвига в регистре) состояние 1 переместится из ячеек 1,11,5 только в ячейки 1 1, 19, 1 ц , так как элементы И только этйх ячеек будут иметь сигналы 1 на всех трех входах.На втором такте символ 1 принимается в первом канале и символ О во втором канале, поэтому сигналы 1 подаются на единичную шину 7 и нулевую шину 4, а сигналы 0 на единичную шину 5 и нулевую шину б. После второго сдвига в регистре состояние 1 переместится из ячеек1 з В единственную ячейку 1 так как элемент И только этой ячейки будет иметь сигналы 1 фф на всех трех входах. Таким образом, ячейка 16 зафиксирует результат дешифрирования комбинации 0110 (Й = б) .Если произойдет отказ ячейки Я типа 10, та дешифратор не сможет дешифрировать только одну комбинацию с номером М . Допустим произошел отказ ячейки 19 . Это никак не повлияет на результат дешифрирования всех комбинаций, кроме 1001 ( М = 9) . Так, например, при приеме той же комбинации 0110 ( К =б) после приема первой пары сиМволов и первого сдвига в состоянии 1 окажутся ячейки 1,1, 1,а после приема второй пары символов и второго сдвига в состоянии 1 окажется только ячейка 1 З, которая и зафиксирует результат дешифрирования.Формула изобретенияДешифратор параллельно-последовательного кода длины и с основанием К, содержащий Ь входных каналов, каждый из которых содержит К входных шин, регистр сдвига из К ячеек, каждая из которых содержит последовательно соединенные элемент И и элемент памяти, о т л и ч а ю щ и й с я тем, что, с79 б 09 Составитель Ф. КеллерРедактор И. Марховская Техред С.Беца Корректор М,Демчик Заказ 439 б/45 Тираж 818 Подписное ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб д. 4/5Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 целью упрощения устройства и повыше" ния надежности его работы, каждая входная шина(0,1 ,К)-го канала ( 1 =1,2 , , Ь ) подключена к-ым входам элементов И тех ячеек, й ( й :0,1 ; К -1) уО 5 ,которых в к-ичном представлении числа М имеется символв 1. -ом разряде,выход элемента памяти каждой ячейки10 М подключен к ( 3 +1) -ым входамэлементов И ячеек с номерамиК М июс( К ), К Н+1 Ффх К ).Ъ ИК ЙК -1(иас( К ) .Источники инФормации, принятые вовнимание при экспертизе:1. Авторское свидетельство СССР9 235 б 02, б Об Р 5/00, 19 б 2,

СмотретьЗаявка

1857604, 11.12.1972

ВЫСШЕЕ ВОЕННОЕ-МОРСКОЕ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ИМ. А. С. ПОПОВА

КЕЛЛЕР ФЕЛИКС ЭДУАРДОВИЧ

МПК / Метки

МПК: G06F 5/00

Метки: дешифратор, длины, кода, основанием, параллель-последовательного

Опубликовано: 05.11.1977

Код ссылки

<a href="https://patents.su/3-579609-deshifrator-parallel-posledovatelnogo-koda-dliny-s-osnovaniem-k.html" target="_blank" rel="follow" title="База патентов СССР">Дешифратор параллель-последовательного кода длины с основанием к</a>

Предыдущий патент: Устройство для ввода информации с перфокарт

Следующий патент: Многофункциональный логический модуль

Случайный патент: Установка для выработки тонкого армянского лаваша