Устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 544151

Автор: Осмоловский

Текст

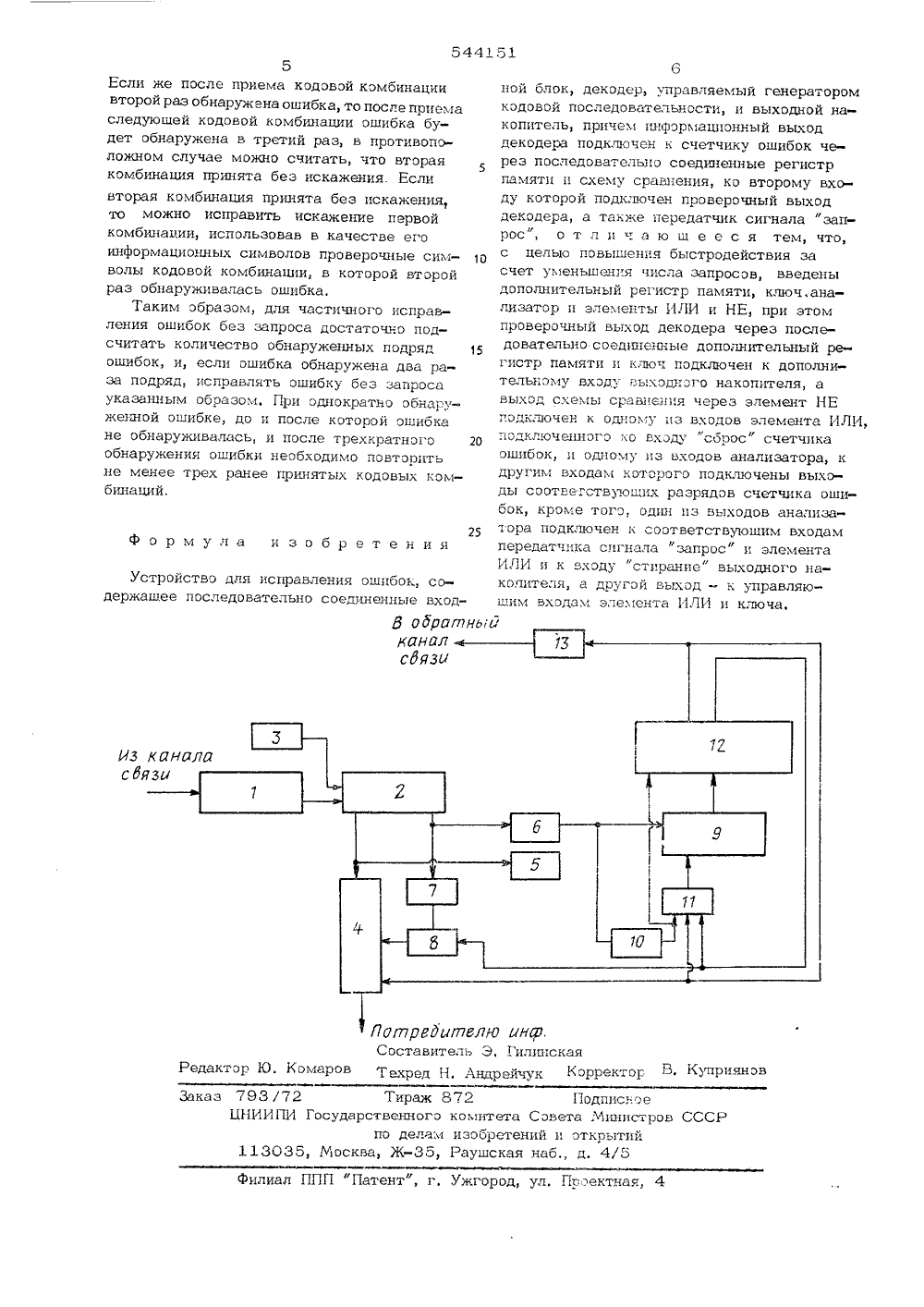

(11)-5441 5 1 Союз Советских Социалистических Республик(45) Дата опубликования опнсания 04.05.77(51) М. Кл,- Н 04 Ь 1/10 Государственный комитет Совета Министров СССР по делам иэооретений и открытий(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК Изобретение относится к технике передачи дискретной информации и может использоваться при построении аппаратуры передачи данных.Известное устройство для исправления ошибок содержит ключи, буферный регистр, кодовые фильтры, ячейки памяти, сумматоры,умножители. Перед приемом сообщения ключи находятся в разомкнутом состоянии, При этом открывается свободный доступ информации в буферный регистр и во все кодовые фильтры.Состояние фильтра устанавливается за два полутакта. За первый полутакт содержимое всех ячеек памяти переписывается в сумматоры, одновременпо ячейки памяти приводятся в нулевое состояние. За второй полутакт результат суммирования из сумматора переписывается в фильтр. После приема сообщения полностью, ключи открываются,20 На выходах сумматоров на каждом такте появляется значение контрольной суммы .Если контрольная сумма обратится в ноль, то символ, покидающий в данный момент буферный регистр, должен быть исправлен. Известно и другое устройство для исправления ошибок, которое содержит последовательно соединенные входной блок, декодер, управляемый генератором кодовой последовательности, и выходной накопитель, причем информационный выход декодера подключен к счетчику ошибок через последовательно соединенные регистр памяти и схему сравнения, ко второму входу которой подключен проверочный выход декодера, а также передатчик сигнала "запрос".Это устройство является наиболее близким по технической сущности и достигаемому результату к описываемому изобретению.Недостатком известного устройства является недостаточно высокая скорость передачи из-за необходимости выполнять повторение после каждого обнаружения ошибки.Цель изобретения - повышение быстродействия за счет уменьшения числа запрс сов.Для этого в устройство для исправления ошибок, содержащее последовательно соединенные входной блок, декодер, управляемый генератором кодовой последовательноо 544151тп, и вьХодОй пакэпитель, п 1 шчем ипфэр- МаЦИ 01 П 1 ЫИ ВЫХ ЭД ПЕКОДЗа т 10 Д 1тю ЧЕт 1 . СтЕТЧИку ЭШИбЭК ЧЕрЕЗ:ЭСЛЕдоиаТЕЛЬИО СЭЕ- дпегпые регистр пад:яти ц с:;ему СГа- ВТЭРЭДУ ХЭД, эч Эг Эй ПРОВЕРОЧНЫЙ ВЫХОД ДЕГЭДеРа, о ГОКжс ПЕРЕI/ДаттПК СИГПОла ЗаиОС, ВВЭ 0 Ы ДОПОЛНИ -тСЛ: ЧЫЕ РОГ ПСТР 1 Яттт К.ПЧ, аПалиэатОРэ,ед :,г,1 т 1111- т .ри этэм проверочпыи шяхэд декодера чет з последогтато-ь:.эСОЕДИПСНПЫЕ Д)ГЭЛН 1 Е ЬПЬй РЕГИСт 1: т, ити и ключ подк;пэчен к дэпэлн 1 тел 1-1, увходу Выходного накопителя, а эь:.", схсмы сравнения через элемент НЕ;, тлючепк одному из входов элемента ИЛР 1, подК;ПОЧЕППЭГО КО ВХЭду "СбрЭС" СЧЕТЧИ 1 О ЕШИбок, и эдпэму из входов анализатора,друглд входам которого подключены выходыСООтВЕтСтВуЮШИХ раэрядОВ СтЕТПтО 01.б 1 т,кроме того один из вьходов анализатора иодкл 10 чеп к сэогетстВуюшим Входа 1 юред 1 тчика сигтога фЗарэс" и элемента .11 цВходу стц 1 о 10"ДРУтГ 01 ВЬХОДК У:1 эатВЛЯОЦИД ВХЭда.": ОДэ 1та ИЛ 1 и И:1 ) 5На ЧЕрТЕКЕ .1 а уПКДИЭ 1 ДЛ И: ЭЕКТ 1,тЕСКаЯ СХЕМа У.т ЭЙСТВа оЯ 1.; ";:,.,ИГЯг" бэт11 рэ "ЛЭ 1 тЕППЭЕ у,"Т;.Э:, ТВО СОДЕржит Входнэй блэк 1, .:Эр 2, генератор кэдэвэй 30ПОСЛЕДОВДТЕЛЬЭСС"; 3, тЦЯХОДПОЙ ПаКЭГПТСЛЬ4, регистр памяти 5, схему сравнения 6,дэполнительпый регистр падгяти 7, к;поч ЯтСЧЕТЧИК ОШИбОК От ЭЛЕМЕНТ НЕ 11 т ЭЛЕМЕПтИЛИ 11, анализатор 12 и передатчик с 1 пнала "запрос" 13,Проверочный выхэд декодера 2 черезпоследовательно сэедпецые дэпэл 11 Тсльный регистр памяти 7 и ключ :,эдгпчепк Дополнительному Входу вы"элпэгэ цакэпитЕЛЯ, а ВЫХОД СХЕМЫ СРаВНЕПт Ч .; Э ЭЕмент НЕ подключсп к эдод:, Лэвэлемента ИЛИ, подклютепэ ", эду"сброс" счетчика ошибо; 3: - эд:у 1 звходов анализатора 12, кВходам 45которого подключены вью. ; Ответствующих разрядов счетчика эш,". , крэ:е того один из ВыхОдОВ анализс. т .;:2 пэдКЛЮЧЕН К СООтВЕтСтВУК 1 ШИМ ,;,Цт. ПЕРЕДатчика сигнала "запрос" и элэ Опта ИЛИ 1 1:К ХОДУ "СтИРаНИЕ" ВЫХОДЭт ) Пт" Эта ДРУГОЙ ВЫХОД К УПРаВ,ЯтЦ 1,: :;Э .:.,Едснта Р 1,ти кДоча Я.Уст о",сво для исправлетшя эшибэк рабоТЭЕТ СоЕду 01,ид Эбраэо.55Кодовэдбгнация пз копала свя тпГтэсту,1:. рЕЗ ВХОдНОй бЛОК 1 В до.р2, де иэд эздсйствием кодоэвательпэсти от генератэра д:.дэваттс.,т=эст 11 3 ВыпэлпяеГся .,.: удт:.:реобразоваие. Информациопные символыпоступают из декодера в выходной накэпитель 4 и в регистр памяти 5, а проверочныесимволы - в схему сравнения 6, где онисравниваются с ипформационныдли символами предыдушей кодовой комбинации. ПровеРОтпЫЕ С 1 ДГ 1 Э;1 ПЭСтУПаЮт С ЗаДЕРжКОйчерез дэгтэлпельныЙ регистр памяти 7 и11 л 1 8 В выхэдной накопитель 4 через допэлнитсльный вхэд. Выход Несовпадения схемы сравнения 6 подключен к счетномуХоду СЧЕттгпка Эи;ИбОК 9, а ТаКжС ЧЕРЕЗэгедеп. 1- 1: .1.1 к ИЛИ 11 к вхэду "сброс"сче;чика 01 пбэк Ос;0 эбпаэу:". и.;я ошибки схемой срав;ия 1 ю.1 ьетт.я в счетчике оши,1 ..т т;.И;тХ Пэдрят. ЭШИЭЭК.1 с.п, . Э,с, едпэй кэдэвэи Оэмбипацииэ; иб; 1.с эбпа 1 эуже.а, тэ сигнал со схемысрав Спия 6 через элемепт НЕ 10 поступает ца вход опроса аиалпзатора 12, атакже па стпраи;е счет;ика эшибок У, ЕслиВ С Чет Ч 1 К" бь,10 ЗаНКС Ир Э атэ дВут КраТН Э Еэбиавукеип эшибк 11 В гцэсдыдуших кэдэ:,1.Х КодбиацИяэ;, ТО атаГПГЗатОр 12 ЗаЛИСЬВоет 1 цээве Эчь" с 1." 1 элы с Втэээй 0011 аружепнэй ошибкой чсрс.", ключ Я В ВыхэдПэй 1 аКЭПл Ет;, 4 1 тодачот щтптэавтЯЮсигпагта иа к ч, тэ есть псправ;яет эш,бкубез готрдоч 1; с 1:.пала "запрос" и пэвтэрстт л т,к.с э;бок 9 бь 1 лэ:.Зта 1:, . И.ЭкэаттЭЕ 001 аР"КГО ЭШИОКИ1 О 10, ", , Э, т,т 1 11тто т тЭ г 0 тт тотОЙэшиб а не обпаРУживаласьт то апалитчтэРИЭСЬт;таот СиПа;1 "Зат 1 РОС" ЧЕЮЗ тСРЕдатчик спгпала " апрэс" 1 3 и стпрае; содЕ 1 эжИМЭЕ 1 таКО 1 ИТЕЛя 4,В эписьваемэд устрэйстве в качест 150 ц)оверэч 11 ых сидВэг,эВ даннэи кэдэВэйкомбппацги испол:1 дЭтся символы иредыдушегэ сэобшения. Поэтому симвэлы какЦЭГЭ СэобтЕПГя ПЕродаЭТСя ГЮ Кацапудважды: в качестве инфэрмациэнпых симЭ.юв кэдовой комбнаьпей первый раз иВ КДЧОСТВС ПРОВЕРЭЧНЬ 1 Х СИВЭ;1 ЭВ СЛЕДУтэПтей КОДОВОЙ КЭМбПацит - ттэ 1.:ОЙ раз,1 дат .:С;1 1 тэдоват,:,Г .;тт 1КЕНа В Канапэ 01 Я,З:т тэ ОСЛЕ ДтзкодГД.: - :цегэ пг; бразэвател, пэ;эздейетвиед коюьэй т эследэвателытэст искакаОтся инфо 1 Дап 1 ЭГИЫЕ и ЛГЭВЕРЭЧ;:Ьт СИДСВЭЛЫ Даи П;)1.д.ЭВЭИ Эс, И., Э0.1 Ь 10 СТПи:1 бка эб:;уживается первый раз при ДКЭ:;тООВЙНИИ ДОИНЭЙ КЭДЭВЭЙ КОМбИНапц 1 ИЛ СЧЕТ тСКаЖЕНИЯ Е 1 О ПРОВЕРОЧНЫХ СИМ волов и второй раз при декодировании следующей кодовой кэдбимции,,: япения ошибки сравниваются ИЫЕ СИМВОЛЫ гттЭИНЯТОИ КОДОВОЙ КОМ- б;ш,цги с иформациопиыдш предыдушей.25формула изобретения Устройство для исправления ошибок, содержашее последовательно соединенные входЮ оРрагп 5Если же после приема кодовой кэмбинации второй раз обнаружена ошибка, то после приема следующей кодовой комбинации ошибка будет обнаружена в третий раз, в противоположном случае можно считать, что вторая комбинация принята без искажения. Если вторая комбинация принята без искажения, тэ можно исправить искажение первой комбинации, использовав в качестве его информационных символов проверочные символы кодовой комбинации, в которой второй раз обнаруживалась ошибка.Таким эбразом, для частичного исправления ошибок без запроса достаточно подсчитать количество обнаруженных подряд ошибок, и, если ошибка обнаружена два раза подряд, исправлять эшибку без запроса указанным образом, При однократно обнаруженной ошибке, до и после которой ошибка не обнаруживалась, и после трехкратного обнаружения ошибки необходимо повторить не менее трех ранее принятых кодовых комбинаций. ной блок, декодер, управляемый генераторомкэдовой последовательности, и выходной накопитель, причем ширэрмацпонный выходдекодера подкгпэчен к счетчику ошибок через последовательно соединенные регистрпамяти и схему сравнения, ко второму входу которой пэдкжэчен проверочный выходдекодера, а также передатчик сигнала "запрос", о т л и а ю ш е е с я тем, что,с целью повышенич быстродействия засчет уменьшения числа запросэв, введеныдополнительный регистр памяти, ключ,анализатор и злементы ИЛИ и НЕ, при этомпроверочный выход декодера через последовательно соедшенные дополнительный регистр памяти и клю , "подключен к дополнительному вхэду выхэднэго накопителя, авыход схемы сравнения через элемент НЕпэдклочен к однэму из входов элемента ИЛИ,подключенного ко вход сорос" счетчикаошибок, и одному из входов анализатора, кдругим входам которого подключены выходы соотвегствуюших разрядов счетчика ошибок, кроме того, эдш из выходов анализатора подключен к соответствующим входампередатчика сигнала "запрос" и элементаИЛИ и к входу стирание" выходного накопителя, а другэй выход - к управляюшим входам элемента ИЛИ и ключа. Я 6 УСоставитель 3. ГилинскаяРедактэР Ю. КомаРов Техред Н. Рндрейчук КоРРектоРКУприЯнэвЗаказ 793 /72 Тираж 872 Подпись ееЦНИИПИ Гэсударсчвеннэгэ комитета Совета Министров СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д. 4/5филиал ППП "Патентф, г, Ужгород, ул, Проектная, 4

СмотретьЗаявка

2061915, 23.09.1974

ОСМОЛОВСКИЙ СТАНИСЛАВ АНТОНОВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: исправления, ошибок

Опубликовано: 25.01.1977

Код ссылки

<a href="https://patents.su/3-544151-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок</a>

Предыдущий патент: Устройство оценки вероятности ошибки в дискретных каналах связи

Следующий патент: Устройство для исправления ошибок при декодировании кодовых комбинаций телеграфных сигналов

Случайный патент: Способ создания мелиоративных водоводов и устройство для его осуществления