Устройство поэлементного фазирования приемников дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 536612

Автор: Попше

Текст

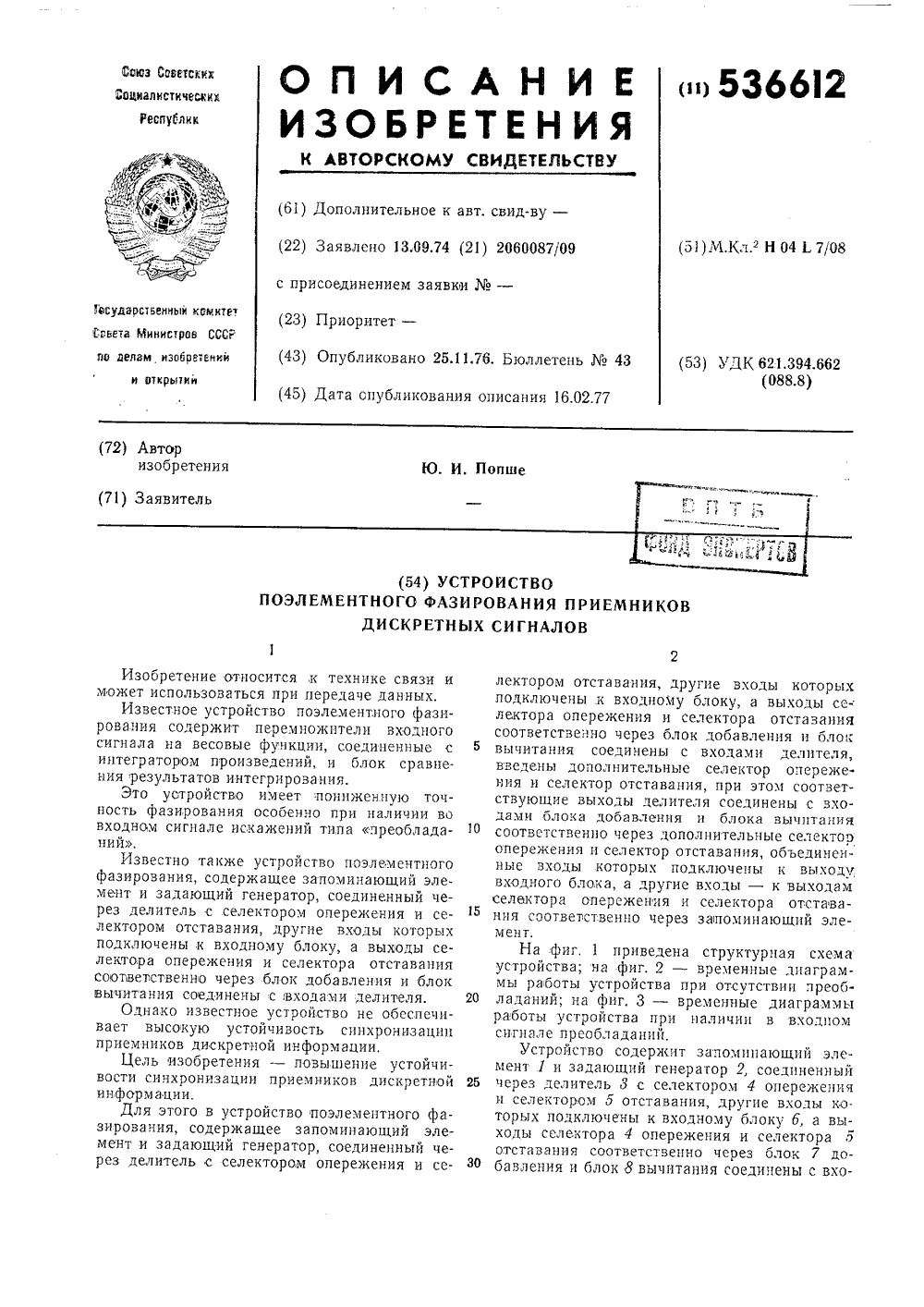

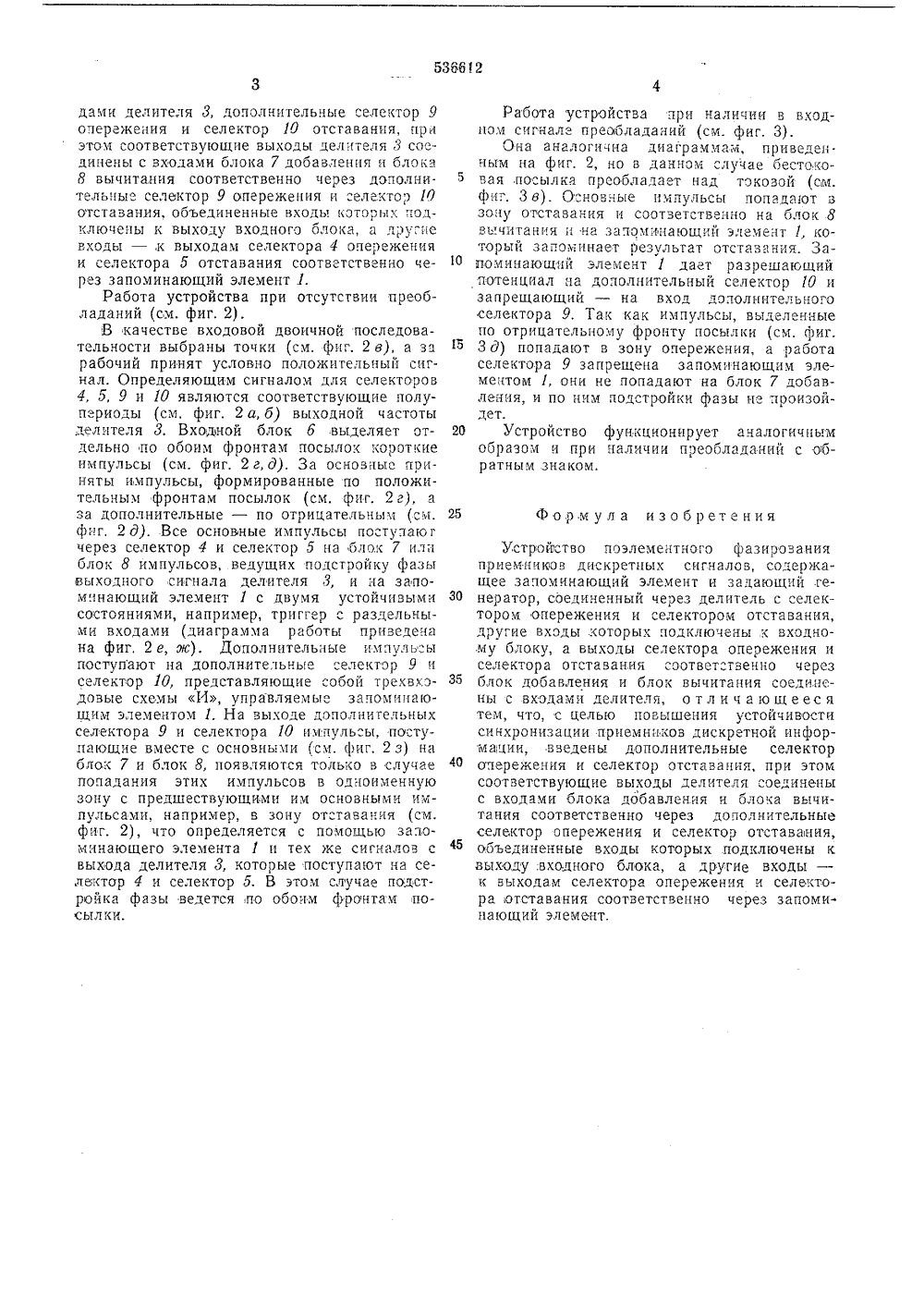

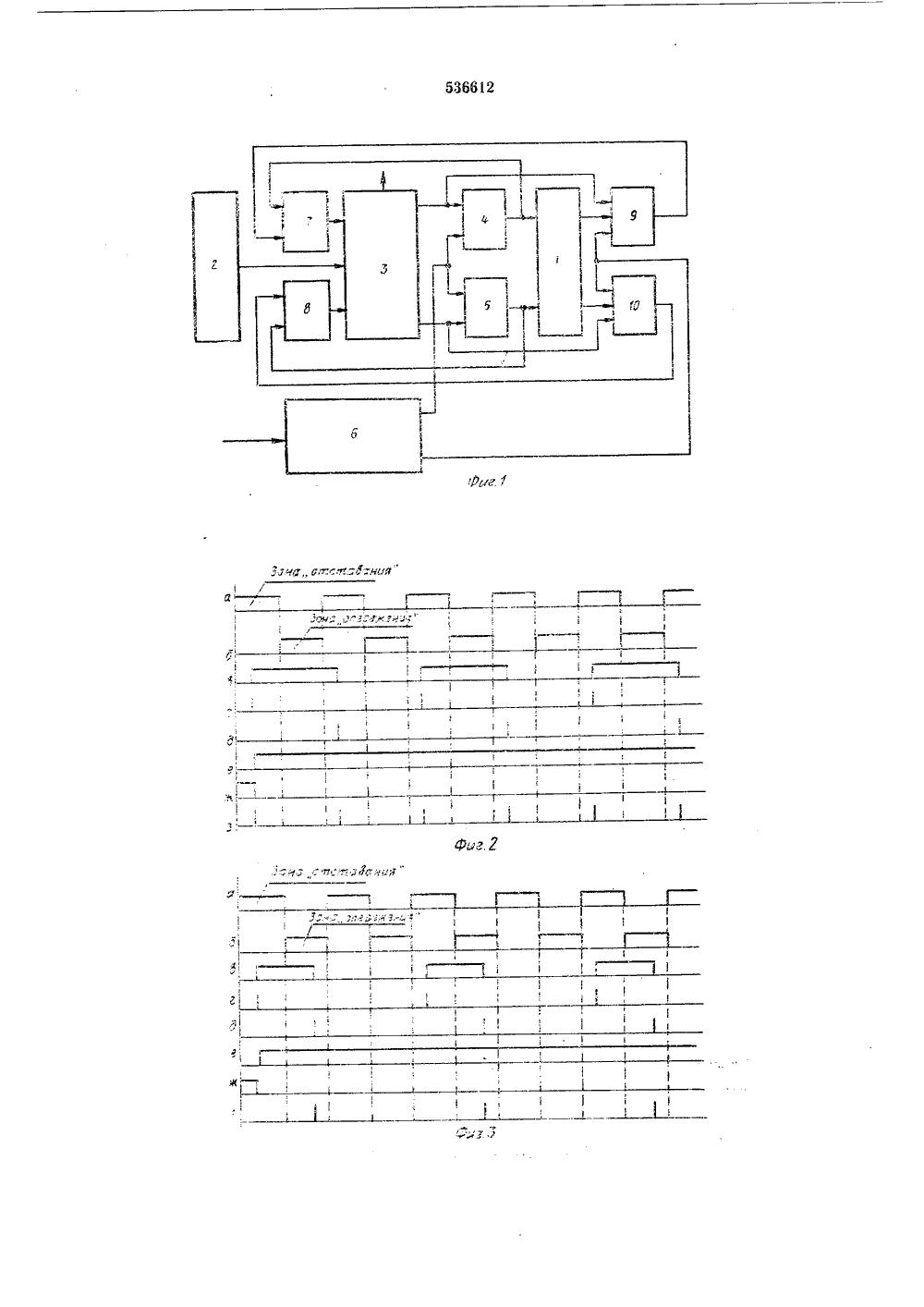

53662 ОПИСАНИЕ ИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(45) Дата опубликования описания 16.02,77(51)Л.Кл. Н 04 1. 7/08 1 асударстеенныи комитетСсеета Чиннстров СССРло делам изобретенийи етирытии(54) УСТРОЙСТВО ПОЭЛЕМЕНТНОГО ФАЗИРОВАНИЯ ПРИЕМНИКОВ ДИСКРЕТНЫХ СИГНАЛОВИзобретение относится,к технике связи и может использоваться при передаче данных.Известное устройство поэлементного фазирования содержит перемножители входного сигнала на весовые функции, соединенные с интегратором произведений, и блок сравне. ния результатов интегрирования.Это устройство имеет пониженную точность фазирования особенно при наличии во входном сигнале исскажений типа преобладаний.Известно также устройство поэлементного фазирования, содержащее запоминающий элемент и задающий генератор, соединенный через делитель с селектором опережения и селектором отставания, другие входы которых подключены к входному блоку, а выходы селектора опережения и селектора отставания соответственно через блок добавления и блок вычитания соединены с входами делителя.Однако известное устройство не обеспечивает высокую устойчивость синхронизации приемников дискретной информации,Цель изобретения - повышение устойчивости синхронизации приемников дискретной информации.Для этого в устройство поэлементного фазирования, содержащее запоминающий элемент и задающий генератор, соединенный через делитель с селектором опережения и селектором отставания, другие входы которыхподключены к входноМу блоку, а выходы селектора опережения и селектора отставаниясоответственно через блок добавления и блок5 вычитания соединены с входами делителя,введены дополнительные селектор опережения и селектор отставания, при этом соответствующие выходы делителя соединены с входами блока добавления и блока вычитаниясоответственно через дополнительные селекторопережения и селектор отставания, объединенные входы которых подключены к выходувходного блока, а другие входы - к выходамселектора опережения и селектора отставания соответственно через запоминающий элемент.На фиг. 1 приведена структурная схемаустройства; на фиг. 2 - временные диаграммы работы устройства при отсутствии преоб 20 ладаний; на фиг. 3 - временные диаграммыработы устройства при наличии в входномсигнале преобладаний,Устройство содержит запоминающий элемент 1 и задающий генератор 2, соединенный25 через делитель 3 с селектором 4 опереженияи селектором 5 отставания, другие входы которых подключены к входному блоку 6, а выходы селектора 4 опережения и селектора эотставания соответственно через блок 7 добавления и блок 8 вычитания соединены с вхо25 зо З 5 40 45 дами делителя 3, дополнительные селектор 9 опережения и селектор 10 отставания, прл этом соответствующие выходы делителя 3 соединены с входами блока 7 добавления и блока 8 вычитания соответственно через дополни. тельныг селектор 9 опережения и селектор 10 отставания, ооъединенные входы которых подключены к выходу входного олока, а друг е входы - ,к выходам селектора 4 опережения и селектора 5 отставания соотвгтствгнно через запоминающий элемент 1.Работа устройства при отсутствии преобладаний (см. фиг. 2).В качестве входовой двоичной последовательности выбраны точкл (см, фнг. 2 в), а за рабочий принят условно положительный сигнал. Определяющим сигналом для селекторов 4, 5, 9 и 10 являются соответствующие полупгриоды (см. фиг. 2 а, б) выходной частоты делителя 3. Входной блок б выделяет отдельно по обоим фронтам посылок короткие импульсы (см. фиг. 2 г, д). За основные приняты импульсы, формированные по положительным фронтам посылок (см. фиг, 2 г), а за дополнительные - по отрицательным (см. фнг, 2 д). Все основные импульсы поступают через селектор 4 и селектор 5 на блок 7 илн блок 8 импульсов, ведущих подстройку фазы выходного сигнала делителя 3, и на запоминающий элемент 1 с двумя устойчивымл состояниями, например, триггер с раздельными входами (диаграмма работы приведена на фиг. 2 е, ж). Дополнительные нмпуль ы поступают на дополнительные селектор 9 и селектор 10, представляющие собой трехвхздовые схемы И, управляемыг запоминающим элементом 1. На выходе дополнитечьных селектора 9 и селектора 10 импульсы, поступающле вместе с основными (см. фиг. 2 з) на блох 7 и блок 8, появляются тольхо в случае попадания этих импульсов в одноименную зону с предшествующими им основными импульсами, например, в зону отставания (см. фиг. 2), что определяется с помощью заломлнающего элемента 1 и тех же сигналов с выхода делителя 3, которые поступают на селектор 4 и селектор 5. В этом случае подстройка фазы ведется,по обоим фронтам посылкии. Работа устройства при наличии в входном сигнале преобладаний (см. фиг. 3).Она аналогична диаграммам, приведен. ным на фиг. 2, но в данном случае бестокозая посылка преобладает над токовой (см. фиг. Зв). Основные импульсы попадают в зону отставания и соотзетственно на блок 8 вь.чигания н на запоминающий элемент 1, которыи запоминает результат отставания.,запоминающий элемент 1 дает разрешающий потенциал ча дополнительный селектор 10 и запрещающий - на вход дополнительного селектора 9. Так как импульсы, выделенные по отрицательному фронту посылки (см. фиг. Зд) попадают в зону опережения, а работа селектора 9 запрещена запоминающим элементом 1, они не попадают на блок 7 добавления, и по ним подстройки фазы нг произойдет. Устройство функционирует аналогичным образом и при наличии преобладаний с обратным знаком. Формула изобретения Устройство поэлементного фазирозания приемников дискретных сигналов, содержащее запоминающий элемент и задающий генератор, соединенный через делитель с селектором опережения н селектором отставания, другие входы хоторых подключены х входному блоку, а выходы селектора опережения и селектора отставания соответственно через блок дооавления и блок вычитания соединены с входамл делителя, о т л и ч а ю щ е ес я тем, что, с целью повышения устойчивости синхронизации прнемнихов дискретной информации, введены дополнительные селектор опережения и селектор отставания, при этом соответствующие выходы делителя соединены с входами блока добавления и олока вычитания соответственно через дополнительные селектор опережения и селектор отставания, ооъединенные входы которых подключены к выходу входного блока, а другие входы - и выходам селектора опережения и селектора отставания соответственно через запоминающий элемент.

СмотретьЗаявка

2060087, 13.09.1974

ПРЕДПРИЯТИЕ ПЯ А-1221

ПОПШЕ ЮОН ИОНАШЕВИЧ

МПК / Метки

МПК: H04L 7/08

Метки: дискретных, поэлементного, приемников, сигналов, фазирования

Опубликовано: 25.11.1976

Код ссылки

<a href="https://patents.su/3-536612-ustrojjstvo-poehlementnogo-fazirovaniya-priemnikov-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство поэлементного фазирования приемников дискретных сигналов</a>

Предыдущий патент: Устройство синхронизации сигналов

Следующий патент: Способ измерения модуля величины искажений типа преобладания телеграфных сигналов

Случайный патент: Способ работы энергетической установки