Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

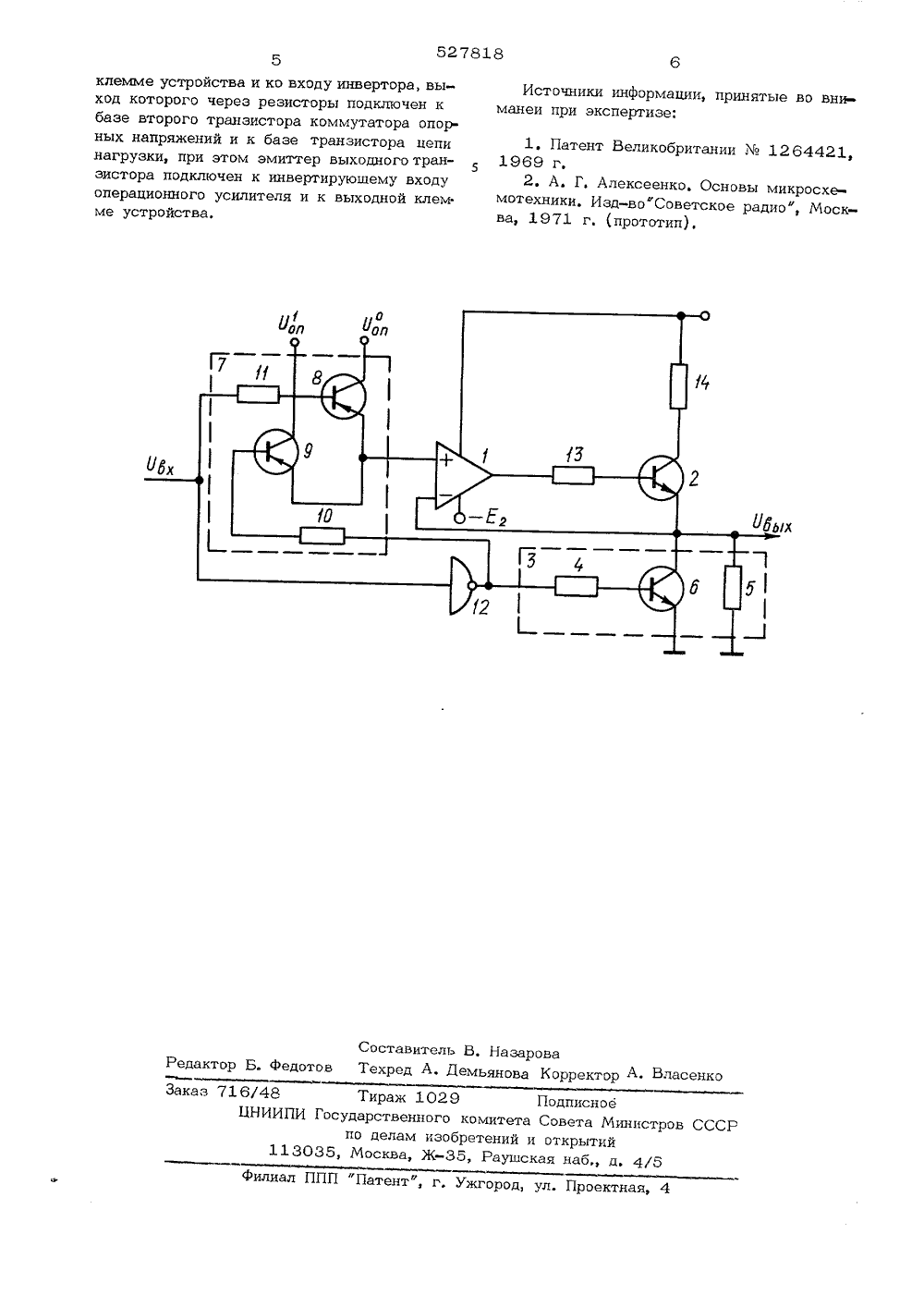

СВИДБТБПЬС 7 В 1,б 1) Дополнительное к (22) Заявлено 04.05.75 вид-ву 21)21 32312/ 1) М, Кл, Н 03 К 5(15с присоединением ваяв(23) Приоритет(43) Опубликэвано 05,0 чванв 11 инте1 ветейв СССчзи 1 етевчй Гасу,аййвтв бййетй Мв ев деяйв эз) У 1% 621.373.4.76, Бюл тень и вткей тви Дата опубликования описа 9. 05. 77 в. туляков, В, О. Плэкс, К, В. Зейля, Ви О, Ф, Суббэта Субботин(7;, 3 аявитель 1:;) фОтз;,л 1,1 РОВатРГ 11- ЦП 7"ТИСО К КОНТРОЛЬНОЛЗщф ет, в частностинк. ионально-стати И.зэбретен 11 е Относитсямер 1 лте;.ьнэй технике, можбыть использовано при фу ищФ чэскэм контроле цифровых интегральных1 ри кэитрэле параметров интегральных схем, лэгическллх узлов, иэстрэеннь 1 Х на их базс. Важ 11 ей 11.ей задачей является подача ;1 а их Вхэдь 1 .,аданных уровней сигналовп ь 1 единица, 1 ри этом ОсэОенностью К-.-, тэ-,1;с 1 гР; л 1 с; 1 а Ьй К ОТ ИЭИН;1 ка Вхэц 1.ых с 1:налэвесли входной сигнал раВен логической единице, и бэлынэй тэк втекаюший в источник входных сигналов, Осли Вх днэй сигнал равец 1 логическом" н= и 10 атель имиуль 1 й или диффер обратной связ ов сэевнин -и,И С ВЫХО- еГО ИНВЕРнапря, ШЕМУ ВХСЭГО) УСИ 1 лителя на ЭЫХ ВХОДНО неинвертируюифференциаль ЦИОННОГ точности повторяется на егэ вь ХОДЕ ХзВесте 11 фОРмиРОВдерлка 1111 лй одоргциэн 11 ьный усилитель, цепьда Операционного утируюший Вход, в кэтжение, пэдвэдимэе к В этой схеме Выходной сигнал, равныйвходному, появляется на нагрузке, когдавключается цепь обратной связи, для чегосхема содержит ключевой элемент на униполярном или биполярном транзисторе.Однако .акая схема расходует большуюмощность источн 11 кэв питания при выходномнапряжении, равном логической единице.Наиболее близок к предлагаемому фор 1 и мирователь импульсов, содержащий операционный усилитель с двумя Входами, к Выдьходу которого подключен выходной транзистор, цепь нагрузки из параллельно соединенных транзистора резистора один из вывоц дэв которой подключен к эмиттеру выходного транзистора, коммутатор опорных напряжений, содержащий два транзистора,эмиттеры которых подключены к неинвертирующему Входу операционного усилителя,2 О инвертор, входную и выходную клеммы 2,Однако такой формирователь импульсовне Обеспечивает достаточной точности уровней логических сигналов,Цель изобретения - повышение точности25 формирования логических уровней импульсов,Предлагаемый формирователь импульсов отличается тем, что база одного из транзисторов коммутатора опорных напряжений через резистор подключена ко входной клемме устройства и ко входу инвертора, выход которого через резисторы подключен к базевторого транзистора коммутатора опорныхнапряжений и к базе транзистора цепи нагрузки; при этом эмиттер выходного транзистора подключен к инвертирующему входу операционного усилителя и к выходной клеммеустройства,Схема формирователя импульсов приведена на чертеже.формирователь импульсов состоит из опе рационного усилителя 1, выходного транзистора 2, цепи нагрузки 3, состоящей из разисторов 4,5 и транзистора 6, коммутатораопорных напряжений 7, содержащего транзисторы 8, 9 и резисторы 10, 11, инвертора 12, резисторов 13 и 14,Работает формирователь импульсов следую.щим образом. Если на входе формирователяустановлен уровень фнульф с коммутатораопорных напряжений 7 на неинвертирующий вход 25операционного усилителя 1 поступает напряожение низкого уровня - УопРоль коммутатора опорных напряжений 7играют ключи на транзисторах 8 и 9 в инверсном включении, Опорные напряжения, З 0определяющие верхний и нижний уровни логических сигналов на выходе формирователя,подключены к коллекторам соответствующихтранзисторов, эмиттерные выводы которыхобъединены и соединены с неинвертирующимвходом операционного усилителя 1. Резисторы 10 и 11 определяют базовые токи открытых транзисторов 8 и 9. Если на входеформирователя имеется сигнал "нуль", открывается транзистор 8 а транзистор 9 40закрывается сигналом "единица" с инвертоара 12. В этом случае напряжение БОппередается на операционный усилитель 1практически без потерь, так как с 1 ( 1 мВкзДля надежного запирания транзистора 9 45уровень фединица" на выходе инвертора 12должен превышать Б и . Одновременновходной сигнал фнульф поступая в цепь нагрузки 3, включает ее, в результате чегорезко уменьшается сопротивление нагрузки,Выходное напряжение формирователя в точоности повторяет напряжение Оподопключенное ко второму входу коммутатораопорных напряжений 7.Диапазон токов нагрузки (входные токиинтегральных схем при уровне "нуль" наих входах), протекающих через цепь нагруэ.ки 3, определяется ее динамическим сопротивлением, а максимальный ток нагрузкиограничивается такими параметрами выход ного транзисотра 2, как максимальный коллекторный ток и рассеиваемая мощность,Если на входе формирователя установленуровень "единицами с коммутатора опорныхнапряжений на инвертируюший вход операционного усилителя 1 поступает напряжениеопПри установке на входе формирователясигнала "единицами открыт транзистор 9, атранзистор 8 закрыт, На операционный усилитель 1 поступает напряжение Укоопторое устанавливается на выходе формирователя импульсов, Одновременно сигналфединица" воздействуя через инвертор 12на вход цепи нагрузки 3, закрывает транзистор 6, и сопротивление нагрузки определяется в этом случае большим сопротивлением резистора 5 и входными токами утечки проверяемых интегральных схем. Потребляемая мощность формирователя импульсовпри формировании выходного сигнала "единица" резко уменьшается. Резистор 13, включенный между выходом операционного усилителя 1 и базой транзистора 2, предназначен для ограничения выходного тока операционного усилителя при замыкании выходаформирователя на корпус. Резистор 14 служит для облегчения режима, транзистора 2в том случае, когда на выходе формирователя устанавливается уровень "нуль" (при этомтранзистор 2 открыт), а количество нагрузок мало. В этом случае большая часть мощности источника питания гасится на резисторе 14.Таким образом, такое схемное решениеформирователя импульсов позволяет значительно сократить потребляемую мощность,атакже повысить точность формирования любых значений логических уровней нуля иединицы,формула изобретенияформирователь импульсов, содержащий операционный усилитель с двумя входами, к выходу которого подключен выходной транзистор, цепь нагрузки из параллельно соединенных транзистора и резистора, один из выводов которой подключен к эмиттеру выходного транзистора, коммутатор опорных напряжений, содержащий два транзистора, эмиттеры которых подключены к неинвертирующему входу операционного усилителя, инвертор, входную и выходную клеммы, о тл и ч а ю щ и й с я тем, что, с целью повышения точности формирования логических уровней импульсов, база одного из транзисторов коммутатора опорных напряжений через резистор подкл.очена ко входной527818 Составитель В. НазароваРедактор Б. Федотов Техред А, Демьянова Корректор А. Власенко Заказ 716/48 Тираж 1029 Подписное БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская набд. 4/5Филиал ППП "Патентф, г, Ужгород, ул. Проектная, 4 клемме устройства и ко входу инвертора, выход которого через резисторы подключен кбазе второго транзистора коммутатора опорных напряжений и к базе транзистора цепинагрузки, при этом эмиттер выходного транзистора подключен к инвертируюшему входуоперационного усилителя и к выходной клем.ме устройства. Источники информации, принятые во вниманеи при экспертизе: 1. Патент Великобритании Мо 1264421, 1969 г.2, А, Г, Алексеенко, Основы микросхемотехники, Изд-во "Советское радио", Москва, 1971 г. (прототип).

СмотретьЗаявка

2132312, 04.05.1975

ПРЕДПРИЯТИЕ ПЯ М-5046, ИНСТИТУТ ЭЛЕКТРОНИКИ И ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ АН ЛАТВИЙСКОЙ ССР

ЖУЛЯКОВ ВИКТОР КУЗЬМИЧ, ПЛОКС ВАЛЕНТИН ОСКАРОВИЧ, ЗЕЙЛЯ КАРЛ ВЛАДИМИРОВИЧ, СУББОТИН ВИКТОР НИКОЛАЕВИЧ, СУББОТА ОЛЕГ ФЕДОРОВИЧ

МПК / Метки

МПК: H03K 5/156

Метки: импульсов, формирователь

Опубликовано: 05.09.1976

Код ссылки

<a href="https://patents.su/3-527818-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Формирователь импульсов малой длительности по переднему и заднему фронту входного импульса

Следующий патент: Пороговое устройство

Случайный патент: Устройство для термической перфорации