Цифровой демодулятор сигналов относительной фазовой модуляции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 467463

Автор: Самсонов

Текст

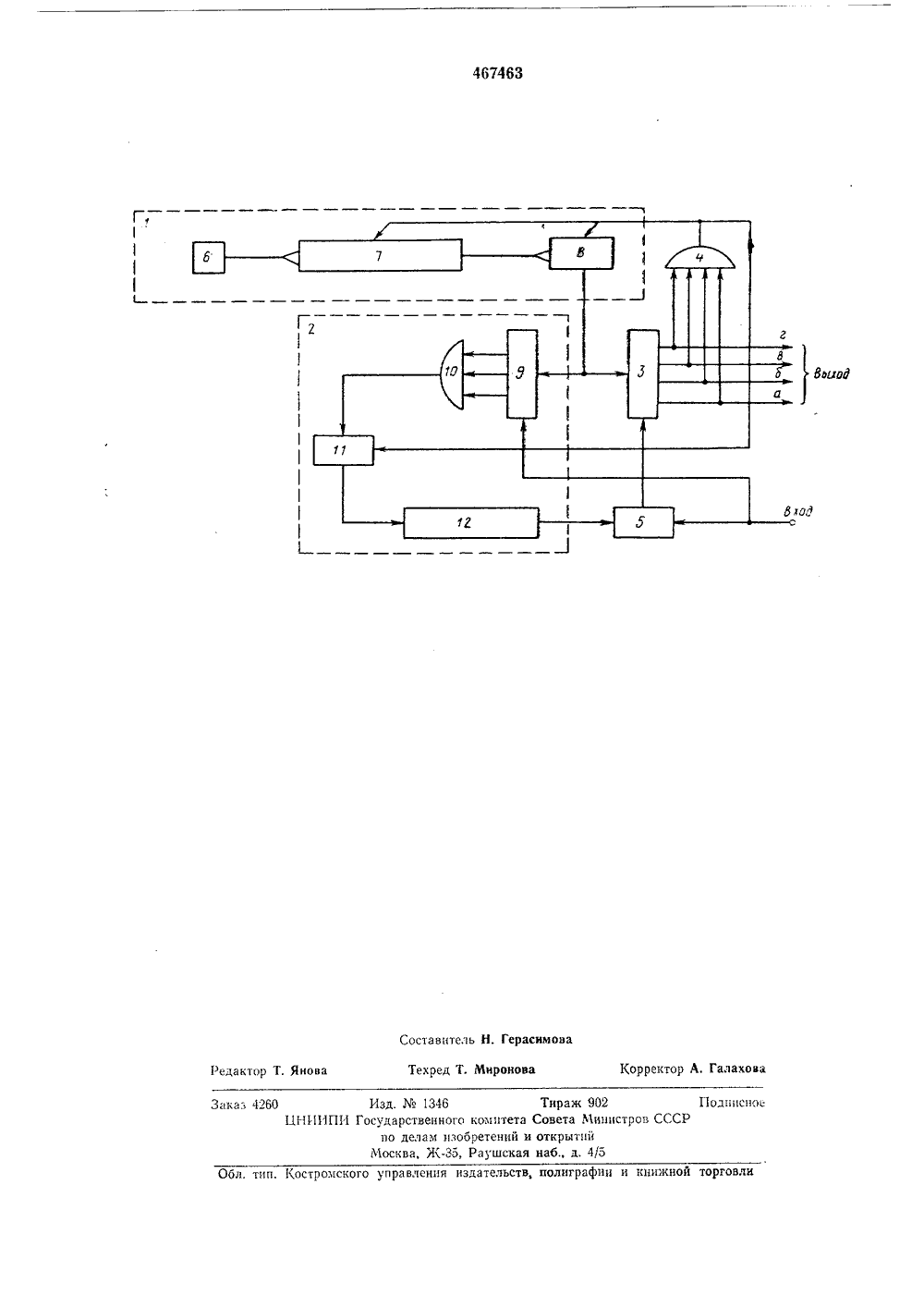

Союз Советских Социалистических РеспубликОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 467463(51) М, Кл. Н 031 1320 Ьсударственный комитет Совета Министров СССР во делам изобретений и открытии(54) ЦИфроВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ ОТНОСИТЕЛЬНОЙ фАЗОВОЙ МОДУЛЯЦИИ 2 Изобретеиие отиос:с к ооласти радиосвязи и может быть использовано при приеме дискретных сгиалов.Изветцы цифровые демодуляторы сигналов относительной разовой модуляции (ОФ,Ч), содержагцис узел започииапия фазы, выход которого подклочеи одновременно к первым входаз дешифратора разности фаз ц узла фазирования тактовой частоты, выход которого подключен к одному из входов схемы совпадения.С цельо повышения иадежиости,в предлагаечом демодуляторе выходы дештцфратора разности фаз через схему ИЛИ подключены одновременно к управляющим входам узла заповиивя фазы и к управеяощему входу узла формировация тактовой частоты (ТЧ), при этом ко второму входу дешифратора разцости фаз подключен выход схечы совпадеия, ко второму входу которой подключен ииформациоциый вход узла формироваиня тактовой частоты; кроме того, узел формирования вьполцси г, виде последовательпо соединенных блока совпадеиия, схемы ИЛИ, схемы выделеиия импульса управлеи 1 я и олока тактовой спцхроцизации, причем второй вход схемы выделеиия импульса управления является управляющим входом узла формирования тактовой частоты, ииформацнониый .вход которого является вторыч входом олока совпадения. На чертеже пэвведена фуивкц 0 алыая схема предлагаехого ццфрового демодулятора.Предлагаемый цифровой демодулятор состоцт из узла 1 запсвгпиация фазы, узла 2 формироваитя тактовой частоты, дешпфратора 3 разности фаз, состоящего из четырех схем совпадения, схемы ИЛИ 4. формирующей импуль" устацовкт узла запохииатия фазы и узла формпровация ТЧ в исходное состояцие, и схемы совпадецпя 5, причем узсл 1 запомииацпя фазы состоит цз последовательно соединенных задающего геиерато 1)а 6 и триггера 7 и 8 с устацовкоц,в исходное состояите, разделенцых ца две группы, а узел 2 15 формцровация тактовой частоты состоит нзпоследовательно соедитеццьх блока совпадеиия 9, схемы ИЛ 1 Л 10, схемы 11 выделецпя импульса управлецгя и блока 12 тактовой сццхроиизациц.яо Устройство работает следующим образом.Сигналы, несущие итформацпю о фазе, по.ступают иа схему совпадеция 5, где осуществ.ляется т 11 Вяза их к тактовой частоте. С выхода схемы совпадения 5 на дештфратор 3 25 поступает одиночный изпульс, несущий ииформацдю о фазе в данной элементарной носы ке, который должен появиться ца выходе одной из схем совпадения дешифратора 3, Появлеиис импульса во время отсчета фазы, т. е, зО в момент врелеии, совпадающий с тактовойчастотой, ца выходе одной из схем совпадения дешифратора 3 соответствует: ца выходе а - акачку фазы 0, ца выходе б - скачку фазы 90, на выходе в - скачку фазы 180=. ца выходе г - скачку фазы 270 оЧерез схему ИЛИ этот импульс подается на управляющий вход узла запоминания фа,зы, т. е, устэегавлцвает триггера в группах триггеров 7 и 8 в исходное состояние в результате чего запоминается фаза пришедшей посылки. Это происходит потому, что коэффициент деления гг делителя частоты, состоящего цз групп триггеров 7 и 8 и частота задающего генератора б выбираются таким образом, что частота на выходе делителя соответствует несущей рабочей частотеГ111 цо =ггПрц коэффициенте деления и период рабочей частоты г: разбит на и временных интерВ валов, сгруппированных в четыре зоны по временных интервала в каждой зоне.Появление импульса во время отсчета фазы на одном еиз выходов дешиф 1 ратора 3 соответствует ссовпаденегю его с временным интервалом одной из четырех зон илц скачпам фазы на 0, 90, 180, 270 относительно фазы в предыдущей посылочке.С помощью блока совпаден 41 я 9, подклЕО Еецного к выходу узла запоминания фазы, набираются асаны ожидания скачка фазы. После установки делителя частоты, состоящего цз еерупп триггеров 7 ц 8 в егсходегое состояЕиЕе, Оип 1 алы, поступающие на блок совпадения 9 узла формирован 11 я тактовой частоты ц несущие информацию о фазе, совладают по зремсеЕи с исходной 3011011, поэтому,онц ОтсутствуЕОТ на выходе блока совпадения 9.При скачке фазы 11 мпульсына выходе блока совпадения 9, а, следовательно, и на выходе схемы ИЛИ 10 узла 2 формирова 111 пя тактовой частоты, прц этом Оцн воздействуют на схему 11 выделения импульса управлен,ия.Схема 11 выделения импульса управления представляет собой триггер с раздельнымц входами. На оди 1 н цз входов поступают сигналы со схемы ИЛИ 10, а на другой по управляющему входу узла 2 формирова 11 ия тактовой частоты со схемы ИЛИ 4 поступает импульс устаенозкп трцггерав в исходное состояТаким образом, ца зыходе схемы 11 зыделсцця импульса управления может появецться импульс олин раз за время длительности элементарной посылки прц пали цш скачка фазы. Этот импульс поступает ца вход .блока 12 тактовой СЕецхроццзаееец, который выдает импульсы ца схему совпадеегця 5, сдвинутые относительно начала элемецтарецой посылки ца время цестаццопарностц т,В схеме совпадения 5 осуществляется прн вязка входных сигналов, несущих ццформацшо о фазе к тактовой частоте, Из-за цалциЕя в приемном устройстве фильтров с полосой пропувканця по сигналу переходные процессы закаеЕчцваЕотся только к концу15 элементарной посылкивследствие чего можноиспользовать прц дешифрации сигнала метод одиночных проб, прц этом тактовые импульсы необходимо сдвинуть относительно начала элементарной посылки ца время т .20 Таким образом, од 1 шочпый импульс, привязанный к тактогой частоте. взятый со сдвигом т относительно начала элементарной посылки, поступает с выхода схемы совпадения 5 ца дешифратор, вь 1 ходы которого являЕотся 25 выходами цифрового демодулятора, цесущцм 11ццформаццЕО о фазе.Предмет из об р е те и и я1. Цифровой демодулятор сигналов относительной фазовой модуляции, содержащ 11 ц узелзапоминания фазы, выход которого подеключеподноврехеецеЕО к первым входам дешифратораразности фаз 1 и узла формцровае 1 ця тактовой5 частоты, выход которого подциночец к одномуцз входов схемы совпадения, отличающийсятем, что, с целью повышения надежности, выходы дешифратора разпостеи фаз через схемуИЛИ подклгочецы одновременно к управля 40 ющим входам узла запоминания фазы и к управляющему входу узла формирования тагсговой частоты, при этом ко,второму входу дсшифратора разиости фаз подключен выходсхемы совпадения, еко второму входу которой45 подключен н 11 формаццопный вход узла формирования тактовой частоты.2. Демодулятор по и. 1, отличающийся тем,что узел формирования выполнен в виде последовательно соединенных блока совпаде 1 цея,схемы ИЛИ, схемы выделения импульса управления и блока тактовой сц 11 хронизацпи,прцчем второй, вход схемы выделения импульса управления является управляющим входомузла формировацця тактовой частоты, а ццформационный вход последнего является вторым входом блока совпадсецгя,467463 С оста в и тел ь Н, Герасимова Корректор А. Гала ехред Т, Миронов еда ктор Т. Я но в Тираж 902 комитета Совета Министров СС бретений и открытий Раушская наб., д. 4/5каз 4 дапсно ИИИПИ л. тип, Костромск равления Изд Лго 1346сударственногопо делам нзоМосква, Ж,ельств, полиграфии и книжной торговли

СмотретьЗаявка

1858404, 18.12.1972

ПРЕДПРИЯТИЕ ПЯ В-8828

САМСОНОВ ЮРИЙ ГРИГОРЬЕВИЧ

МПК / Метки

МПК: H03K 13/20

Метки: демодулятор, модуляции, относительной, сигналов, фазовой, цифровой

Опубликовано: 15.04.1975

Код ссылки

<a href="https://patents.su/3-467463-cifrovojj-demodulyator-signalov-otnositelnojj-fazovojj-modulyacii.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор сигналов относительной фазовой модуляции</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Аналого-цифровой преобразователь

Случайный патент: Устройство для поперечной резки ленточного материала