Генератор -фазных синусоидальных кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

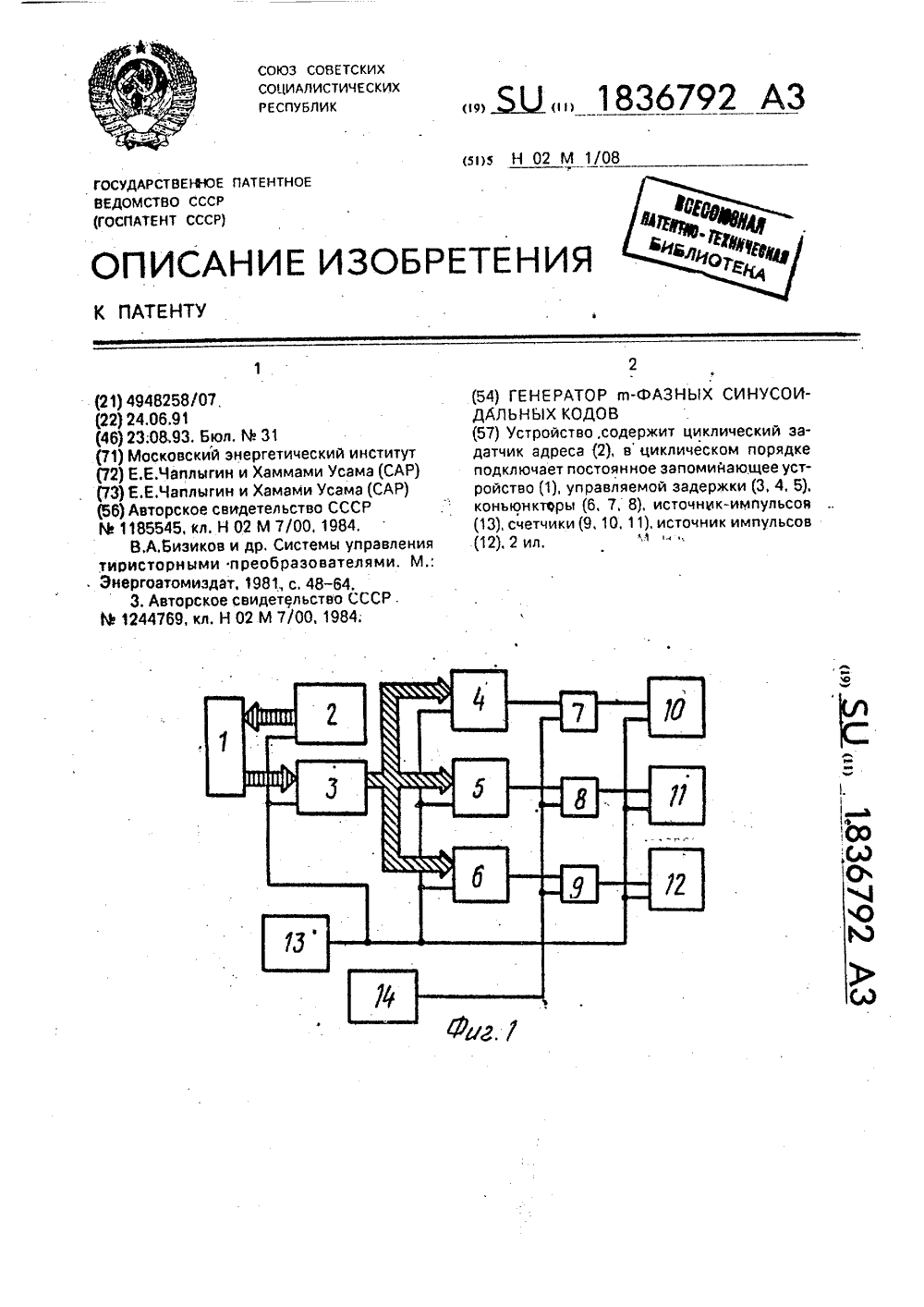

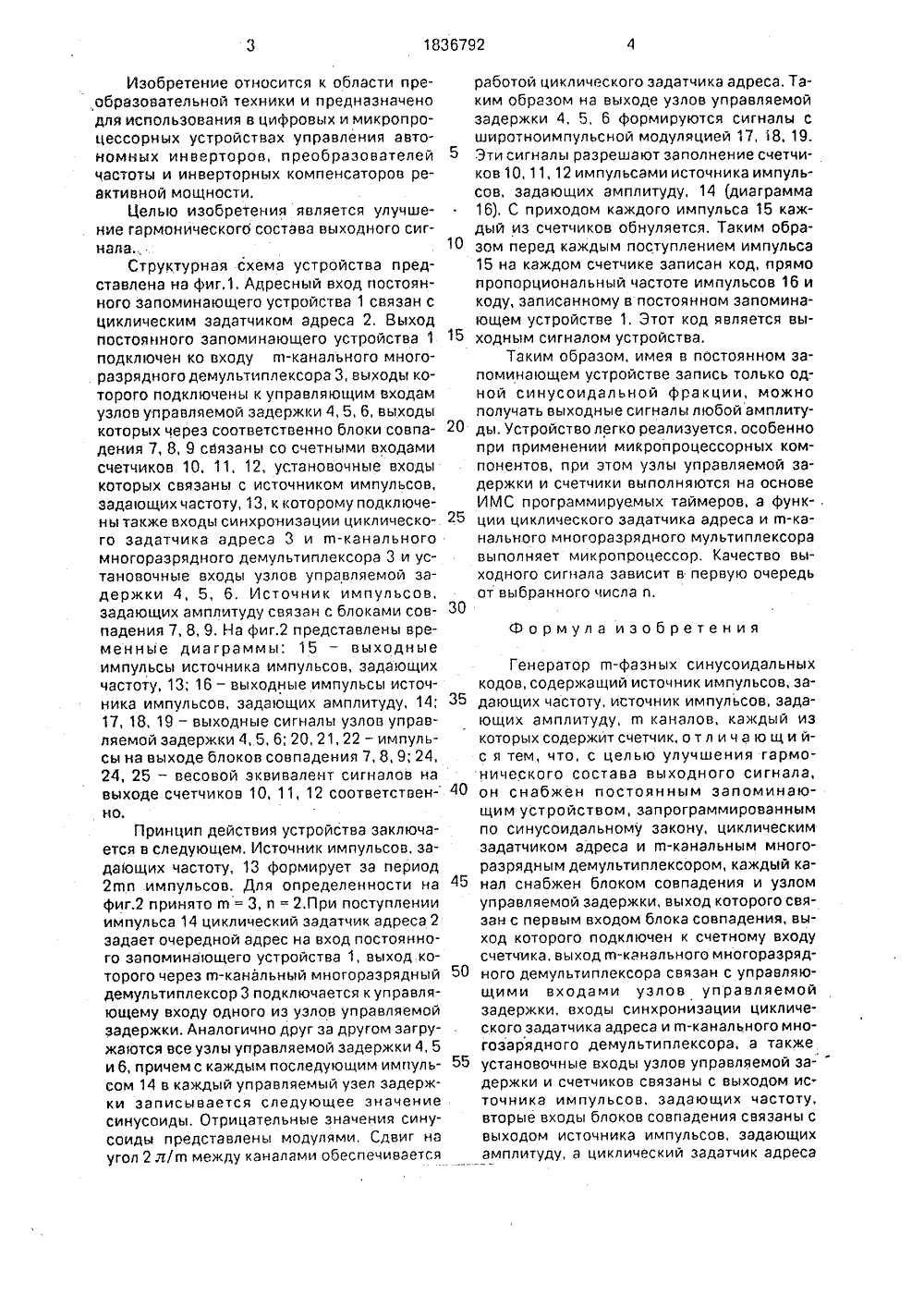

(54) ГЕНЕРАТОР (и-ФАЗНЫХ СИН ДАЛЬНЫХ ОДОВ(57) Устройство, содержит циклический задатчик адреса (2), вциклическом порядке подключает постоянное запомийающее устройство (1), управляемой задержки (3, 4, 5), коньюнктфры (б, 7, 8), источник-импульсоя (13), счетчики (9, 10, 11), источник импульсов (12), 2 ил. УСОИГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(71) Московский энергетический институт(56) Авторское свидетельство СССРЬ 1185545, кл. Н 02 М 7(00, 1984.В,А.Бизиков и др, Системы управлениятиоисторными преобразователями. М.:5 10 15 20 25 30 35 40 50 55 Изобретение относится к области преобразовательной техники и предназначено для использования в цифровых и микропроцессорных устройствах управления автономных инверторов, преобразователей частоты и инверторных компенсаторов реактивной мощности.Целью изобретения является улучшение гармонического состава выходного сигнала.,Структурная схема устройства представлена нэ Фиг,1. Адресный вход постоянного запоминающего устройства 1 связан с циклическим задатчиком адреса 2, Выход постоянного запоминающего устройства 1 подключен ко входу гп-канального многоразрядного демультиплексора 3, выходы которого подключены к управляющим входам узлов управляемой задержки 4, 5, 6, выходь 1 которых через соответственно блоки совпадения 7, 8, 9 связаны со счетными входами счетчиков 10, 11, 12, установочные входы которых связаны с источником импульсов, задающих частоту, 13, к которому подключены также входы синхронизации циклического задатчика адреса 3 и гп-канального многоразрядного демультиплексора 3 и установочные входы узлов управляемой задержки 4, 5, 6, Источник импульсов, задающих амплитуду связан с блоками совпадения 7, 8, 9. На фиг.2 представлены временные диаграммы: 15 - выходные импульсы источника импульсов, задающих частоту, 13; 16 - выходные импульсы источника импульсов, задающих амплитуду, 14;17, 18, 19 - выходные сигналы узлов управляемой задержки 4, 5, 6; 20, 21, 22 - импульсы на выходе блоков совпадения 7, 8, 9; 24, 24, 25 - весовой эквивалент сигналов на выходе счетчиков 10, 11, 12 соответственно.Принцип действия устройства заключается в следующем, Источник импульсов, задающих частоту, 13 Формирует за период 2 вп импульсов, Для определенности на фиг,2 принято в = 3, и = 2,При поступлении импульса 14 циклический задатчик адреса 2 задает очередной адрес на вход постоянного запоминающего устройства 1, выход которого через в-канальный многоразрядный демультиплексор 3 подключается к управляющему входу одного из узлов управляемой задержки. Аналогично друг за другом загружаются все узлы управляемой задержки 4, 5 и 6, причем с каждым последующим импульсом 14 в каждый управляемый узел задержки записывается следующее значение синусоиды. Отрицательные значения синусоиды представлены модулями, Сдвиг нэ угол 2 л/гп между каналами обеспечивается работой циклического задатчика адреса. Таким образом на выходе узлов управляемой задержки 4, 5, 6 формируются сигналы с широтноимпульсной модуляцией Л, 18, 19. Эти сигналы разрешают заполнение счетчиков 10, 11, 12 импульсами источника импульсов, задающих амплитуду, 14 (диаграмма 16). С приходом каждого импульса 15 каждый из счетчиков обнуляется. Таким образом перед каждым поступлением импульса 15 на каждом счетчике записан код, прямо пропорциональный частоте импульсов 16 и коду, записанному в постоянном запоминающем устройстве 1, Этот код является выходным сигналом устройства.Таким образом, имея в постоянном запоминающем устройстве запись только од-. ной синусоидальной фракции, можно получать выходные сигналы любой амплитуды. Устройство легко реализуется. особенно при применении микропроцессорных компонентов, при этом узлы управляемой задержки и счетчики выполняются на основе ИМС программируемых таймеров, а функ- . ции циклического задатчика адреса и а-канального многоразрядного мультиплексора выполняет микропроцессор. Качество выходного сигнала зависит в первую очередь от выбранного числа и. Формула изобретения Генератор п 1-фазн ых си нусоидал ьных кодов, содеркащий источник импульсов, задающих частоту, источник импульсов, эадающих амплитуду, в каналов, каждый из которых содержит счетчик, о т л и ч а ю щ и йс я тем, что, с целью улучшения гармонического состава выходного сигнала,он снабжен постоянным запоминающим устройством, запрограммированным по синусоидальному закону, циклическим задатчиком адреса и п 1-канальным многоразрядным демультиплексором, каждый канал снабжен блоком совпадения и узлом управляемой задержки, выход которого связан с первым входом блока совпадения, выход которого подключен к счетному входу счетчика, выход т-канального многораэрядного демультиплексора связан с управляющими входами узлов управляемой задержки, входы синхронизации циклического задатчика адреса и п 1-канального многозарядного демультиплексора, а также установочные входы узлов управляемой задержки и счетчиков связаны с выходом источника импульсов. задающих частоту,вторые входы блоков совпадения связаны с выходом источника импульсов, задающих амплитуду, а циклический задатчик адреса1 В 36792 подкаючен к входу в-канального многоразрядного демультиплексора; связан с адресным входом постоянного запоминающего устройства, выход которого 15 б Ш 77 18 О 20 П И Составитель Е, ЧаплыгинРедактор А, Мельникова Техред М.Моргентал Корректор Н; Ревская Заказ 3026 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

СмотретьЗаявка

4948258, 24.06.1991

МОСКОВСКИЙ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ

ЧАПЛЫГИН ЕВГЕНИЙ ЕВГЕНЬЕВИЧ, ХАММАМИ УСАМА

МПК / Метки

МПК: H02M 1/08

Метки: генератор, кодов, синусоидальных, фазных

Опубликовано: 23.08.1993

Код ссылки

<a href="https://patents.su/3-1836792-generator-faznykh-sinusoidalnykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор -фазных синусоидальных кодов</a>

Предыдущий патент: Устройство для управления тиристорами

Следующий патент: Преобразователь переменного напряжения в переменное

Случайный патент: Маховик ручного управления трубопроводной арматурой