Устройство для вычисления симметрических булевых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1835542

Авторы: Авгуль, Гришанович, Костеневич, Торбунов

Текст

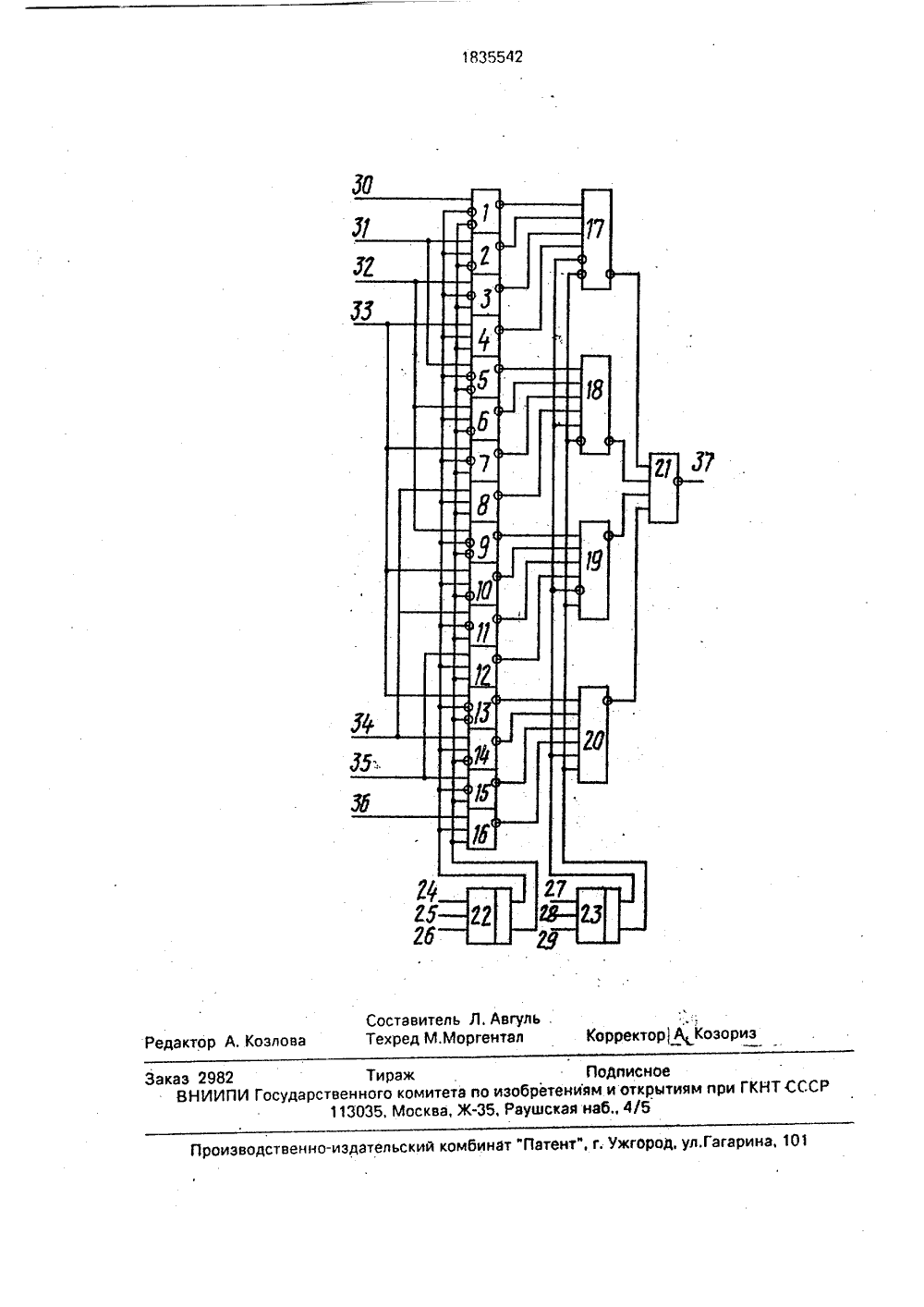

(51)5 0 06 Г 7/00 ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(56) Авторское свидетельство СССР Ь 1587489, кл. 6 06 Р 7/00, 1988,Авторское свидетельство СССР Ь 1683001, кл. С 06 Р 7/00, 1989.(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ (ВЩ 7 изобретение Ьтносится к области вычислительной техники и микроэлектроники и предназначено для реализации симметриЧеСких булевых функций шести переменИзобретение относится к вычислительной технике и микроэлектронике и предназначеноо для реализации симметрических булевых функций шести переменных.На чертеже представлена функциональная схема устройства для вычисления симметричесКих булевых функций,Устройство содержит двадцать один элемент И - НЕ 121, два одноразрядных двоичных сумматора 22 и 23, шесть информационных входов 2429, семь настроечных входов 3036, выход 37.Устройство для вычисления симметрических булевых функций работает следующим образом. На информационные входы 2429 поступают двоичные переменные х 1 х 6(в произвольном порядке), на настроенчые входы 3036 - сигналы настройки ц 1 ц 7 соо 5 еетствеино, значения которых.,Ж 1835542 А 1 ных. Цель изобретения - расширение функциональных возможностей устройства за счет реализациц симметрических булевых функций шести переменных, Поставленная цель достигается тем, что устройство содержит двадцать один элемент И-НЕ, два одноразрядных двоичных сумматора, шесть информационных входов, семь настроечных входов и один выход. При подаче на информационные, входы двоичных переменных х 1,х 2,хЗ,х 4,х 5,х 6, на настроечные входы - сигналов настройки ц 1,ц 2,цЗ,ц 4,ц 5.цб,ц 7 на выходе реализуется некоторая симметрическая булевая функция Р=Цх 1,х 2,хЗ,х 4,х 5,х 6), определяемая вектором настройки и=(ц 1, г,цэ,ц 4,ц 5,цб,ц 7).1 и . принадлежат множеству (О, 1), На выходе 37 реализуется некоторая симметрическая булевая функция Г=Е(х 1,х 6), определяемая вектором настройки 0=(ц 1 ц 2 ц 6).Рассмотрим алгоритм настройки. Пусть р 5 - значение Р на наборе аргументов х 1,х 2,. хб, содержащем равно э единиц, т.е. Г=Цх 1,х 6)=р 5 при х 1+х 2+хЗ+х 4+х 5+хб=э, 5=0,6.Компоненты вектора настройки 0 инверсны соответствующим значениям р 5, а ИМЕННО: Ц 5+1=Р 5, ИЛИО,ц 2,цЗ.ц 4,ц 5.цб,ц 7)=(рО,р 1,р 2, рЗ. р 4, р 5. р 6.П р и м е р. Определим вектор настройки О устройства на реализацию функции 5=5(х 1, х 6) = х 1 х 2 хЗх 4 х 5 х 6 ч х 1 х 2 хЗх 4 х 5 ч ч х 1 х 2 хЗх 4 х 6 ч х 1 х 2 хЗх 5 х 6 чч х 1 х 2 х 4 х 5 хбх ч х 1 хЗх 4 х 5 хб чч х 2 хЗх 4 х 5 хбРешение. Очевидно, что р(Е)= -(рО,р 1,р 2,рЗ,р 4,р 5,рб)- (1,1,0,0,0,0,1). Тогда О"(0,0,1,1,1,0).Следовательно, сигнал логического нуля должен быть подан на настроечные входы 30, 31 и Зб, сигнал логической единицы - на настроечные входы 32. 33, 34 и 35.Таким образом, устройство реализует 10 все 128 симметрических булевых функций шести переменных,Формула изобретенияУстройство для вычисления симметри ческих булевых функций, содержащее шесть элементов И - НЕ, причем первый вход первого элемента И-НЕ соединен с первым настроечным входом устройства, второй настроечный вход которого соединен с пер вым входомтретьего.элемента И-НЕ, первые входы четвертого и пятого элементов И-.НЕ соединены с третьим настроечным входом устройства, четвертый настроечный вход которого соединен с первым входом 25 шестого элемента И - НЕ, о т л и ч а ю щ е ес я тем, что, с целью расширения фунциональных возможностей путем реализации симметрических булевых функций шести переменных, оно содержит с седьмого по 30 двадцать первый элементы И-НЕ и два сумматора, причем первый вход седьмого элемента И - НЕ соединен с третьим построечным входом устройства, четвертый настроечный вход которого соединен с 35 первыми входами восьмого, девятого и десятого элементов И-НЕ, первые входы одиннадцатого, двенадцатого и тринадцатого элементов И-НЕ соединены с пятым настроечным входом устройства, шестой 40 настроечный вход которого соединен с первыми входами четырнадцатого и пятнадцатого элементов И-НЕ, первый вход шестнадцатого элемента И-НЕ соединен с седьмым настроечным входом устройства, первый, второй и третий информационные входы которого соединены с входами первого сумматора, выход суммы которого соединен с вторыми входами первого, третьего,5 Ф четвертого, седьмого, восьмого, десятого, двенадцатого, пятнадцатого элементов И - НЕ и первыми инверсными входами второго, пятого, шестого, девятого, одиннадцатого, тринадцатого, четырнадцатого и шестнадцатого элементов И-НЕ, выход переноса первого сумматора соединен с третьими входами первого, третьего, седьмого, десятого элементов И-НЕ, вторыми входами второго, пятого, девятого, тринадцатого элементов И - НЕ, первыми инверсными входами четвертого, восьмого, двенадцатого, пятнадцатого элементов И - НЕ, и вторыми инверсными входами шестого, одиннадцатого, четырнадцатого и шестнадцатого элементов И-НЕ, выходы первого, второго, четвертого и шестого элементов И-НЕ соединены с первого по четвертый входами семнадцатого элемента И-НЕ, пятый вход которого соединен с инверсным входом восемнадцатого, первым входом девятнадцатого, первым инверсным входом двадцатого элементов И - НЕ и выходом суммы второго сумматора, выход переноса которого соединен с шестым входом семнадцатого, первым входом восемнадцатого, инверсным входом девятнадцатого и вторым инверсным входом двадцатого элементов И-НЕ, выход которого соединен с первым входом двадцать первого элемента И-НЕ, второй и третий входы которого соединены соответственно с выходами семнадцатого элемента И - НЕ и восемнадцатого элемента И-НЕ, с второго по шестой входы которого соединены с выходами третьего, пятого, восьмого и одиннадцатого элементов И - НЕ, выходы седьмого, девятого, двенадцатого и четырнадцатого элементов И-НЕ соединены с второго по пятый входами девятнадцатого элемента И - НЕ, выход которого соединен с четвертым входом двадцать первого элемента И - НЕ, выходы которого являются выходом устройства, с четвертого по шестой информационные входы которого соединены с входами второго сумматора, выходы десятого, тринадцатого, пятнадцатого и шестнадцатого элементов И-НЕ соединены с первого по четвертый входами двадцатого элемента И - НЕ.1835542 Корректор АКозориз Составитель Л. АвгуРедактор А, Козлова Техред М.Моргентал при ГКНТСССР ужгород, ул. Гагарина, 10 Производственно-издательский комбинат "П аказ 2982 Тираж Подписно ВНИИПИ Государственного комитета по изобретениям и откр 113035, Москва,Ж, Раушская наб., 4/5

СмотретьЗаявка

4929199, 18.04.1991

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

АВГУЛЬ ЛЕОНИД БОЛЕСЛАВОВИЧ, ТОРБУНОВ ВЛАДИМИР ВАСИЛЬЕВИЧ, КОСТЕНЕВИЧ ВАЛЕРИЙ ИВАНОВИЧ, ГРИШАНОВИЧ ВЛАДИМИР ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: булевых, вычисления, симметрических, функций

Опубликовано: 23.08.1993

Код ссылки

<a href="https://patents.su/3-1835542-ustrojjstvo-dlya-vychisleniya-simmetricheskikh-bulevykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления симметрических булевых функций</a>

Предыдущий патент: Высоковольтная система электропитания с микропроцессорным управлением

Следующий патент: Устройство для сортировки чисел

Случайный патент: Устройство для определения наибольшей разности