Сумматор логарифмических кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1667053

Авторы: Золотовский, Коробков

Текст

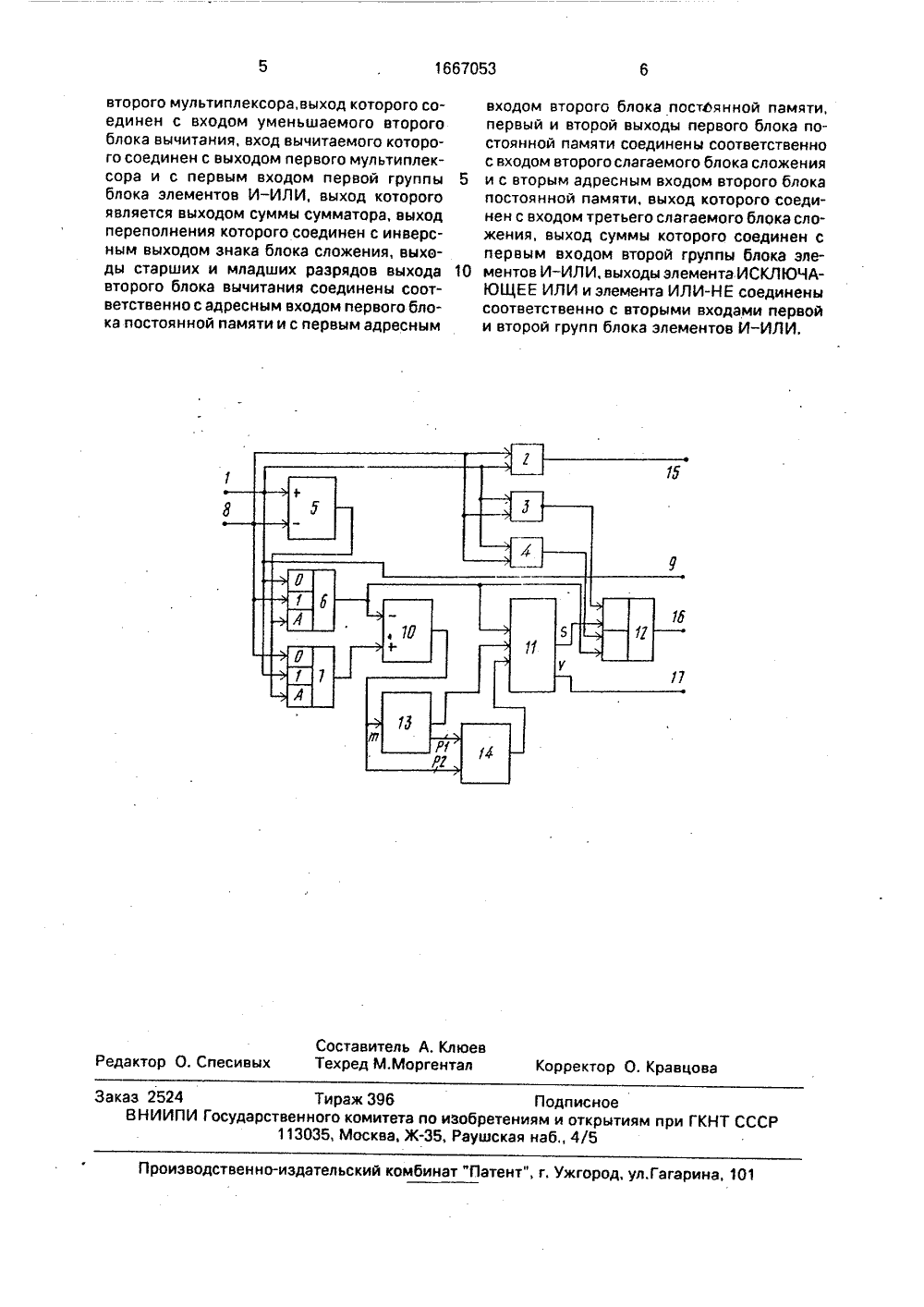

(51)5 6 06 Г 7/49 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Таганрогский радиотехнический институт им. В.Д, Калмыкова(56) Авторское свидетельство СССР М 1365077, кл. 6 06 Р 7/49, 1986.Авторское свидетельство СССР М 1168921, кл. 6 06 Г 1/02, 1984. (54) СУММАТОР ЛОГАРИФМИЧЕСКИХ КО- ДОВ Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах приобработке радиолокационных сигналов, решении задач распознавания,Целью изобретения является упрощение сумматора.На чертеже представлена схема сумматора логарифмических кодов.Сумматор содержит вход 1 первого слагаемого сумматора, элемент И 2, элемент ИЛИ - НЕ 3, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, первый блок 5 вычитания, первый и второй мультиплексоры 6 и 7, вход 8 второго слагаемого сумматора, выход 9 знака сумматора, второй блок 10 вычитания, блок 11 сложения, блок 12 элементов И - ИЛИ, первый и второй блоки 13 и 14 постоянной памяти, выход 15 признака сумматора, выход 16 суммы сумматора, выход 17 переполнения сумматора,Сумматор логарифмических кодов предназначен для сложения двух чисел с одинаковыми знаками, представленными в логарифмических кодах, Логарифмический.Ы 2 1 б 67053 А 1(57) Изобретение относится к вычислительной технике и может быть использовано при построении универсальных и специализированных цифровых вычислительных машин. Целью изобретения является упрощение сумматора, Сумматор содержит элемент И 2; элемент ИЛИ - НЕ 3, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, первый и второй блоки 5 и 10 вычитания, первый и второй мультиплексоры 6 и 7, блок 11 сложения, блок 12 элементов И-ИЛИ, первый и второй блоки 13 и 14 постоянной памяти со связями. 1 ил. код некоторого числа а 1 есть х 1 = 1 о 921 а 11. Так как 01 а 1 1 1, то О х 1-1 о 92 тГ, где 1 Г- разрядность числа а,. Логарифмический код х 1 имеет следующий форматздп г к 1 К 2, где в однобитовом поле з 1 дп записывается знак числа а 1, в однобитовом поле а записывается код 1, если а 1=0, в поле к 1, имеющем 1 од 2 д) разрядов, записывается целая часть 0" 1 од 2 а 11, в поле 2, имеющем л разрядов О записывается дробная часть 1 о 92 1 а 11 . При Ж=15 11= 4, 12 = 15 и логарифмичЕский код(,.) х 1 содержит 21 разряд, знак 1 о 92 1 а 1 всегда ) (Л отрицателен и поэтому не записывается.( )1 Сумматор работает следующим образом. Пусть необходимо найти сумму В = а 1+ а 2. На входы устройства 1 и 8 приходят логарифмические коды чисел а 1 и а 2, Необходи- в мо найти логарифмический код суммы В 21 оЯ 2 В 21 оЯа 1 + 21 оЯа 2 Выберем щах(1 ода 1, 1 ода 2), Пусть 1 ода 1Одаг. Тогда 21092 В 21 о 9 а 1 ( 1 + 21 оЯа 2 - 1 оЯа 1 ) : 21 о 9 а 1(1 +2 с)Откудао 92 В = )о 92 а 1+ )о 92(1 + 2 ).Признак г 1 первого слагаемого поступает напервые входы элементов И 2, ИЛИ-НЕ 3 иИСКЛЮЧАЮЩЕЕ ИЛИ 4, Целая и дробнаячасти кода о 92а 1, дополненные знаком,поступают на вход уменьшаемого блока 5вычитания. Код )о 92 а 11 поступает на первый вход мультиплексора 6 и второй входмультиплексора 7.Признак г 2 второго слагаемого поступает на вторые входы элементов И 2, ИЛИ - НЕ3, ИСКЛЮЧАЮЩЕЕ ИЛИ 4, Целая и дробная части кода )о 92 а 21, дополненные знаком, поступают на вход вычитаемого блока5 вычитания. Код )о 92 а 2 поступает на второй вход мультиплексора 6 и на первый входмультиплексора 7. Знак числа с входа 1 п роходит на выход 9 сумматора.В блоке 5 вычитания формируется разность о 92 а 1 - )о 92 а 2, Если знак разностиравен нулю, то )о 92 а 1)о 92 а 2, и наоборот,Поэтому на выходе мультиплексора 6 формируется п 1 ах (о 92 а 1, о 92 а 2), на выходемультиплексора 7 в)п о 92 а 1, )о 92 а 2), С выходов мультиплексоров 6 и 7 значения поступают на входы вычитаемого и уменьшаемогоблока 10 вычитания, на выходе блока 10вычитания формируется разность - С, которая содержит Й 1 целых разрядов и кдробных, в старших разрядов (- С 1) этойразности поступают на адресные входыблока 13 памяти, Р 2 последующих разряда(- С 2) поступают на адресные входы блока 14памяти.На первом выходе блока 13 памяти формируется функциявг(од 2 а 1, оя 2 а 2)-гаах 0 ой а 1, од 2 аг) .о 92(1+2= )о 92(1+2 1)На втором выходе блока 13 памяти формируется Р 1-разрядная функция2 - с 1+2 - с 1На выходе блока 14 памяти формируется величина С 212 чНа выходе суммы блока 11 сложенияформируется величина )од 2 В =: о 92 а 1+2 - с 1+ )о 92(1+2 ) + с 2,Если г 1= г 2 = О,1+2 с 1эта величина через блок 12 элементов ИИЛИ проходит на выход 16, Если один изпризнаков г 1 или г 2 равен "1", то в разрядах)с 112 соответствующего числа записываетсяминимально возможное число 0000, 0000- 1000,0000 = -16 (и ри к = 15), 10 Число, имеющее г1, окажется большим и через блок 12 элементов И-ИЛИпройдет на выход 16. Если г 1 = г 2 = 1, на выходе 15 формируется признак результата г = 1, На выходе 16 сформируется минимально возможное число.Признак переполнения разрядной сетки Ч считывается с инверсного выхода знакового разряда блока 11 сложения и поступает на выход 17. При к = 15 удобно иметь и = 11, Р 1 = 5, Р 2 = 5, разрядность сумматора равной 22. Тогда погрешность сумматора логарифмических кодов не превысит 215 Дополнительный положительный эффект изобретения состоит в повышении быстродействия,Формула изобретенияСумматор логарифмических кодов, со 20 держащий элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,. первый блок вычитания,первый и второй мультиплексоры, блок сложения, первый и второй блоки постояннойпамяти, причем выход знака первого блока25 вычитания соединен с управляющими входами первого и второго мультиплексоров,выход первого мультиплексора соединен свходом первого слагаемого блока сложения,о т л и ч а ю щ и й с я тем, что, с целью30 упрощения сумматора, он содержит элемент ИЛИ - НЕ, второй блок вычитания иблок элементов И - ИЛИ, причем вход разряда признака входа первого слагаемого сумматора соединен с первыми входами35 элемента И, элемента ИЛИ-НЕ и элементаИСКЛЮЧАЮЩЕЕ ИЛИ, вход разряда признака входа второго слагаемого сумматорасоединен с вторыми входами элемента И,элемента ИЛИ - Н Е и элемента ИСКЛ ЮЧА 40 ЮЩЕЕ ИЛИ, выход элемента И являетсявыходам признака сумматора, вход разрядазнака входа первого слагаемого сумматораявляется выходом знака сумматора, входыинформационных разрядов и вход разряда45 знака входа первого слагаемого сумматорасоединены соответственно с входами разряда входа уменьшаемого первого блока вычитания, входы разрядов входа вычитаемогокоторого соединены соответственно с вхо 50 дами информационных разрядов и входомразряда знака входа второго слагаемогосумматора, входы информационных разрядов входов первого и второго слагаемыхсумматора соединены соответственно с вхо 55 дами разрядов первого и второго информационных входов первого мультиплексора,второй и первый информационные входыкоторого соединены соответственно с первым и вторым информационными входамиаказ 2524 Тираж 396 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб., 4/5 оизводственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 второго мультиплексора, выход которого соединен с входом уменьшаемого второго блока вычитания, вход вычитаемого которого соединен с выходом первого мультиплексора и с первым входом первой группы 5 блока элементов И - ИЛИ, выход которого является выходом суммы сумматора, выход переполнения которого соединен с инверсным выходом знака блока сложения, выходы старших и младших разрядов выхода 10 второго блока вычитания соединены соответственно с адресным входом первого блока постоянной памяти и с первым адресным входом второго блока постбянной памяти, первый и второй выходы первого блока постоянной памяти соединены соответственно с входом второго слагаемого блока сложения и с вторым адресным входом второго блока постоянной памяти, выход которого соединен с входом третьего слагаемого блока сложения, выход суммы которого соединен с первым входом второй группы блока элементов И - ИЛИ, выходы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента ИЛИ-НЕ соединены соответственно с вторыми входами первой и второй групп блока элементов И-ИЛИ.

СмотретьЗаявка

4741644, 27.09.1989

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЗОЛОТОВСКИЙ ВИКТОР ЕВДОКИМОВИЧ, КОРОБКОВ РОАЛЬД ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 7/49

Метки: кодов, логарифмических, сумматор

Опубликовано: 30.07.1991

Код ссылки

<a href="https://patents.su/3-1667053-summator-logarifmicheskikh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор логарифмических кодов</a>

Предыдущий патент: Комбинационный сумматор кодов фибоначчи

Следующий патент: Сумматор-умножитель по модулю три

Случайный патент: Многооборотный бесконтактный потенциометр трансформаторного типа