Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

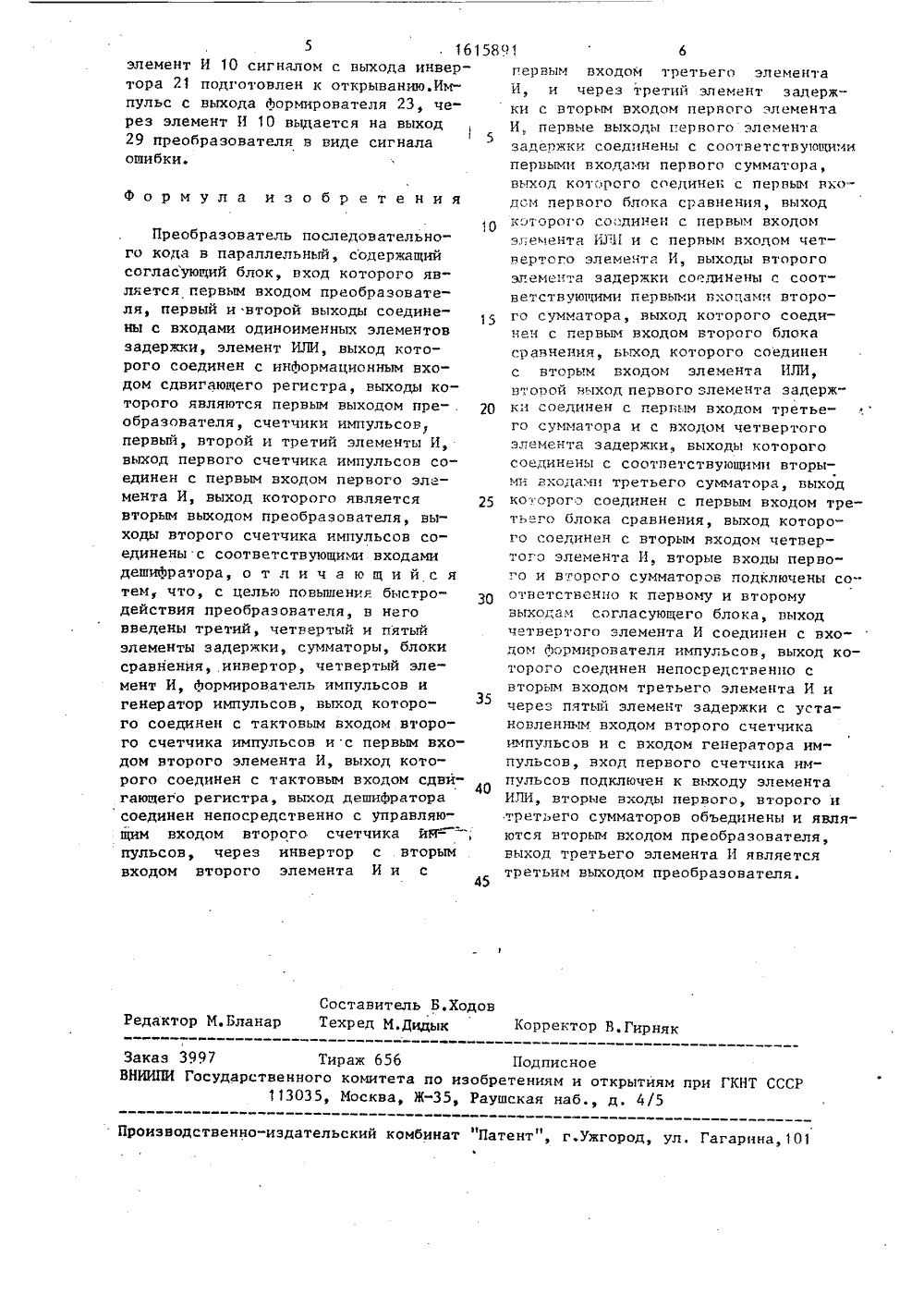

СОЮЗ СОВЕТСКИ СОЦИАЛИСТИЧЕСН 16 СПУБЛИ 19) 8(51 М 900 0 БЕЕТ ДЕТЕЛЬСТВУ ифери обес бразоней напряжения между ЭВМ иными устройствами. Изобрчивает прием, обработкуванне одного бита информамя, равное длительности эинформации, чем достигаетсние быстродействия преобПреобразователь содержитблок 1, элементы 2, 3, 1задержки, элемент ИЛИ 4,регистр 5, счетчики 6 иэлементы И Я, 9, 10, и 2тор 11,сумматоры 15, 1619 н 20 сравнения, имирователь 23 импульс24 импульсов, 1 ил. етени и пре 47Рукода циитого а бита выше ельство СССР 9/00, - 1982. ьство СССР 9/00, 1984. разователя.согласующий2, 13 и 14сдвигающий7 импульсов,2, дешифраи 17, блокинвертор 21,ов и генераПОСЛЕДОВАТЕЛЬНО ычислиспольнфоруровсится к ет быть инарной алов треИ 18, фор тор ОСУДАРСТВЕННЫЙ КОМИТЕ0 ИЗОБРЕТЕНИЯМ И ОТНРЬПРИ ГКНТ СССР ОПИСАНИ И АВТОРСКОМУ(21) 4420170/24-24 (22) 03.05.88 (46) 23.12.90, Бюл, (72) Л.В.Друзь и 1 О, (53) 681.325(088.8) (56) Авторское свид Иф 924696, кл. Н 03Авторское свидет В 1229968, кл. Н 03(57) Изобретение отнтельной технике и можзовано для передачимации с помощью сиги 36 ЕОЮЧф 113 БХЮ" 1 с, лчЩ.ЯИзобретение относится к вычислительной технике и может быть использовано для передачи бинарной информации с помощью сигналов трех уровней напряжения между ЭВМ и периФерийны 5 ми устройствами,Целью изобретения является повышение быстродействия преобразователя,На чертеже приведена Функциональая схема преобразователя.Преобразователь содержит согласуюй блок 1, первый 2 и второй 3 элеенты задержки, элемент ИЛИ 4, сдвиающий регистр 5, первый 6 и второй 7 1 Счетчики импульсов, г 1 ервый 8, второй 9 и третий 10 элементы И дешиФатор 11, третий 12, четвертый 13 и 1 ятый 1 14 элементы задержки, первый 15, второй 16 и третий ,7 сумматорь, первый 18,второй 19 и третий 20 блоки сравнения,инвертор 21,четвертый элемент И 22,Формирователь 23 импульсов и 1"енератор 24 импульсов, Кроме того, Па схеме обозначены перный 25 и вто рой 26 входы преобразователя первый .77второй 28 и третий 29 выходы Преобразователя.Преобразователь работает следую 1 дим образом, 3 ОВ исходном состоя:.ии счетчики 6 иобнулены (цепи начальной установки 1 е показаны), Входное слово инФормаПии подается на вход 25 последователь 1 о бит за битом. При этом входные" сигналы Опр еделяют ся тр емя уровнями напряжения +ь, -и, О. инФормацион ь 1 Й бит 1 кодируется уровнями: Б, Информационнь 1 й бит "О" - уровнем 0 При,.плительности импульса и паузы (нуО леной Лнт) Т , Начало слова кодируетю . с Ся 11 мпульсом двойной длительности 2 Т урон 11 ем +П Положительные импульсы разрядов слона поступают на входы элемента 2 задержки, отрицательные 45 импульсы - на вход элемента 3 задержки. Элементь 1 2, 3 и 13 задержки с максимальной задержкой сигнала на вы" ходе Т имеют определенное число от"Д нодон, сигналы с которых подаются на входы соответствующих сумматоров 5 17. Последние определяют сумму единичных сигналов на выходах соответ:тнующих элементов 2, 3 и 13 задержки с учетом входных сигналон на эти элементы. Коды сумм единиц с выходов сумматоров 15-17 подаются на первые входи соответствующих блоков 18-20 :равнения, на вторь 1 е входы которых по входу 26 постоянно поступает код порогового числа. Если сумма единиц на выходе соответствующего сумматора пре вышает это пороговое число, то на выходе соответствующего блока сравнения Формируется выходной сигнал.Для импульсов начала слова совпадение сигналов на выходах блоков 18 и 20 сравнения выявляется элементом И 22, Импульс с выхода последнего по. дается на вход Формирователя 23, который Формирует узкий импульс. Этот импульс опрашивает элемент И 10 и через элемент 14 задержки обнуляет счетчик 7 и синхронизирует с этого момента работу генератора 24. Последний Формирует последовательность импульсов с периодом следования То,которая поступает через элемент И 9 на вход регистра 5 и тактовый вход счетчика 7, Импульсы, соответствующие положительным входным сигналам, с выхода блока 18 сравнения и отрицательным - с выхода блока 19 сравнения подаются на входы элемента ИЛИ 4 и далее на инФормационный вход сдвигающего регистра 5, в котором накапливается параллельный код нходного слова, и на вход счетчика б по модулю дна, После выдачи числа импульсов, состветствующих количеству разрядон слова, дешиФратор 11 Формирует сигнал, который запрещает счет импульсон в счетчике 7, через инвертор 21 закрынает элементы 9 и 10 и прекращает сдвиг инФормации в регистре 5, В последнем Формируется параллельный код принятого слова.Кроме того, сигнал с выхода дешиФ- ратора 11 через элемент 12 задержки опрашивает элемент И 8, При правильной четности принятого кода счетчик 6 выдает сигнал который через элемент И Я, выдается на выход 28 преобразователя в виде сигнала "ИнФормация готова". При неправильной четности принятого кода сигнал на выходе счетчика 6 отстутсвует, элемент И 8 закрыт и сигнал "ИнФормация готова" не выдается, В случае, если в результате действия помех в процессе приема слова на вход 25 преобразователя подается случайный двойной импульс признак начала слова, то Формируется внеочередной импульс на выходе Формирователя 23. Так как процесс приема слова еще не закончен, то сигнал на выходе дешиФратора 7 отсутствует и5 1615 Я 91 элемент И 10 сигналом с выхода инвертора 21 подготовлен к открыванию.Импульс с выхода формирователя 23, через элемент И 10 выдается на выход 29 преобразователя в виде сигналаошибки. формула изобретения Составитель Б.Ходов Редактор М,Бланар Техред М,Дидык Корректор В.ГирнякЗаказ 3997 Тираж 656 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д, 4/5 Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101Ъ Преобразователь последовательного кода в параллельный, содержащий согласующий блок, вход которого является гервым входом преобразователя, первый и второй выходы соединены с входами одиноименных элементов задержки, элемент ИЛИ, выход которого соединен с информационным входом сдвигающего регистра, выходы которого являются первым выходом пре- . образователя, счетчики импульсову первьп, второй и третий элементы И, выход первого счетчика импульсов соединен с первым входом первого элемента И, выход которого является вторым выходом преобразователя, выходы второго счетчика импульсов соединены с соответствующими входами деширатора, о т л и ч а ю щ и й с я тем, что, с целью повышения бистро- действия преобразователя, в него введены третий, четвертый и пятый элементы задержки, сумматоры, блоки сравнения,.инвертор, четвертый элемент И, формирователь импульсов и генератор импульсов, выход которого соединен с тактовым входом второ" го счетчика импульсов и с первым входом второго элемента И, выход которого соединен с тактовым входом сдви" гающего регистра, выход дешиФратора соединен непосредственно с управляющим входом второго счетчика йя== пульсов, через инвертор с вторым входом второго элемента И и с первым входом третьего элементаИ, и через третий элемент задержки с вторым входом первого элементаИ первые выходы первого элементазадержки соединены с соответствующимипервыми входами первого сумматора,выход которого соединен с первым входам первого блока сравнения, выходкоторого соединен с первым входомэлемента ИЧ и с первым входам четвертого элемента И, выходы второгоэгемента задержки соединены с соответствующими первыми входами второго сумматора, выход которого соединен с первым входом второго блокасравнения, выход которого соединенс вторым входом элемента ИЛИ,второй выход первого элемента задержки соединен с первым входом третьего сумматора и с входом четвертогоэлемента задержки, выходы которогосоединены с соответствующими вторыми входами третьего сумматора, выход 25 катарога соединен с первым входом третьего блока сравнения, выход которого соединен с вторым входом четвертага элемента И, вторые входы первого и второго сумматоров подключены соответственна к первому и второмувыхогам согласующего блока, выходчетвертого элемента И соединен с входом Аармирователя импульсов, выход которого соединен непосредственно свторым входом третьего элемента И ичерез пятый элемент задержки с установленным входом второго счетчикаимпульсов и с входом генератора импульсов, вход первого счетчика импульсов подключен к выходу элементаИЛИ, вторые входы первого, второго итретьего сумматоров объединены и являются вторым входом преобразователя,выход третьего элемента И является 45третьим выходом преобразователя.

СмотретьЗаявка

4420170, 03.05.1988

ПРЕДПРИЯТИЕ ПЯ А-3706

ДРУЗЬ ЛЕОНИД ВОЛЬФОВИЧ, РУКОДАНОВ ЮРИЙ ПЕТРОВИЧ

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательного

Опубликовано: 23.12.1990

Код ссылки

<a href="https://patents.su/3-1615891-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь прямого кода в относительный

Следующий патент: Преобразователь параллельного кода в последовательный

Случайный патент: Выпрямительное устройство