Формирователь повторяющихся частотно-модулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

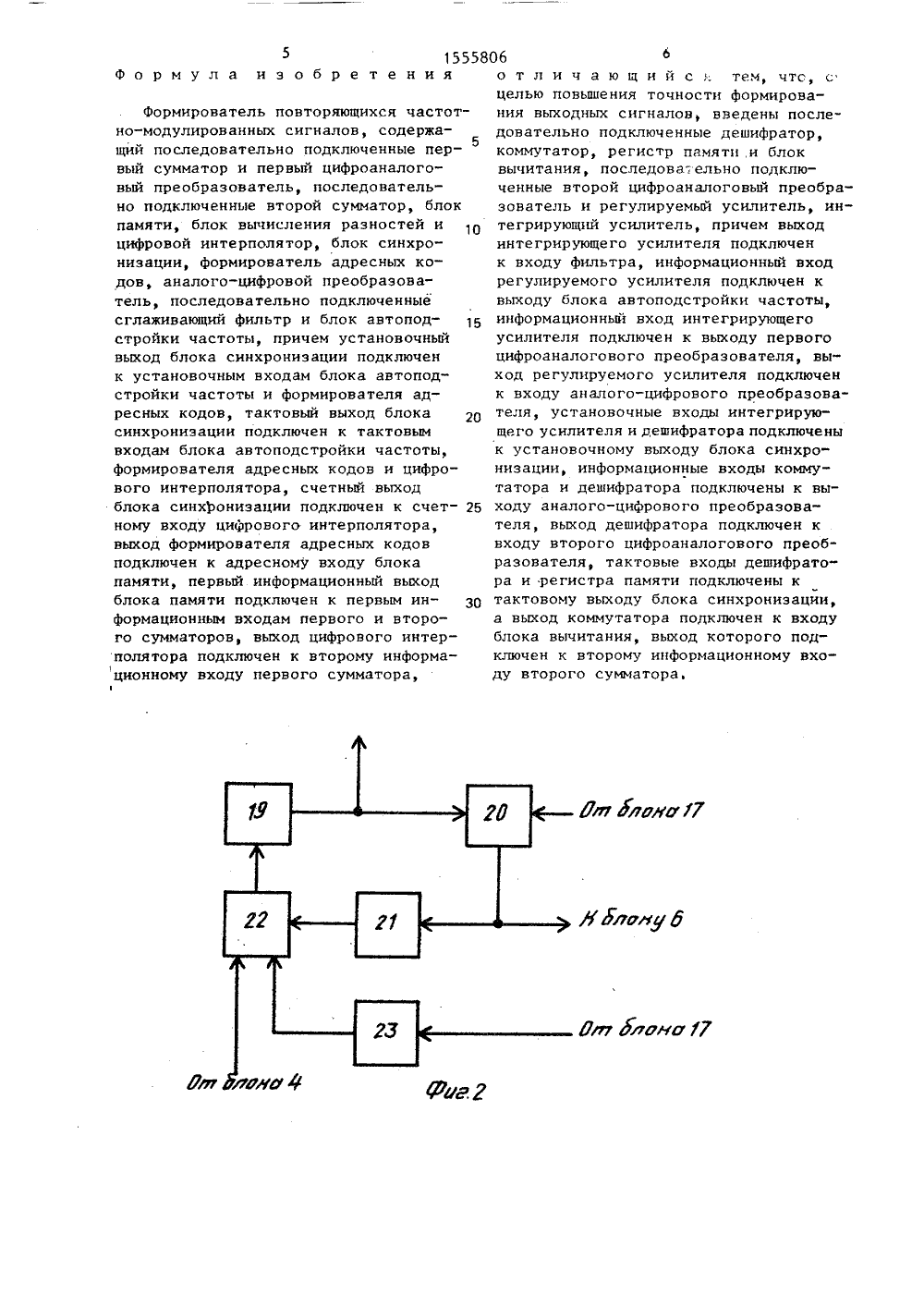

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 6 А ЯО 155 03 С 3/ НИЕ ИЗОБРЕТЕНИЯ ЛЬСТ ство СС 23/00 ь ВАТЕЛЬ ПОВТОРЯЮЩИХСРОВАННЫХ СИГНАЛОВ(54) ФОТОТНОГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР А ВТОРСКОМУ Сви(71) Всесоюзный заочный электротехнический институт связи(57) Изобретение относится к радиотехнике и связи. Цель изобретения повышение точности формирования выходных сигналов, Формирователь повторяющихся частотно-модулированных сигналов содержит сумматоры 1 и 13, ЦАП 2 и 7, интегрирующий усилитель 3, сглаживающий фильтр 4, блок 5 авто- подстройки частоты, регулируемый усилитель 6, АЦП 8, дешифратор 9, коммутатор 10, блок 11 вычитания, регистр 12 памяти, блок 14 памяти, блок 15 вычисления разностей, цифровой интерполятор 16, блок 17 синхронизации и формирователь 18 адресных кодов. Цель достигается за счет устранения сигнала ошибки от регулярной помехи. Дана ил, выполнения блока 5 автоподстройки частоты. 2 ил,Изобретение относится к радиотехнике и связи, измерительной технике и может быть использовано при испытайиях и исследованиях систем различного назначения.Цель изобретения - повышение точности формирования выходных сигналов,На фиг, 1 представлена структурная электрическая схема формирователя повторяющихся частотно-модулированных сигналов; на Фиг. 2 - структурная электрическая схема блока автоподстройки частоты. 1Формирователь повторяющихся час тотно-модулированных сигналов содержит первый сумматор 1, первый цифроаналоговый преобразователь (ЦАП) 2, интегрирующий усилитель 3, сглаживающий фильтр 4, блок 5 автопод стройки частоты, регулируемый усилитель 6, второй ЦАП 7, аналого-цифровой преобразователь (АЦП) 8, дешифратор 9, коммутатор 10, блок 11 вычитания, регистр 12 памяти, второи25 сумматор 13, блок 14 памяти, блок 15 вычисления разностей, цифровой интерполятор 16, блок 17 синхронизации и Формирователь 18 адресных кодов.30Блок 5 автоподстройки частоты соержит управляемый генератор 19, измеритель 20 отклонения от заданного, закона, Фильтр 21, сумматор 22 и генератор 23 модулирующего напряжения. Формирователь повторяющихся частот 3 но-модулированных сигналов работает следующим образом,Очередной цикл работы формирователя повторяющихся частотно-модулирован 40 ных сигналов начинается после подачи установочнык импульсов с выхода блока 17 синхронизации на соответствующие входы блоков 5 автоподстройки частоты, интегрирующего усилителя 3, логического анализатора 9 и формирователя 18 адреснык кодов. Блок 17 синхронизации формирует также тактовые и счетные импульсы. С выхода блока 5 сигнал ошибки поступает на вход регулируемого50 усилителя 6, обеспечивающего минимальный коэффициент усиления, при котором динамический диапазон АЦП 8 согласован,с диапазоном ожидаемых уровней исходного сигнала ошибки, При этом55 коммутатор 10 обеспечивает подключение выхода АЦП 8 к регистру 12 памяти и блоку 11 вычитания, в результате чего на выходе блока 11 вычитания формируется код разности поступившего и предыдущего отсчетов.1С выхода второго сумматора 13 коды разности записываются в блок 14 памяти, откуда по сигналам с формирователя 18 адресных кодов поступают в блок 15 вычисления разностей и далее на цифровой интерполятор 16, с выхода которого Формируется последовательность кодов для компенсации регулярной помехи. С выхода первого сумматора 1 последовательность кодов преобразуется первым ЦАП 2 в ступенчатоизменяемое напряжение и после сглаживания интегрирующим усилителем 3 и сглаживающим фильтром 4 аналоговый сигнал компенсации регулярной помехи поступает на информационный вход блока 5 автоподстройки частоты, Управление регулируемым усилителем 6 и коммутатором 10 производится по сигналам с выхода дешифратора 9, который является дешифратором состояний АЦП 8, при этом последовательность управляющих кодов в аналоговую форму преобразуется вторым ЦАП 7. Наличие управляющих сигналов, позволяющих осуществлять контроль состояния АЦП 8, и совместная работа указанных блоков с блоком 11 вычиТания и позволяют повысить точность выходных сигналов. Блок 5 авто- подстройки частоты содержит непосредственно тракт автоподстройки частоты частотно-модулированных сигналов, например линейно частотно- модулированных сигналов, который включает управляемый напряжением генератор 19, выход которого является выходом повторяющихся частотно- модулированных сигналов, а также фильтр 21, сумматор 22 и измеритель 20. В состав блока 5 входит также подключенный к второму входу сумматора 22 генератор модулирующего напряжения, для линейного частотно- модулированного сигнала он является, генератором пилообразного напряжения, Измеритель 20 представляет собой блок дискретизации частотно-модулированного сигнала тактовыми импульсами в моменты перехода через нуль. При на" личин отклонения от заданного закона на выходе измерителя 20 имеет место сигнал ошибки от регулярной помехи, устранение которой обеспечивается работой формирователя повторяющихся частотно-модулированных сигналов.5 15558Ф о р м у л а изобретения формирователь повторяющихся частотно-модулированных сигналов, содержа 5 щий последовательна подключенные первый сумматор и первый цифроаналоговый преобразователь, последовательно подключенные второй сумматор, блок памяти, блок вычисления разностей и цифровой интерполятор, блок синхронизации, формирователь адресных кодов, аналого-цифровой преобразователь, последовательно подключенные сглаживающий фильтр и блок автоподстройки частоты, причем установочный выход блока синхронизации подключен к установочным входам блока автоподстройки частоты и формирователя адресных кодов, тактовый выход блока синхронизации подключен к тактовым входам блока автоподстройки частоты, формирователя адресных кодов и цифрового интерполятора, счетный выход блока синхронизации подключен к счет ному входу цифрового интерполятора, выход формирователя адресных кодов подключен к адресному входу блока памяти, первый информационный выход блока памяти подключен к первым информационным входам первого и второго сумматоров, выход цифрового интерполятора подключен к второму информационному входу первого сумматора, 1 06ьотличающийс,. тем, что, с целью повышения точности формирования выходных сигналов, введены последовательно подключенные дешифратор, коммутатор, регистр памяти,и блок вычитания, последова-.ельно подключенные второй цифроаналоговый преобразователь и регулируемый усилитель, интегрирующий усилитель, причем выход интегрирующего усилителя подключен к входу фильтра, информационный вход регулируемого усилителя подключен к выходу блока автоподстройки частоты, информационный вход интегрирующего усилителя подключен к выходу первого цифроаналогового преобразователя, выход регулируемого усилителя подключен к входу аналого-цифрового преобразователя, установочные входы интегрирующего усилителя и дешифратора подключены к установочному выходу блока синхронизации, информационные входы коммутатора и дешифратора подключены к выходу аналого-циФрового преобразователя, выход дешифратора подключен к входу второго цифроаналогового преобразователя, тактовые входы дешифратора и регистра памяти подключены к тактовому выходу блока синхронизации, а выход коммутатора подключен к входу блока вычитания, выход которого подключен к второму информационному входу второго сумматора.

СмотретьЗаявка

4409390, 14.04.1988

ВСЕСОЮЗНЫЙ ЗАОЧНЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ

КОЧЕМАСОВ ВИКТОР НЕОФИДОВИЧ, РЕВУН АЛЕКСАНДР ДМИТРИЕВИЧ, ШПИЛЕВ ВЛАДИМИР ЮРЬЕВИЧ

МПК / Метки

МПК: H03C 3/00

Метки: повторяющихся, сигналов, формирователь, частотно-модулированных

Опубликовано: 07.04.1990

Код ссылки

<a href="https://patents.su/3-1555806-formirovatel-povtoryayushhikhsya-chastotno-modulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь повторяющихся частотно-модулированных сигналов</a>

Предыдущий патент: Формирователь имитирующего сигнала многоканальной системы связи

Следующий патент: Способ модуляции емкости -перехода в параметрических устройствах

Случайный патент: Способ заточки пил