Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1376244

Автор: Гладков

Текст

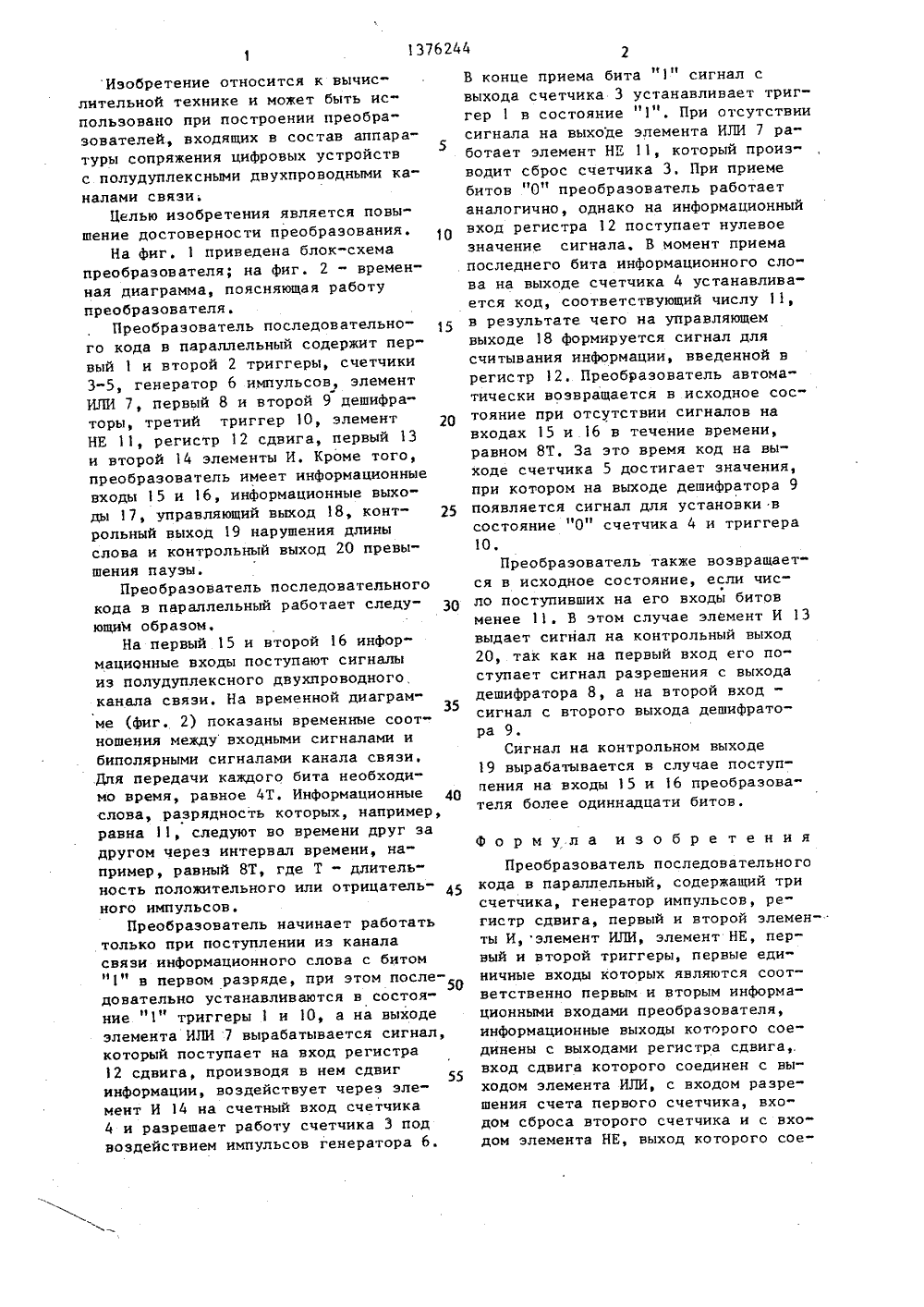

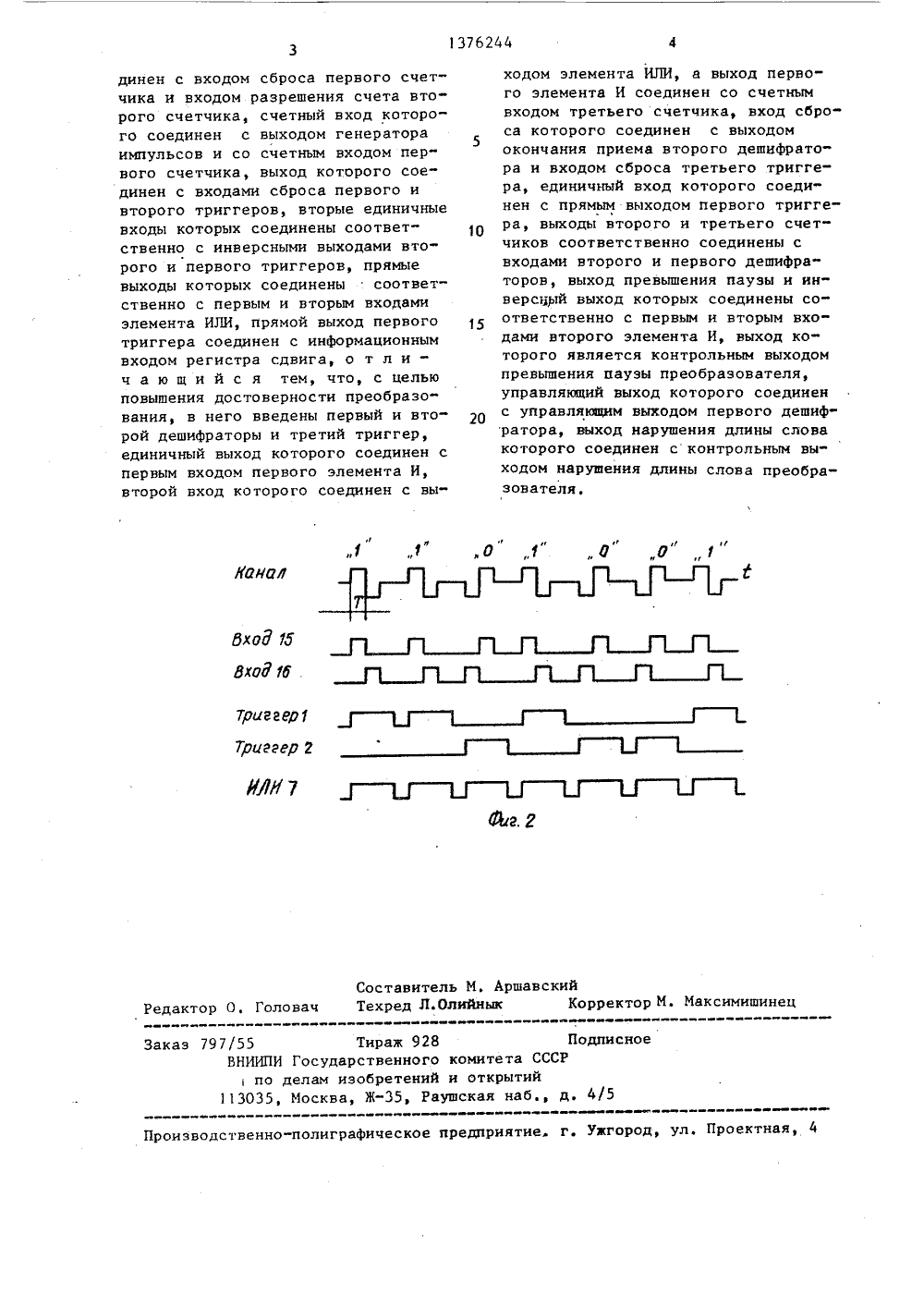

СОЮЗ СОВЕТСНИХСОЦИА ЛИСТ ИЧЕСНИХРЕСПУБЛИК 19) (11 А 1 7 504 Н 03 М 7/О САНИЕ ИЗОБРЕТЕ(2246 де" ил. ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 4115790/24(56) Авторское свидетельство СССР У 1045238, кл, С 06 К 7/016, 1982,Авторское свидетельство СССР У 1159164, кл, Н 03 М 7/00, 1985. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ(57) Изобретение относится к вычислительной технике и может быть использовано при построении преобразователей в составе аппаратуры сопряженияцифровых устройств с полудуплекснымканалами связи, Целью изобретенияявляется повышение достоверностипреобразованияПоставленная цельдостигается тем, что в преобразо"ватель последовательного кода в параллельный, содержащий три счетчика 3-5, первый и второй триггеры1,2, генератор импульсов 6, регистрсдвига 12, два элемента И 13,14,элемент ИЛИ 7, элемент НЕ 11, дополкительно введены первый и второйшифраторы и третий триггер 10. 2137624 Изобретение относится к вычислительной технике и может быть использовано при построении преобра"зователей, входящих в состав аппара"туры сопряжения цифровых устройств5с полудуплексными двухпроводными ка"налами связи.Целью изобретения является повышение достоверности преобразования.На фиг. 1 приведена блок-схемапреобразователя; на фиг. 2 - временная диаграмма, поясняющая работупреобразователя.Преобразователь последовательного кода в параллельный содержит первый 1 и второй 2 триггеры, счетчики3-5, генератор 6 импульсов, элементИЛИ 7, первый 8 и второй 9 дешифраторы, третий триггер 10, элемент 20ИЕ 11, регистр 12 сдвига, первый 13и второй 14 элементы И, Кроме того,преобразователь имеет информационныевходы 1 5 и 16, информационные выходы 17, управляющий выход 18, контрольный выход 19 нарушения длиныслова и контрольный выход 20 превы"шения паузы,Преобразователь последовательногокода в параллельный работает следующим образом,На первый 15 и второй 16 информационные входы поступают сигналыиз полудуплексного двухпроводного,канала связи, На временной диаграм 35ме (фиг. 2) показаны временные соотношения между входными сигналами ибиполярными сигналами канала связи..Для передачи каждого бита необходимо время, равное 4 Т. Информационные 4 Ослова, разрядность которых, например,равна 11, следуют во времени друг задругом через интервал времени, например, равный 8 Т, где Т - длительность положительного или отрицательного импульсов.Преобразователь начинает работатьтолько при поступлении из каналасвязи информационного слова с битом"1" в первом разряде, при этом после"5довательно устанавливаются в состояние "1" триггеры 1 и 10, а на выходеэлемента ИЛИ 7 вырабатывается сигнал,который поступает на вход регистра12 сдвига, производя в нем сдвигинформации, воздействует через элемент И 14 на счетный вход счетчика4 и разрешает работу счетчика Э подвоздействием импульсов генератора 6. 42В конце приема бита "1" сигнал свыхода счетчика 3 устанавливает триггер 1 в состояние "1". При отсутствиисигнала на выходе элемента ИЛИ 7 ра"ботает элемент НЕ 11, который произ"водит сброс счетчика 3. При приемебитов "0" преобразователь работаетаналогично, однако на информационныйвход регистра 12 поступает нулевоезначение сигнала, В момент приемапоследнего бита информационного слова на выходе счетчика 4 устанавливается код, соответствующий числу 11,в результате чего на управляющемвыходе 18 формируется сигнал длясчитывания информации, введенной врегистр 12Преобразователь автоматически возвращается в исходное состояние при отсутствии сигналов навходах 15 и 16 в течение времени,равном 8 Т. За это время код на выходе счетчика 5 достигает значения,при котором на выходе дешифратора 9появляется сигнал для установки всостояние "0" счетчика 4 и триггера10,Преобразователь также возвращает"ся в исходное состояние, если число поступивших на его входы битовменее 11, В этом случае элемент И 13выдает сигнал на контрольный выход20, так как на первый вход его поступает сигнал разрешения с выходадешифратора 8, а на второй вход "сигнал с второго выхода дешифратора 9.Сигнал на контрольном выходе19 вырабатывается в случае поступпения на входы 15 и 16 преобразователя более одиннадцати битов. Формула изобретенияПреобразователь последовательного кода в параллельный, содержащий три счетчика, генератор импульсов, регистр сдвига, первый и второй элемен-. ты И, элемент ИЛИ, элемент НЕ, первый и второй триггеры, первые единичные входы которых являются соответственно первым и вторым информационными входами преобразователя, информационные выходы которого сое" динены с выходами регистра сдвига вход сдвига которого соединен с вы" ходом элемента ИЛИ, с входом разрешения счета первого счетчика, входом сброса второго счетчика и с входом элемента НЕ, выход которого соеЗаказ 797/55 Тираж 928 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж"35, Раушская наб., д. 4/5Производственно-полиграфическое предприятие. г. Ужгород, ул, Проектная, 4 динен с входом сброса первого счетчика и входом разрешения счета второго счетчика, счетный вход которого соединен с выходом генератораимпульсов и со счетным входом пер"вого счетчика, выход которого соединен с входами сброса первого ивторого триггеров, вторые единичныевходы которых соединены соответ"ственно с инверсными выходами второго и первого триггеров, прямыевыходы которых соединены соответ"ственно с первым и вторым входамиэлемента ИЛИ, прямой выход первоготриггера соединен с информационнымвходом регистра сдвига, о т л ич а ю щ и й с я тем, что, с цельюповышения достоверности преобразования, в него введены первый и второй дешифраторы и третий триггер,единичный выход которого соединен спервым входом первого элемента И,второй вход которого соединен с выходом элемента ИЛИ, а выход первого элемента И соединен со счетнымвходом третьего счетчика, вход сброса которого соединен с выходомокончания приема второго дешифратора н входом сброса третьего триггера, единичный вход которого соединен с прямым выходом первого триггера, выходы второго и третьего счетчиков соответственно соединены свходами второго и первого дешифра"торов, выход превышения паузы и инверсный выход которых соединены соответственно с первым и вторым входами второго элемента И, выход которого является контрольным выходомпревышения паузы преобразователя,управляющий выход которого соединенс управляющим выходом первого дешифратора, выход нарушения длины словакоторого соединен с контрольным выходом нарушения длины слова преобразователя.

СмотретьЗаявка

4115790, 04.06.1986

ПРЕДПРИЯТИЕ ПЯ А-3706

ГЛАДКОВ ВЛАДИМИР ДМИТРИЕВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: кода, параллельный, последовательного

Опубликовано: 23.02.1988

Код ссылки

<a href="https://patents.su/3-1376244-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь двоичного кода во временной интервал

Следующий патент: Преобразователь позиционного кода в код системы остаточных классов

Случайный патент: Контактный узел жидкометаллического коммутационного устройства