Центральный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 890400

Авторы: Алексеев, Бестань, Конорев, Нестеренко, Новиков, Супрун, Щербаченко

Текст

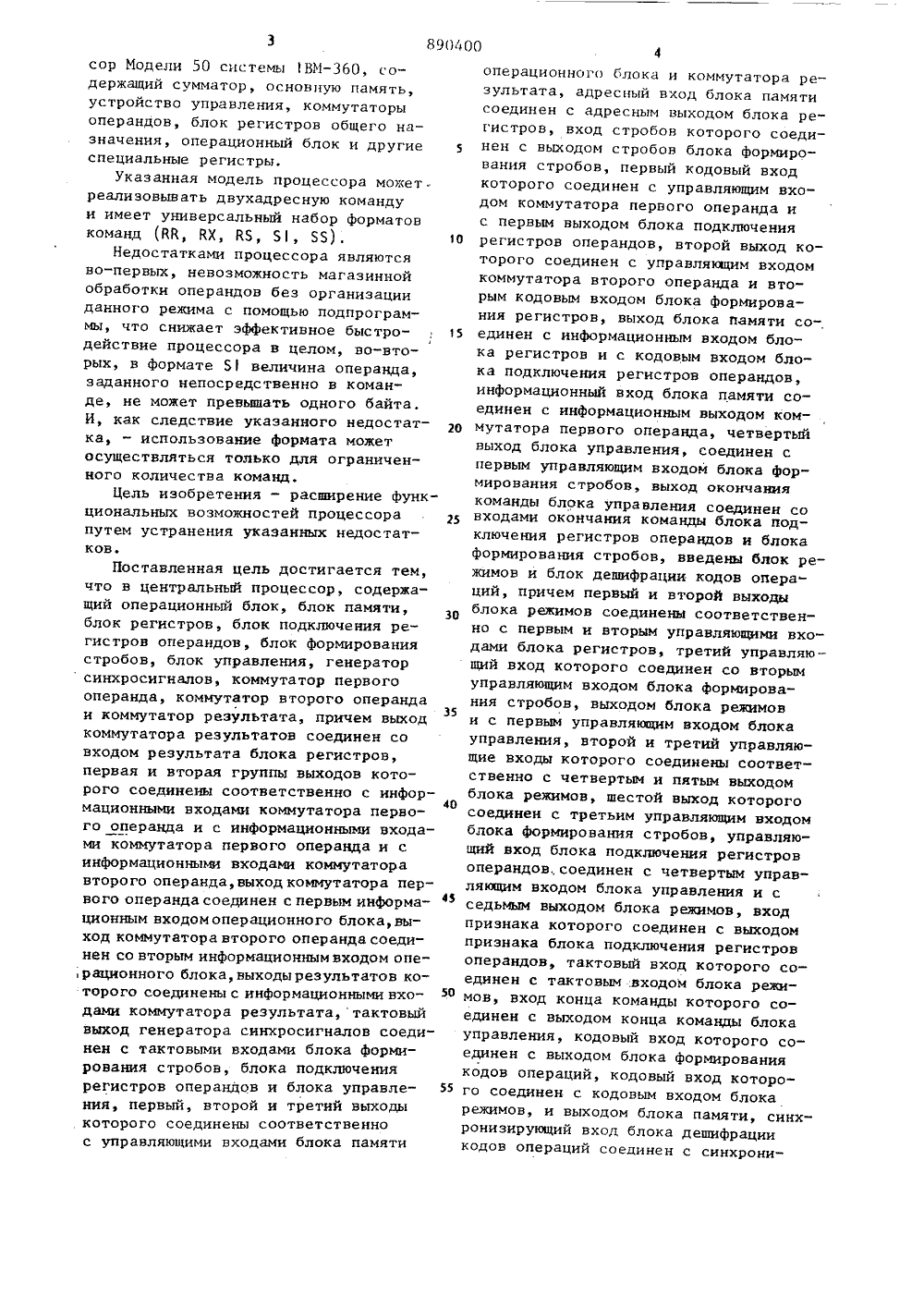

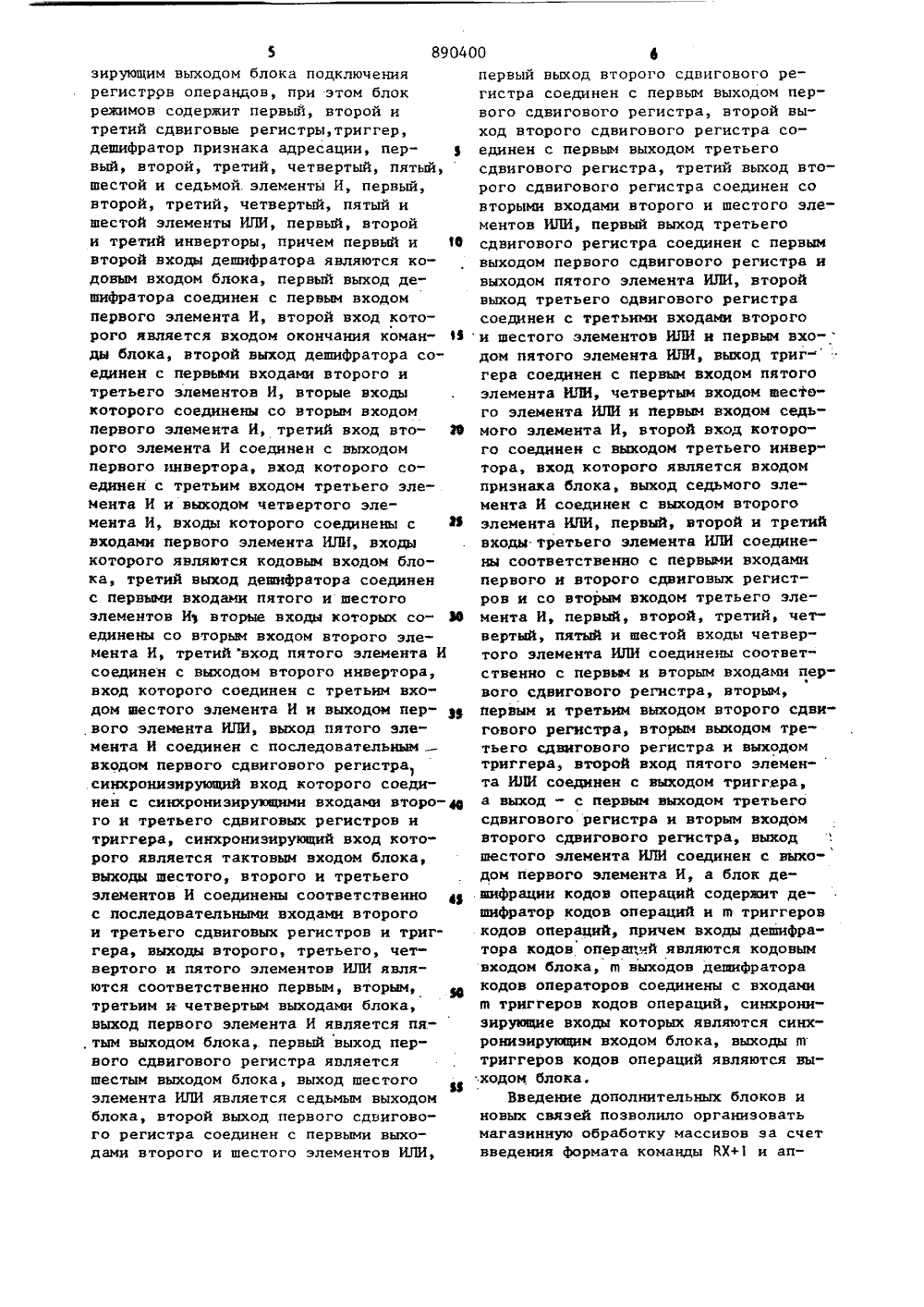

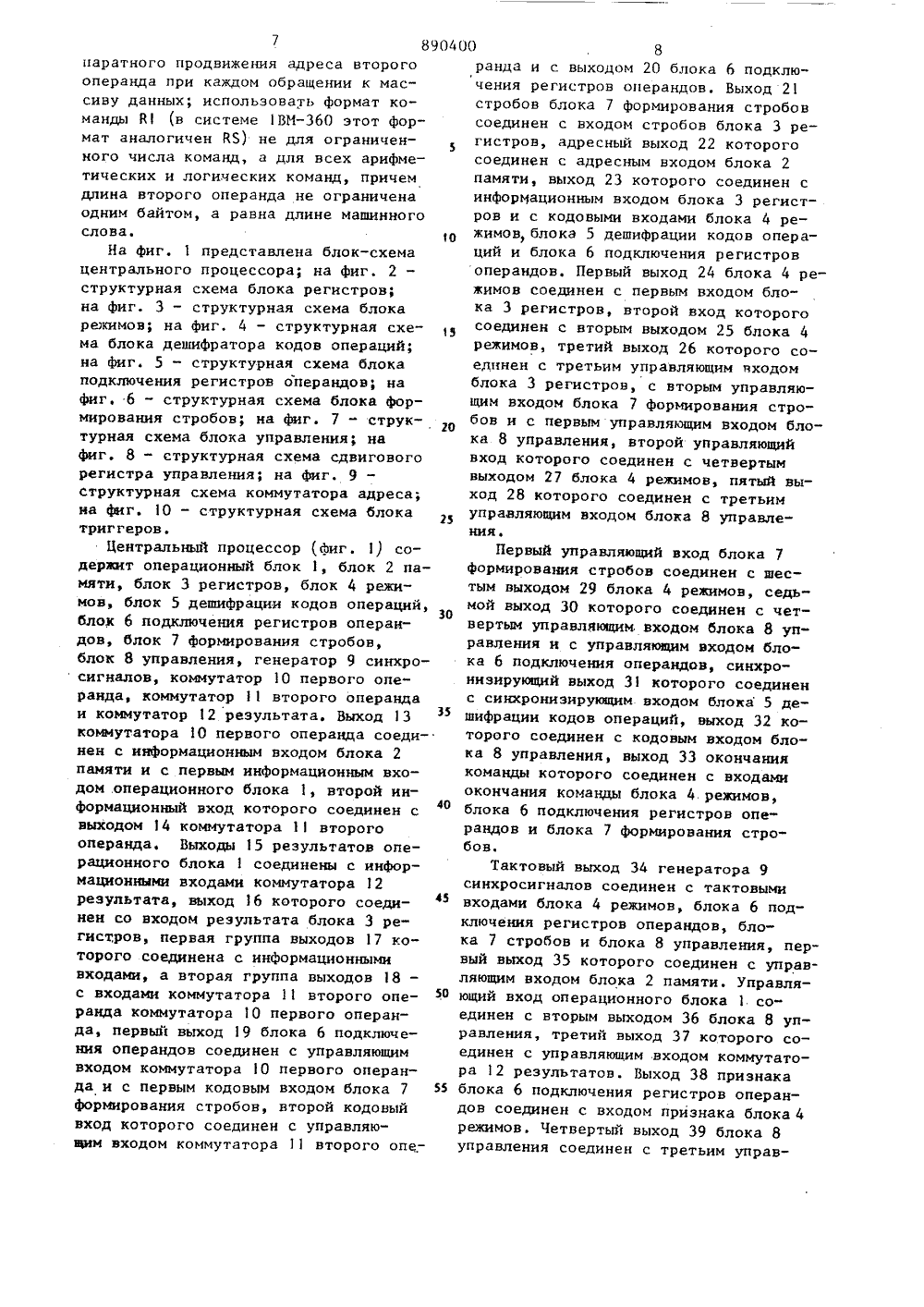

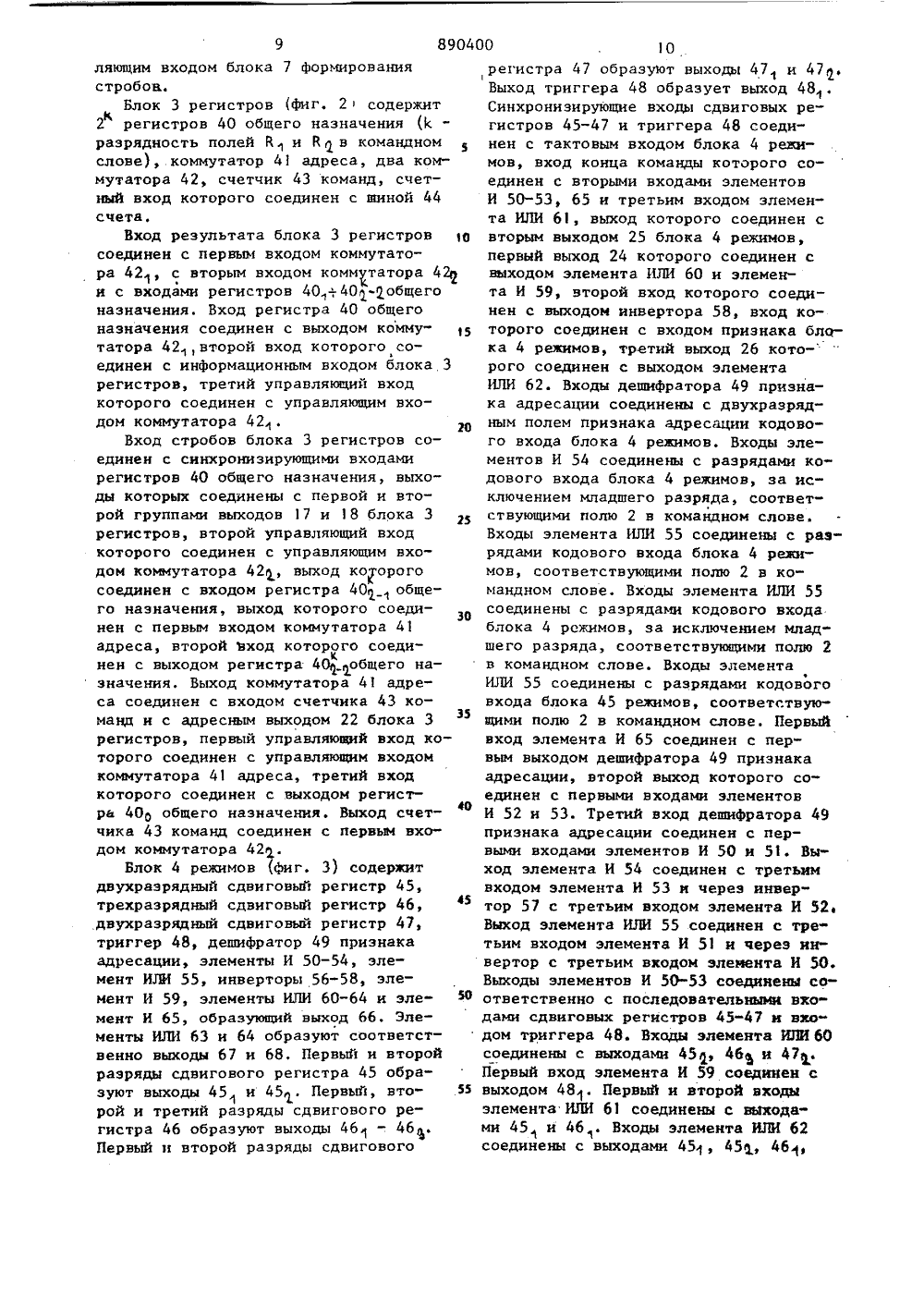

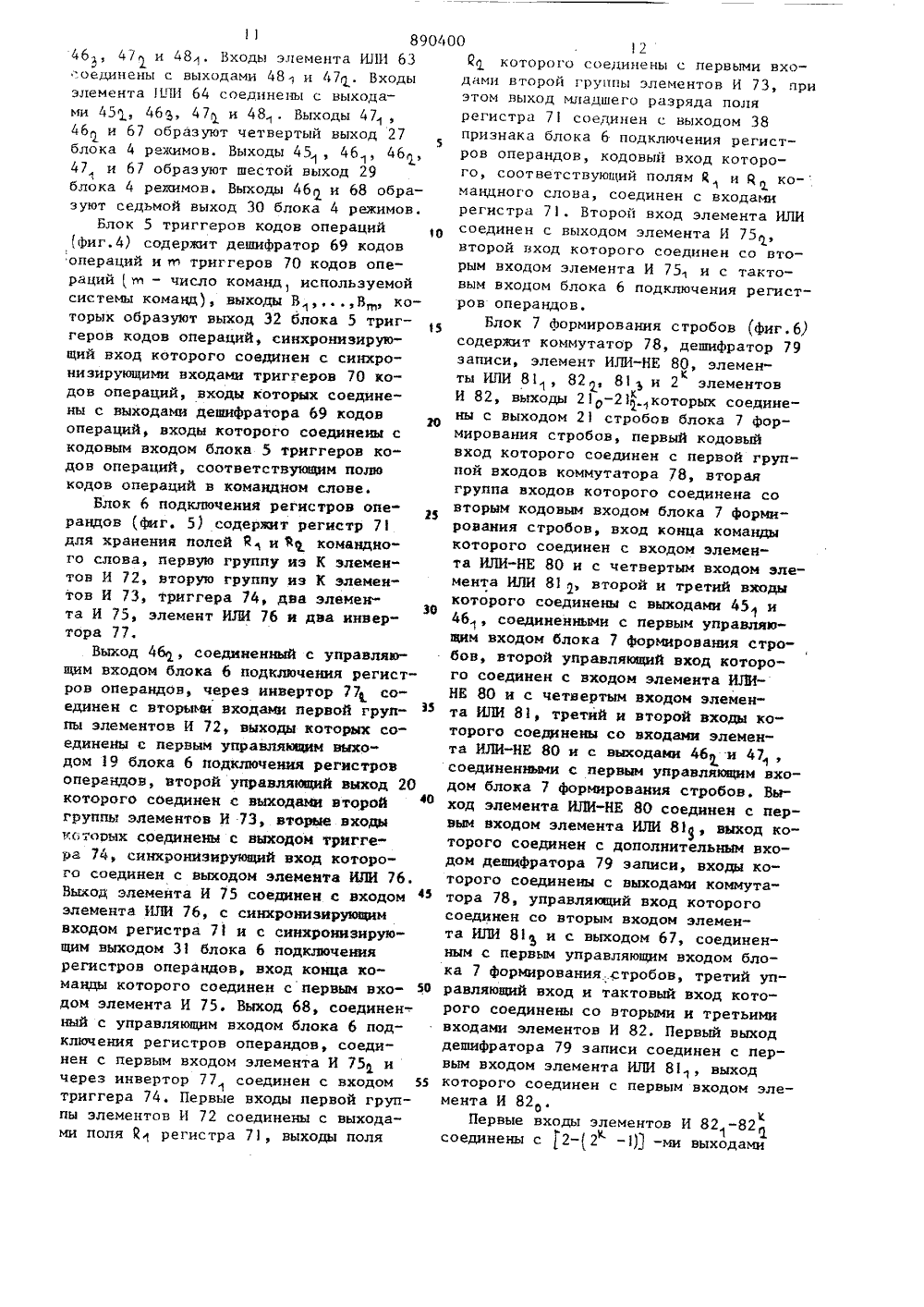

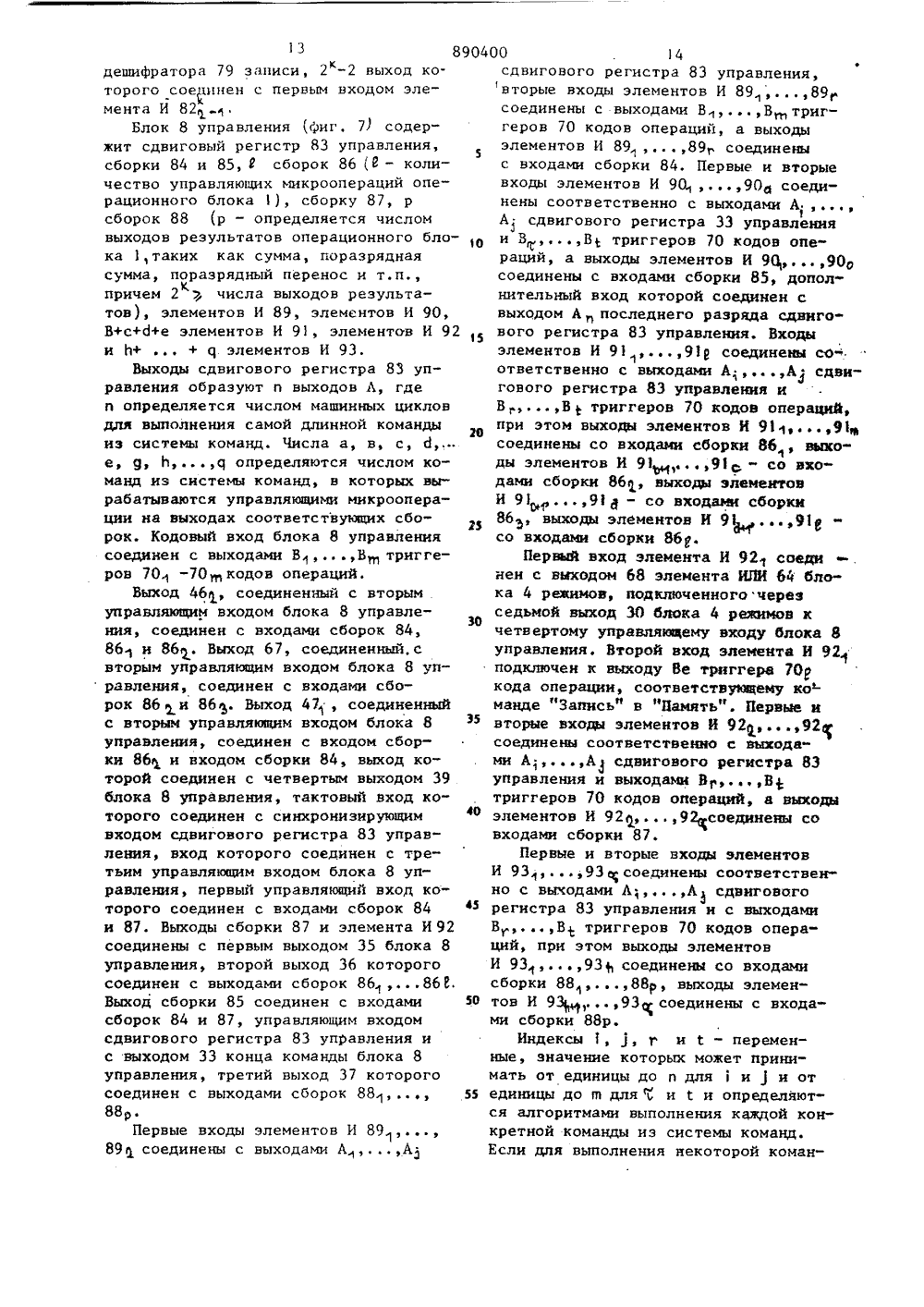

Союз СоветскикСоциалистическикРеспублик ОП ИСАНИ ИЗОБРЕТЕН И К АВТОРСКОМУ СВКДЕТЕЛЬСТВ(23) Приоритет Опубликовано Вата опубли явки М дарстеенны кемит СССР взобрвтенктерытвй 15. 12. 81. Бюллетень оваиия описания 17. УД 681.3088.8) оре 72) Авторы изобретения П. Супрун Г. Нестере Г. Алексеев, Г. С. Бестань, Б, М. Н, И, Новиков и В. Т. Щербаченко с7 ) Заявител ТРАЛЬНЫЙ ПРОЦЕССО я, блок хранРации, арифметиок памяти, блоканализа и подблок сннхроения памятью,та символов,ент И, счетчик,авляющих сигнасора. Наиболе техническодлагаемомуется процеслизким крешению пр Изобретение относится к вычислительной технике, в частности к процессорам цифровых вычислительных машин, оборудование которых используется при работе с большими массивами данных, представленных в табличном виде.Известен процессор, содержащий блок местной памяти, информационный регистр, сумматор, выходной регистр, узел формирования признаков, первую10 группу элементов И, регистр признаков, узел управления микропрерываниями, триггер режима, узел микропрограммного управления, содержащий па 1 мять микрокоманд, регистр адреса, регистр микрокоманды с дешифратором микроопераций,.информационная магистраль каналов, вторая группа элементов И, регистр хранения, третья группа элементов И, второй триггер режима, элементы задержки С 1.Известен также микропрограммныйоцессор, содержащий блок микропрограммного управлениния служебнсф информкологическии блок, блзащиты памяти, блоксчета символов данныхнизацин, блок управлблок анализа и подсчесхему сравнения, элемузел формирования упрлов 23Однако известные процессоры обладают следующими недостатками: во-первых, в их структуре отсутствуют элементы, обеспечивающие переадресацию с автоиндексацией, что усложняет программированиефи увеличивает время .вычислений; во-вторых, в структурах команд отсутствует формат, который позволяет второй операнд располагать непосредственно.в команде, что снижает эффективное быстродействие процес 9 8904ход 25 блока 4 режимов и далее на управляющий вход коммутатора 42, который обеспечивает подачу на вход рекгистра 401 общего назначения продвинутого" значения счетчика 43 команд,5так как на его вход подается код с выхода коммутатора 41 адреса, а на егосчетный вход подается сигнал с шины 44счета,Командное слово следующей командыс выхода 23 блока 2 памяти поступаетна кодовые входы блока 4 режимов, блока 5 дешифрации кодов операций и блока 6 подключения регистров операндов.После признака адресации командногослова поступает на дешифратор 49 признака адресации, поле 2 командногослова без его младшего разряда поступает на элемент И 54 и полностью поступает на вход элемента ИЛИ 55 и на20вход зоны И регистра1. Поле Р 1 командного слова поступает на вход зонырегистра 71, а поле кода операции в командном слове поступает навход дешифратора 69 кода операции,на одном из выходов которого вырабатывается сигнал. При этом, если полепризнака адресации (ПА) в командномслове следующей команды равно "ОО"(соответствует реаимуИ -регистр - реЗбгистр - выполненная команда), то сигнал вырабатывается на первом выходедешифратора 48 признака адресациии через элемент И 65, его выход бб ивыход 28 блока 4 режимов поступит через элемент ИЛИ 94 на вход элемента И 96, Если ПА " "01" режимРХ+1 - выполнение команды в режимерегистр - память, причем адрес второго операнда находится в одном из регистров 40 общего назначения содержи 40мое которого увеличивается на единицу - магазинная организация работы),то сигнал вырабатывается на второмвыходе дешифратора 49 ПА и открываетпо вторым входам элементы И 52 и 53,15причем при равенстве полякодам110 или "11" на выходе элемента И 54 вырабатывается сигнал ипроходит только через элемент И 53на вход триггера 48, при других кодахв поле Р сигнал на выходе элемента И 54 отсутствует, поэтому на выходе инвертора 57 вырабатывается сигнал и поступает на вход сдвиговогорегистра 47. 55Если ПА = "10", то сигнал вырабатывается только на третьем выходе дешифратора 49 ПА и открывает по вторым 00 20входам элементы И 50 и "1, причем при неравенстве поля 2 коду "00" на гыходе элемента ИЛИ 56 вырабатывается сигнал и проходит только через элемент И 51 на вход сдвигового регистра 46, а при равенстве поля 1 коду "00" на выходе элемента ИЛИ 55 сигнал отсутствует, а на выходе инвертора 56 сигнал вырабатывается и через элемент И 50 поступает на вход сдвигового регистра 45, Сигнал с выхода 39 блока 8 управления, поступая на элементы И 82, открывает нх по вторым входам. Сигнал ОК с выхода 33 блока 8 управления, поступая на вход элемента И 75, открывает его по первому входу и поступая, с одной стороны, через элемент ИЛИ 81 на элемент И 82к открывает его по первому входу, и с другой стороны, поступая на вход элемента ИЛИ-НЕ 80, обуславливает отсутствие сигнала на его выходе и соответственно на дополнительном входе дешифратора 79 записи. При отсутствии сигнала на дополнительном входе дешифратора 79 записи сигнала на его выходах отсутствует, а при наличии еигнала на дополнительном входе дешифратора 79 записи появляется сигнал на одном из его выходов,соответствующем коду, подаваемому на его входы с выходов коммутатора 78.При появлении сннхросигнала на тактовом выходе 34 генератора 9 синхросигналов, во-первых, выработается сигнал на выходе элемента И 82 ,1 и запишется продвинутое значенике счетчика 43 команд в регистр 40общего назначения, во-вторых, вырабатывается сигнал на выходе элемента И 75 и. пройдя через элемент ИЛИ 76, запишет "1" в триггер 74, так каксигнал на выходе 68 элемента ИЛИ 64отсутствует, а на выходе инвертора 77, присутствует. Кроме того, сигнал с выхода элемента И 751 запишет состояние полей % и О командногослова в регистр 71 и, поступая с синхрониэируюшего выхода 31 блока 6 подключения операндов на синхронизирующий вход блока 5 триггеров кодов операций, произведет установку в единицу только одного изтриггеров 70кода операции.Кроме того, синхросигнал с тактового выхода 34 генератора 9 синхросигналов в зависимости от состоянияполей ПА и 2 командного слова произведет запись единицы либо в первый раз890 55 ряд сдвигового регистра 83 управления прн ПА = "00", либо в триггер 48 при ПА = "01" и Я = "110" или"111", либо в первый разряд сдвигового регистра 47 при ПА = "01" и 1 Ф "110" или 1 Ф "111", либо в первый разряд сднигового регистра 46 при ПА = "10" и 1"00", либо в первый разряд сдвигового регистра 45 при ПА = "10" и = "00".оПри этом заканчивается действие всех управляющих сигналов вырабатываемых предыдущей командой и начинается действие управляющих сигналов, вырабатываемых вновь принятой командой.Если команда выполняется в режиме И, то в первом цикле выполнения команды сигнала В с выхода соответствующего триггера 70 кода операции и сигнал Ас выхода сдвигового регистра 83 в управления обеспечивают выработку соответствующих управляющих сигналов требуемых по алгоритму выполнения данной команды (совпадение сигналов А и В на входах соответствующих элементов И 89-93 н подача сигнала через соответствующие сборки 84-88 на выходы 33, 35-37 39 блока 8 управления) . При этом первый операнд подается на первый информационный вход операционного блока 1 с одного иэ регистров 40 общего назначения через коммутатор 10 первого операнда (номер регистра 40 общего назначения подается с выхода поля 1 регистра 71 через элементы И 72 на управляющий вход коммутатора 10 первого операнда, причем, код 00 для поляне используется. Аналогичньич образом код поля 1 регистра 71, поступая через элементы И 73 на управляющий вход коммутатора 11 второго операнда, обеспечивая подачу второго операнда с соответствующего регистра 40 общего назначения на второй информационный вход операционного блока 1, который преобразует данные операнды в соответствии с кодом поступившим на его управляющий вход с выхода 36 блока 8 управления (выходы сборок 86 -86) .Если выполняемая команда выполня ется за один машинный цикл, то в первом цикле выполнения команды на одном из выходов 15 операционного блока 1 (выход "Суммы", "Поразрядной суммы", Поразрядного переноса" и т.п,) присутствует результат, причем на выходах соответствующих элементов И 93 вырабатываются сигналы, ко 400 ггторые формируют на выходе 37 блока 8 управления код, соответствующий этому требуемому результату. Данный код обеспечивает подачу результата через коммутатор 2 результата на входы коммутаторов 42 или регистров 40 -40К общего назначения в блоке 3 регистров. В этом цикле один из элементов И 89 вырабатывает сигнал, который, пройдя через сборку 84, открывает по вторым входам элементы И 82, На выходе 67 элемента ИЛИ 63 сигнал отсутствует, поэтому код полярегистра 71 через коммутатор 78 подается на входы дешифратора 79 записи, на дополнительном входе которого прйсутствует сигнал, поэтому сигналом с соответствующего выхода дешифратора 79 записи открыт по первому входу тот элемент И 82, выход которого соединен с синхронизирующнм входом регистра 40 общего назначения, в котором находится первый операнд, поэтому при появлении синхросигнала на тактовом выходе 34 генератора 9 сиихросигналов, результат запишется на место первого операнда.Кроме того, если данный цикл выполнения команды является последним ее циклом, то на выходе сборки 85 вырабатывается сигнал ОК, при этом выполнится выборка следующего командного слова, аналогично описанному,Если данный цикл выполнения команды не является последним, то после его выполнения синхросигнал с тактового выхода 34 генератора 9 синхро+ сигналов сдвинет единичный сигнал во второй разряд сдвигового регистра 83 управления и так дапее до конца выполнения команды, который определяется наличием сигнала ОК на входе сборки 85.Если команда выполняется в режимеХ при % = "00", то выполнение команды начнется с режима выборки второго операнда, в первом цикле которого на выходе 45 сдвигового регистра 45 вырабатывается сигнал, по которому на выходах 25, 26 и 29 блока 4 режимов вырабатываются сигналы. Сигнал на выходе 25 блока 4режимов настраивает коммутатор 42на пропускание кода с выхода счетчика 43 команд на вход регистра 40 1общего назначения. Сигнал с выхода 26обеспечивает выработку, во-первых,сигнала обращения к памяти на выходесборки 87 и поступающего на управляю23 8904 50 щий вход блока 2 памяти, во-вторых, сигнала на выходе 39 блока 8 управления, обеспечивающего отпирание элементов И 82 по второму входу, в-третьих, настраивает коммутатор 42 на пропус 5 канне информации с выхода 23 блока 2 памяти на вход регистра 40 общего назначения, в-четвертых, сигнал на выходе элемента ИЛИ 81 обеспечивает отпирание элемента И 82 о по первому входу, в-пятых, обеспечивает отсутствие сигнала на выходе элемента ИЛИ-НЕ 80 и соответственно на дополнительном входе дешифратора 79 записи, что обеспечивает отсутствие сигналов на всех его выходах. Кроме того, сигнал с выхода 45, поступая на вход элемента ИЛИ 81обеспечивает отпирание элеКмента И 82,1 по первому входу.Отсутствие сигнала на выходе 24 блока 4 режимов обеспечивает подачу адреса "Смещения" с выхода регистра 40 1 череэ коммутатор 41 адреса наКадресный вход блока 2 памяти и на вход счетчика 43 команд, на счетный вход которого с шины 44 счета поступает сигнал. Командное слово и "Смещение" для формата Я Х занимают две смежных ячейки памяти, причем, в фор" мате 1 Х нри 1 = "00 ф "Смещение" является исполнительным адресом второго операнда. При появлении синхросигнала на тактовом выходе 34 генератора 9 синхросигналов, во-первых, вырабатывается синхросигналы на выхоК З 5 дах 21 и 21 элементов И 82 б и 82 и производится запись "Смещения" в регистр 40 б общего назначения и "продвинутого" значения счетчика 43 коКманд в регистр 40и, во-вторых,40 сдвигает единичный сигнал с первого во второй разряд сдвигового регистра 45, после, чего начинается второй цикл выполнения режима 1 Х при Й0 01Во втором цикле режима 1 Х при 1=45 = "00" сигнал с выхода 45 сдвигового регистра 45 обеспечивает, вопервых, выработку сигнала на выходе элемента ИЛИ 60, по которому коммутатор 41 адреса пропускает исполнительный адрес второго операнда с регистра 40 общего назначения на адресный вход блока 2 памяти. Во-вторых, вырабатывается сигнал на выходе 68 элемента ИЛИ 64, который с выхо да 30 блока 4 режимов поступает на первый вход элемента И 75и открывает его по этому входу, а на входе Оо 24триггера 74 сигнал снимается. Кроме1,того, сигнал с выхода 68 поступаетна входы элемента И 921 и элементов ИЛИ 94 и ИЛИ-НЕ 97. В-третьих, вырабатывается сигнал на выходе элемента ИЛИ 62 и соответственно на выходе 26 блока 4 режимов. Работа, производимая сигналом на выходе 26 блока 4 режимов, описана выше.При появлении синхросигнала на тактовом выходе 34 генератора 9 синхросигналов, во-первых, вырабатываетсясинхросигнал на выходе 21 элемента И 82 О, по которому второй операндс выхода 23 блока 2 памяти записывается в регистр 40 р общего назначения,во-вторых, вырабатывается сигнал навыходе элемента И 75 и, пройдя через элемент ИЛИ 76, запишет нуль втриггер 74, который при этом закроетэлементы И 73, в-третьих, выдвинетединицу из сдвигового регистра 45 изапишет единицу в первый разряд сдвигового регистра 83 управления, послечего процессор начнет выполнениекоманды, которое происходит аналогично ранее описанному выполнению команды в режиме О , за исключением того,что второй операнд подается на операционный блок 1 не из регистра 40; общего назначения, определяемого кодомв поле % , а из регистра 40 О общегоназначения, так как на выходе элементов И 73 сигналы отсутствуют (нулевойкод) .Если команда выполняется в режимеХ при % 4 "00", то выполнение команды начнется с режима выборки второго операнда по исполнительному адресу являющемуся суммой "Смещения" ииндекса - содержимого регистра 401общего назначения, где 1 - код в поле 1 командного слова (полерегистра 71), В первом цикле выполненияданного режима сигнал присутствует навыходе 461 сдвигового регистра 46. Выполнение первого цикла в данном режиме производится аналогично выполнению первого цикла режима Х при00, после чего происходитпереход к выполнению второго цикла,который определяется наличием сигнала на выходе 46 сдвигового регистра 46.Во втором цикле сигнал с выхода 46,во-первых, через выход 30 блока 4режимов поступает на вход инвертора 77 и запрещает срабатывание элементов И 72, что обеспечивает подачу890400 25смещения с выхода регистра 40 д общегоназначения на первый информационныйвход операционного блока 1. Во-вторых, сигнал с выхода 46, поступаячерез выход 29 блока 4 режимов навход элемента ИЛИ-НЕ 80, запрещаетотсутствием сигнала на выходе элемента ИЛИ 81 выдачу сигналов со всехвыходов дешифратора 79 записи и, поступая на вход элемента ИЛИ 81,0открывает элемент И 82 о по первомуходу. В-третьих, сигнал с выхода 462,поступая через выход 27 блока 4 режимов на входы сборок 84, 86.1 и 86обеспечивает выработку сигналов на ихвыходах. При этом сигнал с выходасборки 84 открывает элемент И 82 о повторому входу. Сигналы с выходом сборок 86 и 86, поступающие через выход 36 на управляющий вход операционного блока, обеспечивают соответственно подачу первого и второго операндовв операционный блок 1 прямым кодом,при этом на первом своем выходе операционный блок 1 вырабатывает код,рав-ный сумме кодов на первом и втором информационных входах операционного блока 1. На выходах сборок 88 сигналы отсутствуют, поэтому нулевой код с выхода 37 блока Ь управления настраивает коммутатор 12 результата на пропускание кода с первого выхода операционного блока 1 на вход результата блока 3 регистров, Этот код 1 исполни 35 тельный адрес второго операнда) через коммутатор 421 поступает на вход регистра 40 общего назначения. Синхросигнал с тактового выхода 34 генера 40 тора 9 синхросигналон, во-первых, обеспечивает запись исполнительного адреса в регистр 40 О общего назначения и, во-нторых, производит сдвиг единичного сигнала со второго в третий разряд сдвигового регистра 46,45 после чего сигнал вырабатывается на его выходе 46 и происходит переход к выполнению третьего цикла данного режима, который выполняется аналогично второму циклу режима РХ при 11 = 5 О"00 ч иописанному выше. После третьего цикла выполнения режима при 1100" происходит переход к выполнению команды аналогично выполнению н режиме Щ , причем второй .55 операнд подается на второй информационный нход операционного блока 1 с регистра 40 общего назначения. Если команда выполняется в режиме 1 +1 при 11 Ф " 1 10" и Й 1111",то выполнение команды пачинается с режима выборки второгооперанда по исполнительному адресу,расположенному н регистре 40общегоназначения,где 1 задается полемкомандного слова. При этом после окончания выполнения предыдущей командыустановится в единичное состояниепервый разряд сдвигового регистра 47который определяет выборку второгооперанда из блока 2 памяти в данномрежиме. В первом цикле выполнения данного режима сигнал с выхода 47 сдви 1гоного регистра 47 обеспечивает выработку сигналов на выходах сборок 84и 86 в блоке 8 управления, Сигнал свыхода сборки 86 обеспечивает подачупрямым кодом в операционный блок 1 сего второго информационного входа операнда - содержимого регистра 40 об 1щего назначения, номер которого заданв поле % регистра 71. Сигналы иавыходах остальных сборок 86 отсутствуют, поэтому данный операнд неизменным поступает на выход "Суммы" операционного блока 1 и через коммутатор 12результата, так как сигналы на выходах элемента И 59 и элемента ИЛИ 60отсутствуют, поступают через вход первого коммутатора 42 1 в блоке 3 регистров на вход регистра 40 о общегоФназначения. Сигнал с выхода сборки 84открывает по второму входу элементы И 82 в блоке 7 формирования стробов. Кроме того, сигнал с выхода 47,поступает через элемент ИЛИ 811 наперный вход элемента И 82 о, Элеменкты И 82 -82по первому входу закрыты отсутствием сигналов на выходахдешифратора 79 записи, так как сигналс выхода 47 через элемент ИЛИ-НЕ 801запрещает отсутствием сигнала на выходе элемента ИЛИ 81 срабатываниедешифратора 79 записи,При выработке синхросигнала натактовом выходе 34 генератора 9 синхросигналов код содержимого регистра 40 Я= 1) общего назначения запишется в регистр 40 о общего назначениясигналом с выхода 21 О элемента ИЛИ 82 Ои единица из первого разряда регистра 47 переместится во второй разряд,после чего процессор перейдет к выполнению второго цикла выполненияописываемого режима, который определяется сигналом с выхода 47 сдвигоногорегистра 47.Во втором цикле выполнения данного режима сигнал с выхода 47 обеспечивает выработку сигналов на выходе 68 элемента ИЛИ 64, на выходе 67 элемента ИЛИ 63, на выходе элемента ИЛИ 62 и на выходе элемента ИЛИ 60, Отсутствие сигнала на выходе элемента И 59 и сигнала А на выходе элемента ИЛИ 60 обеспечивают настройку коммутатора 41 адреса на подачу кода адреса второго операнда с выхода регистра 40 на адресный вход блока 2 памяти. Сигнал с выхода 26 блока 4 режимов, во-первых, поступая на управляющий вход коммутатора 421, настраивает его на пропускание информации на вход регистра 40 общего назначения с выхода 23 блока 2 памяти, во-вторых, поступая на вход элемента ИЛИ 81 отпирает по первому входу элемент И 82, одновременно поступая на вход элемента ИЛИ-НЕ 80, снимает сигнал с его выхода и, в-третьих, с одной стороны, поступая на вход сборки 84 сигналом с ее выхода отпирает элементы И 82 по вторым входам и, с другой стороны, поступая на вход сборки 87, вырабатывает сигнал на ее выходе, который в качестве сигнала обращения посту- лает на управляющий вход блока 2 памяти, обеспечивает выборку второго операнда, который с выхода 23 блока 2 памяти поступает на вход регистра 40 общего назначения. Сигнал с выхода 67 элемента ИЛИ 63, во-первых, поступая иа вход коммутатора 78, настраивает его иа пропускание на входы дешифратора 79 записи кода с выхода поля 2 регистра 71, поступающего на входы коммутатора 78 череэ элементы И 731 - -73, так как на выходе триггера 74 присутствует сигнач. Во-вторых, сиг-.ал с выхода 67, поступая на вход элемента ИЛИ 81, обеспечивает выработку сигнала на одном нз выходов дешифратора 79 записи, который открывает по первому входу один из элементов И 82 -82(в данном режиме,исполнение которого производится сдвиговым регистром 47, код "00" в поле 1 в общем случае не используется, так как регистр 40 О общего назначения служит для выработки исполнительного адреса второго операнда), В-третьих, сигнал с выхода 67, поступая на входы сборок 86и 86 обеспечивает выработку сигналов на их выходах, при этом сигнал с выхода сборки 86 обеспечивает подачу единицы переноса в младший разряд операциопного блока 1, а сигнал с выхода сборки 86 обеспечивает подачу в операционный блок 1 прямым кодом операндас его второго информационного входа.Причем на втором информационном входе операционного блока 1 присутствует содержимое регистра 40; общего назначения ( кодс выхода полярегистра 71 через элементы И 731-73 к,поступая на вход коммутатора 11 настраивает его на подачу содержимогорегистра 40, общего назначения навторой информационный вход операционного блока 1), При этом на выходе"Суммы" операционного блока 1 вырабатывается код, равный сумме содержимого регистра 40; и единицы младшегоразряда, На выходах сборок 88. -88 рсигналы отсутствуют, поэтому ко;мутатор 2 результата пропускает кодс выхода "Суммы" операционного блока 1на входы регистров 40-40общегоназначения.Сигнал с выхода 68 элемента ИПИ 64,во-первых, поступая на вход инвертора 77 в блоке 6 подключения операн 1дов снимает сигнал с входа триггера 74 с одной стороны, а поступая навход элемента И 72 открывает его попервому входу. Во-вторых, сигнал свыхода 68 элемента ИЛИ 64 через выход 28 блока 4 режимов поступает навход сдвигового регистра 83 управления, настраивает его на запись сигнала в его первый разряд.При появлении синхросигнала на тактовом выходе 24 генератора 9 синхросигналов в конце выполнения второгоцикла режима й +1 при В"1 О"и й Ф"11, во-первых, в регистр 40; общего назначения 1 кодв поле 1 регистра 7) записываетсяувеличенное на единицу его предыдущее состояние, во-вторых, в регистр 40общего назначения записывается второйоперанд, в-третьих, на выходе элемента И 75 в блоке 6 подключения регистров операндов вырабатывается синхросигнал, который обеспечивает запись "нуля" в триггер 74 это обеспечивает подачу на второй информационный вход операционного блока 1 операнда не с выхода регистра 40;, а с выхода регистра 400(общего назначения 55 на протяжении времени собственно выполнения операции), в-четвертых, всдвиговый регистр 83 управления запишется единица только в первый раз29 89 ряд и, в-пятых, выталкивается сигнал со второго разряда сдвигового регистра 47, после чего сдвиговый регистр 83 управления, переведенный в режим сдвига, обеспечивает собственно выполнение самой операции (тип операции указывает сигнал с выхода одного из триггеров 70 кода операции) .Если команда выполняется в режиме В)(+ при В = "110" или В ="111", то выполнение команды начинается с режима выборки второго операнда по исполнительному адресу,расн положенному в регистре 40, или рек.-1 гистре 40 ,общего назначения .Если в этом режиме В = "111", то исполнительный адрес второго опек ранда указывается в регистре 40,1, являющмся регистром хранения для счетчика 43 команд, поэтому этот случай данного режима соответствует режиму В 1, когда второй операнд располагается в самом командном слове и командное слово занимает две смежных ячейки памяти. Таким образом, номинально, не имея режима К в рвкимах выполнения команд, предложенный процессор реализует и этот режим.Для выполнения режима ВХ +1 при Вы 1 0 цти В ы1 в конце выполнения предыдущей команды включается триггер 48, сигнал с выхода 48 которого управляет данным режимом и обеспечивает выработку сигналов на выходе 68 элемента ИЛИ 64, выходе 67 элемента ИЛИ 63 и выходе элемента ИЛИ 62 (выход 26 блока 4 режимов). Если в данном режиме В"110", то на выходе младшего разряда поля 1 регистра 71 сигнал от", сутствует, а на выходе инвертора 5 в блоке 4 режимов сигнал присутствует, поэтому сигнал с выхода 48 обеспечивает выработку сигнала на выходе элемента И 59, который, поступая на управляющий вход коммутатора 41 адреса, обеспечивает подачу адреса второго операнда с регистра 40обК щего назначения на адресный вход блока 2 памяти. Если В = "111", то на выходе 24 блока 4 режимов сигналы отсутствуют и на адресный вход блока 2 памяти поступает адрес с выхода регистра 40 . общего назначения.Сигнал с выхода 26 блока 4 режимов, во-первых, поступая через сборку 84, выход 39 блока 8 управления на входы элементов И 82 в блоке 70400 30 5 1 О 15 20 25 ЗО3540455055 стробов, открывает их по вторым входам, во-вторых, поступая через сборку 87, выход. 35 блока 8 управленияна управляющий вход блока 2 памяти,обеспечивает выборку второго операнда, который с выхода 23 блока 2 памяти через коммутатор 42, настроенныйсигналом с выхода 26 блока 4 режимов,поступает на вход регистра 40 О общего назначения. В-третьих, сигнал свыхода 26 блока 4 режимов, поступаяна вход элемента ИЛИ 81, в блоке 7формирования стробов, открывает попервому входу элемент И 820, одновременно снимается сигнал с выхода элемента ИЛИ-НЕ 80,Сигнал с выхода 67 элемента ИЛИ 63,во-первых, поступая через выход 29 .блока 4 рвеимов на вход коммутатора 78, разрешает поступление содержимого поля В регистра 71, прошедшего через элементы И 73, через коммутатор 78, на входы дешифратора 79 записи. Так как сигнал с выхода 67 поступает через элементИЛИ 81 о. на дополнительный вход дешифратора 79 записи, то он вырабатывает сигнал напоследнем выходе при 1"111"или на предпоследнем выходе при Ь 2"110", который соответственно откроет по первому входу элемент И 82пройдя через элемент ИЛИ 81 или элемент И 82. Во-вторых, сигнал с выхода 67 элемента ИЛИ 63, поступая через выход 27 блока 4 режимов на входы сборок 86и 86 Ъ, обеспечивает,аналогично описанному ранее второмуциклу режимами +1 при"111"или 111 = "110", увеличение на единицу в операционном блоке 1 содержимого регистра 40при В "1 11",Кили регистра 40при % = "1 10"ккоторое подается на второй информационный вход операционного блокачерез коммутатор 11, настроенный соответствующим образом содержимым поля 2регистра 71. Это увеличенно на единицу содержимое регистра 40 1 40 )с выхода "Суммы" операционного блока 1через коммутатор 12 результата, настроенный соответствующим образом отсутствием сигналов на выходах сборок 88, поступает на входы регистров 40-40и через коммутатор 42,Ктак как сигнал на выходе 25 блока 4режимов отсутствует, на вход регистра 40общего назначения.Сигнал с выхода 68 элемента ИЛИ 64,во-первых, открывает элемент И 75, 890400 3255 по первому входу и снимает сигнал с входа триггера 74, во-вторых, настраивает сдвиговый регистр 83 управления на запись единичного сигнала в его первый разряд.При появлении синхросигнала на тактовом выходе 34 генератора 9 синхросигналов в конце выполнения цикла режима РХ +1 (1 = "111" или"110"), во-первых, в регистр 40-1 при=11 или регистр 40при 1 = "110" запишется увеличенное на единицу его предыдущее состояние, во-вторых, в регистр 400 запишется второй операнд, в-третьих, в триггер 74 запишется нуль, который обеспечит во время выполнения команды подачу второго операнда на второй информационный вход операционного блока 1 с регистра 400 общего назначения, в-четвертых в первый разряд, сдвигового регистра 83 управления запишется единичный сигнал и, в-пятых, обнулится триггер 48, после чего сдвиговый регистр 83 управления переходит в режим сдвига и обеспечивает выполнение команды, указанной одним нз триггеров 70 кода операции.При выполнении команды записи операнда в блок 2 памяти, задаваемой триггером 70 о кода операции (выход В 0, который отпирает элемент И 92) из одного из регистров 40 общего назначения, в циклах режимов, определяемых сигналами на выходах 45 о, 464, 47 и 481, когда вырабатывается сигнал на выходе элемента ИЛИ 64, на выходе элемента И 921 вырабатывается сигнал, который в качестве сигнала записи поступает иа управляющий вход блока 2 памяти, при этом на информационный вход блока 2 памяти поступает содержимое соответствующего регистра 40 общего назначения через коммутатора 10 первого операнда, настроенного соответствующим образом кодомс выходом полярегистра 71. На этом собственно выполнение команды заканчивается, а в первом цикле, определяемом сигналом в первом разряде сдвигового регистра 83 управления, вырабатывается сигнал окончания команды на выходе 33 блока 8 управления, производя соответствующую работу, как описано выше.,Кроме того, необходимо отметить, что регистр 40 О общего назначения, используемый как регистр хранения второго операнд во всех режимах, кро 5 10 5 20 25 30 35 40 45 50 ме И , может использоваться в режимах К для хранения операндов, но его загрузка должна производиться последней из группы загружаемых регистров и предназначенных для использования в подпрограмме, все команды которой исполняются в режиме ИКоманда загрузки регистров 40 общего назначения кодами из блока 2 памяти также имеет один цикл, определяемый сигналом на выходе первого разряда сдвигового регистра 83 управления, при котором сигнал вырабатывается только на выходе сборки 86 из сборок Яб), обеспечивающий только подачу прямым кодом в операционный блок 1 кода со второго его информационного входа (содержимое регистра 400 общего назначения), который с выхода "Суммы" операционного блока 1 через коммутатор 2 результата (сигналы на выходах сборок 88 не вырабатываются) на вхокды регистров 401-402и через коммутаторы 42 и 42соответственно на вхо"1кды регистров 400 и 40 общего назначения. При этом при появлении синхросигнала иа тактовом выходе 34 генератора 9 сиихросигналов выработается сиихросигнал на выходе того иэ элементов И 82 , который открыт по первому входу сигналом с выхода дешифратора 79 записи, определяемого кодомв поле Я 1 регистра 71,Таким образом, как показал схемнотехнический анализ, центральный процессор позволяет при своей работе организовать аппаратное продвижение адреса второго операнда при каждом обращении к массиву данных, Кроме этого, позволяет использовать формат команды Й не для ограниченного числа кокоманд, а для всех арифметических команд, причем длина второго операнда не ограничена одним байтом, а равна длине машинного слова. Это позволяет существенно увеличить .эффективное быстродействие процессора, примерно на 303, а также уменьшить объем разрабатываемых программ при обработке больших массиво-данных. формула изобретения 1. Центральный процессор, содержащий операционный блок, блок памяти, блок регистров, блок подключения регистров операндов, блок формирования стробов, блок управления, генераторсинхросигналов, коммутатор первого операнда, коммутатор второго операнда и коммутатор результата, причем выход коммутатора результата соединен со входом результата блока регист 5 ров, первая и вторая группы выходов которого соединены соответственно с информационными входами коммутатора первого операнда и с информационными входами коммутатора второго операнда, выход коммутатора первого операнда соединен с первым информационным входом операционного блока, выход коммутатора второго операнда соединен со вторым информационным входом операционного блока, выходы результатов которого соединены с информационнь 1 мн входами коммутатора результата, тактовый выход генератора синхросигналов соединен с тактовыми входами блока формирования стробов, блока подключения регистров операндов и блока управления, первый, второй и третий выходы которого соединены соответственно с управляющими входами блока памяти, операционного блока и коммутатора результата, адресный вход блока памяти соединен с адресным выходом блока регистров, вход стробов которого соединен с выходом стробов блока формирования стробов, первый кодо 30 вый вход которого соединен с управляющим входом коммутатора первого операнда и с первым выходом блока подключения регистров операндов, второй выход которого соединен с управляющим З 5 входом коммутатора второго операнда и вторым кодовым входом блока формирования стробов, выход блока памяти соединен с информационным входом блока регистров и с кодовым входом блока 40 подключения регистров операндов, информационный вход блока памяти соединен с информационным выходом коммутатора первого операнда, четвертый выход блока управления соединен с45 первым управляющим входом блока формирования стробов, выход окончания команды блока управления соединен со входами окончания команды блока подключения регистров операндов и блока Ы формирования стробов, о т л и ч а - ю щ и й с я тем, что, с целью повышения быстродействия, в него введе" ны блок режимов и блок дешифрации кодов операций, причем первый и второй выходы блока режимов соединены соответственно с первым и вторым управляющими входами блока регистров,третий управляющий вход которого соединен со вторым управляющим входом блока формирования стробов, выходом блока режимов и с первым управляющим входом блока управления, второй и третий управляющие входы которого соединены соответственно с четвертым и пятым выходом блока режимов, шестой выход которого соединен с третьим управляющим входом блока формирования стробов,управляющий вход блока подключения регистров операндов соединен с четвертым управляющим входом блока управления и с седьмым выходом блока режимов, вход, признака которого соединен,с выходом признака блока подключения регистров операндов, тактовый вход которого соединен с тактовым входом блока режимов, вход окончания команды которого соединен с выходом окончания команды блока управления, кодовый вход которого соединен с выходом блока дешифрации кодов операций, кодовый вход которого соединен с кодовым входом блока режимов и выходом блока а- мяти, синхрониэирующий вход блока дешифрации кодов операций соединен с синхронизирующим выходом блока подключения, регистров операндов.2. Процессор по и. 1, о т л и ч ею щ и й с я тем, что блок режимов содержит первый, второй и третий сдвнговые регистры, триггер, дешифратор, признака адресации, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И,первый, второй, третий, четвертый, пятый и шестой элементы ИЛИ, первый, второй и третий инверторы, причем первьпЪ и второй входы дешифратора являются кодовым входом блока, первый выход дешифратора соединен с первым входом первого элемента И, второй вход которого является входом окончания команды блока, второй выход дешифратора соединен с первыми входами второго и третьего элементов И, вторые входы которых соединены со вторым входом первого элемента И, третий вход второго элемента И соединен с выходом первого ннвертора, вход которого соединен с третьим входом третьего элемента И и выходом четвертого элемента И, входы которого соединены с входами пер" вого элемента ИЛИ, входы которого являются кодовым входом блока, третий выход дешифратора соединен с первыми входами пятого и шестого элементов И, вторые входы которых соединены со0400 36 40 45 35 89 вторым входом второго элемента И,третий вход пятого элемента И соединен с выходом второго инвертора, вход которого соединен с третьим входом шестого элемента И и выходом первого элеФмента ИЛИ, выход пятого элемента И соединен с последовательным входом первого сдвигового регистра, синхронизирующий вход которого соединен с синхронизирующими входами второго и третьего сдвиговых регистров и триггера, синхронизирующий вход которого является тактовым входом блока,выходы шестого, второго и третьего элементов И соединены соответственно с последовательными входами второго и третьего сдвиговых регистров и триггера, выходы второго, третьего, четвертого и пятого элементов ИЛИ являются соответственно первым, вторым, третьим и четвертым выходами блока, выход первого элемента И является пятым выходом блока, первый выход первого сдвигового регистра является шестым выходом блока, выход шестого элемента ИЛИ является седьмым выходом блока, второй выход первого сдвигового регистра соединен с первыми выходами первого сдвигового регистра соединен с первыми выходами второго и шестого элементов ИЛИ, первый выход второго сдвигового регистра соединен с первым выходом первого сдвиговогорегистра, второй выход второго сдвигового регистра, третий выход второго сдвигового регистра соединен со вто" рыми входами второго и шестого элементов ИЛИ, первый выход третьего сдвигового регистра соединен с первым выходом первого сдвигового регистра и выходом пятого элемента ИЛИ, второй выход третьего сдвигового регистра соединен с третьими входами второго и шестого элементов ИЛИ и с первым входом пятого элемента ИЛИ, выход триггера соединен с первым входом пятого элемента ИЛИ, четвертым входом шестого элемента ИЛИ и с первым вхо 5 1 О 15 М 25 30 35 дом седьмого элемента И, второй вход которого соединен с выходом третьего инвертора, вход которого является входом признака блока, выход седьмого элемента И соединен с выходом второго элемента ИЛИ, первый, второй и третий входы третьего элемента ИЛИ соединены соответственно с первыми входами первого и второго сдвиговых регистров и со вторым входом третьего элемента И, первый, второй, третий, четвертый, пятый и шестой входы четвертого элемента ИЛИ соединены соответственно с первым и вторым входами первого сдвигового регистра, вторым, первым и третьим выходом второгб сдвигового регистра, вторым выходом третьего сдвигового регистра и выходом триггера, второй вход пятого элемента ИЛИ соединен с выходом триггера, а выход - с первым выходом третьего сдвигового регистра и вторым входом второго сдвигового регистра, выход шестого элемента ИЛИ соединен с выходом первого элемента И.Л. Процессор по п. 1, о т л и ч аю щ и й с я тем, что блок дешифрации кодов операций содерзит дешифратор кодов операций и а триггеров кодов операций, причем входы деаифратора кодов операций являются кодовым входом блока, в выходов дешифратора кодов операторов, соединены с входами е триггеров кодов операций, синхронизирующие входы которых являются синхронизирушщим входом блока, выходы щ триггеров кодов операций являются выходом блока. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРУ 557 Л 66, кл. 6 06 Г 15/ОО, 05.05.77.2. Авторское свидетельство СССРУ 6 ЛЛ 021, кл. 6 06 Г 15/00,6 06 Г 9/16, 15.11.78.Л. Хассон С. Микропрограммное управление, "Мир", 1974, ч. 2, с.144146, рис. 81 (прототип).30 сор Модели 50 системы ВМ, содержащий сумматор, основную память, устройство управления, коммутаторы операндов, блок регистров общего назначения, операционный блок и другие специальные регистры.Указанная модель процессора может реализовывать двухадресную команду и имеет универсальный набор форматов команд (ВВ, ЙХ, Й 5, 51, 55).0Недостатками процессора являются во-первых, невозможность магазинной обработки операндов без организации данного режима с помощью подпрограммы, что снижает эффективное быстро- , 15 действие процессора в целом, но-вторых, в формате 5 величина операнда, заданного непосредственно в команде, не может превышать одного байта, И, как следствие укаэанного недостатка, - использование формата может осуществляться только для ограниченного количества команд.Цель изобретения - расширение функциональных возможностей процессора путем устранения указанных недостатков.Поставленная цель достигается тем, что в центральный процессор, содержащий операционный блок, блок памяти, блок регистров, блок подключения регистров операндов, блок формирования стробов, блок управления, генератор синхросигналов, коммутатор первого операнда, коммутатор второго операнда35 и коммутатор результата, причем выход коммутатора результатон соединен со входом результата блока регистрон, первая и вторая группы выходов которого соединены соответственно с инфор 40 мационными входами коммутатора первого операнда и с информационными входами коммутатора первого операнда и с информационными входами коммутатора второго операнда, выход коммутатора первого операнда соединен с первым информа 45 ционным нходомоперационного блока,выход коммутатора второго операнда соединен со вторым информационным входом опе,рационного блока,выходырезультатов которого соединены с информационными вхо дами коммутатора результата,тактовый выход генератора синхросигналов соединен с тактовыми входами блока формирования стробов, блока подключения регистров операндов и блока управле ния, первый, второй и третий выходы которого соединены соответственно с управляющими входами блока памяти операционного блока и коммутатора результата, адресный вход блока памятисоединен с адресным выходом блока регистров, вход стробов которого соединен с выходом стробон блока формирования стробов, первый кодовый входкоторого соединен с управляющим входом коммутатора первого операнда ис первым выходом блока подключениярегистров операндов, второй выход которого соединен с упранлянзцим входомкоммутатора второго операнда и вторым кодовым входом блока формирования регистров, выход блока памяти соединен с информационным входом блока регистров и с кодовым входом блока подключения регистров операндов,информационный вход блока памяти соединен с информационным выходом коммутатора первого операнда, четвертыйвыход блока управления, соединен спервым управляющим входом блока формирования стробон, выход окончаниякоманды блока управления соединен совходами окончания команды блока подключения регистрон операндов и блокаформирования стробов, введены блок режимов и блок дешифрации кодов операций, причем первый и второй выходыблока режимов соединены соответственно с первым и вторым управляющими входами блока регистров, третий управляющий вход которого соединен со вторымуправляющим входом блока формирования стробов, выходом блока режимови с первым управляющим входом блокауправления, второй и третий управляющие входы которого соединены соответственно с четвертым и пятым выходомблока режимон, шестой выход которогосоединен с третьим управляющим входомблока формирования стробов, управляющий вход блока подключения регистровоперандовсоединен с четвертым управляющим входом блока управления и сседьмым выходом блока режимов, входпризнака которого соединен с выходомпризнака блока подключения регистровоперандов, тактовый вход которого соединен с тактовым:входом блока режимов, вход конца команды которого соединен с выходом конца команды блокауправления, кодовый вход которого соединен с выходом блока формированиякодов операций, кодовый вход которого соединен с кодовым входом блокарежимов, и выходом блока памяти, синхронизирующий вход блока дешифрациикодов операций соединен с синхрони 890400аз 11008/79ВНИИП 1 Тираж 7481 Государственного кпо делам изобретений и113035, Москва Ж, Раушслиал ППП "Патент", г. Подписное тета СССР крытий4/э Ужгород, ул, Проектная, 4 Составитель В, Латышев актор Недолуженко Техред Е. Харитончик 1;орректор Г, Решетн890400 5зируюшим выходом блока подключения регистров операндов, при этом блок режимов содержит первый, второй и третий сдвиговые регистры, триггер, дешифратор признака адресации, пер- у вый, второй, третий, четвертый, пятый, шестой и седьмой. элементы И, первый, второй, третий, четвертый, пятый и шестой элементы ИЛИ, первый, второй и третий инверторы, причем первый и 1 Ф второй входы дешифратора являются кодовым входом блока, первый выход дешифратора соединен с первым входом первого элемента И, второй вход которого является входом окончания коман- И ды блока, второй выход дешифратора соединен с первыми входами второго и третьего элементов И, вторые входы которого соединены со вторым входом первого элемента И, третий вход вто рого элемента И соединен с выходом первого инвертора, вход которого соединен с третьим входом третьего элемента И и выходом четвертого элемента И, входы которого соединены с ЗЭ входами первого элемента ИЛИ, входы которого являются кодовым входом блока, третий выход дешифратора соединен с первыми входами пятого и шестого элементов Из вторые входы которых со единены со вторьнк входом второго элемента И, третий вход пятого элемента И соединен с выходом второго иивертора, вход которого соединен с третьим входом шестого элемента И и выходом нер- Зу ,вого элемента ИЛИ, выход пятого элемента И соединен с последовательным входом первого сдвигового регистра 1 синхронизирующий вход которого соединен с синхронизирующими входами второа го и третьего сдвиговых регистров и триггера, синхронизирующий вход которого является тактовым входом блока, выходы шестого, второго и третьего элементов И соединены соответственно с последовательными входами второго и третьего сдвиговых регистров и триггера, выходы второго, третьего, четвертого и пятого элементов ИЛИ являются соответственно первым, вторым,третьим и четвертым выходами блока, выход первого элемента И является пя,тым выходом блока, первый выход первого сдвигового регистра является шестым выходом блока, выход шестого элемента ИЛИ является седьмым выходом блока, второй выход первого сдвигового регистра соединен с первыми выходами второго и шестого элементов ИЛИ,первый выход второго сдвигового регистра соединен с первым выходом первого сдвигового регистра, второй выход второго сдвигового регистра соединен с первым выходом третьего сдвигового регистра, третий выход второго сдвигового регистра соединен со вторыми входами второго и шестого элементов ИЛИ, первый выход третьего сдвигового регистра соединен с первым выходом первого сдвигового регистра ивыходом пятого элемента ИЛИ, второйвыход третьего адвигового регистрасоединен с третьими входами второгои шестого элементов ИЛИ и первым входом пятого элемента ИЛ 4, выход триг-:.гера соединен с первым входом пятогоэлемента ИЛИ, четвертым входом шестого элемента ИЛИ и первым входом седьмого элемента И, второй вход которого соединен с выходом третьего инвертора, вход которого является входомпризнака блока, выход седьмого элемента И соединен с выходом второго элемента ИЛИ, первый, второй и третий входы третьего элемента ИЛИ соединены соответственно с первыми входамипервого и второго сдвиговых регистров и со вторым входом третьего элемента И, первый, второй, третий, четвертцй, пятый и шестой входы четвертого элемента КПИ соединены соответственно с первым и вторым входами первого сдвигового регистра, вторьм,первым и третьим выходом второго сдвигового регистра, вторым выходом третьего сдвигового регистра и выходом триггера, второй вход пятого элемен-та ИЛИ соединен с выходом триггера, а выход - с первым выходом третьего сдвигового регистра и вторым входом второго сдвигового регистра, выход шестого элемента ИЛИ соединен с выходом первого элемента И, а блок дешифрации кодов операций содержит дешифратор кодов операций н в триггеров кодов операций, причем входы дешифратора кодов операций являются кодовым входом блока, ш выходов дешифратора кодов операторов соединены с входами а триггеров кодов операций, синхронизирующие входы которых являются синхрониэирующим входом блока, выходы а триггеров кодов операций являются вы" ходом блока.Введение дополнительных блоков и новых связей позволило организовать магазинную обработку массивов за счет введения формата команды ВХ+1 и ап 890400 8О 20 25 30 35 40 45 50 55 паратного продвижения адреса второго операнда при каждом обращении к массиву данных; использовать формат команды В 1 (в системе 1 ВИэтот формат аналогичен В 5) не для ограниченного числа команд, а для всех арифметических и логических команд, причем длина второго операнда не ограничена одним байтом, а равна длине машинного слова.На фиг. 1 представлена блок-схема центрального процессора; на фиг. 2 - структурная схема блока регистров; на фиг. Э - структурная схема блока режимов; на Фиг. 4 - структурная схема блока дешифратора кодов операций; на фиг. 5 - структурная схема блока подключения регистров операндов; на фиг. 6 - структурная схема блока формирования стробов; на фиг. 7 " структурная схема блока управления; на фиг. 8 - структурная схема сдвигового регистра управления; на Фиг. 9 - структурная схема коммутатора адреса; на Фиг. 10 - структурная схема блока триггеров.Центральный процессор (Фиг. 1) содержит операционный блок 1, блок 2 памяти, блок Э регистров, блок 4 режимов, блок 5 дешифрации кодов операций, блок 6 подключения регистров операндов, блокФормирования стробов, блок 8 управления, генератор 9 синхро сигналов, коммутатор 10 первого операнда, коммутатор 1 второго операнда и коммутатор 12 результата. Выход 13 коммутатора 10 первого операнда соединен с информационным входом блока 2 памяти и с первым информационным входом .операционного блока 1, второй инФормационный вход которого соединен с выходом 14 коммутатора 1 второго операнда. Выходы 15 результатов операционного блока 1 соединены с информационными входами коммутатора 12 результата, выход 16 которого соединен со входом результата блока 3 регистров, первая группа выходов 17 которого соединена с инФормационными входами, а вторая группа выходов 18 - с входами коммутатора 11 второго операнда коммутатора 1 О первого операнда, первый выход 19 блока 6 подключения операндов соединен с управляющим входом коммутатора 1 О первого операнда и с первым кодовым входом блока 7 Формирования стробов, второй кодовый вход которого соединен с управляющим входом коммутатора 11 второго операнда н с выходом 20 блока 6 подключения регистров операндов. Выход 21 стробов блока 7 формирования стробов соединен с входом стробов блока Э регистров, адресный выход 22 которого соединен с адресным входом блока 2 памяти, выход 23 которого соединен с информационным входом блока 3 регистров и с кодовыми входами блока 4 режимов, блока 5 дешифрации кодов операций и блока 6 подключения регистров операндов. Первый выход 24 блока 4 режимов соединен с первым входом блока Э регистров, второй вход которого соединен с вторым выходом 25 блока 4 режимов, третий выход 26 которого соединен с третьим управляющим входом блока 3 регистров, с вторым управляющим входом блока 7 формирования стробов и с первым управляющим входом блока 8 управления, второй управляющий вход которого соединен с четвертым выходом 27 блока 4 режимов, пятый выход 28 которого соединен с третьим управляющим входом блока 8 управления.Первый управляющий вход блока 7 формирования стробов соединен с шестым выходом 29 блока 4 режимов, седьмой выход 30 которого соединен с четвертым управляющим входом блока 8 управления и с управляющим входом блока б подключения операндов, синхроннзирующий выход 31 которого соединен с синхронизирующим. входом блока 5 дешифрации кодов операций, выход 32 которого соединен с кодовым входом блока 8 управления, выход 33 окончания команды которого соединен с входами окончания команды блока 4 режимов, блока 6 подключения регистров операндов и блока 7 формирования стробов.Тактовый выход 34 генератора 9 синхросигналов соединен с тактовыми входами блока 4 режимов, блока 6 подключения регистров операндов, блока 7 стробов и блока 8 управления, первый выход 35 которого соединен с управляющим входом блока 2 памяти. Управляющий вход операционного блока 1 соединен с вторым выходом 36 блока 8 управления, третий выход 37 которого соединен с управляющим .входом коммутатора 12 результатов. Выход 38 признака блока 6 подключения регистров операндов соединен с входом признака блока 4 режимов. Четвертый выход 39 блока 8 управления соединен с третьим управ"890400 45 ляющим входом блока 7 формированиястробоа.Блок 3 регистров (фиг, 2 содержит2 регистров 40 общего назначения (АКразрядность полей В 1 и К в командномслове), коммутатор 41 адреса, два коммутатора 42, счетчик 43 команд, счетный вход которого соединен с шиной 44счета,Вход результата блока 3 регистровсоединен с первым входом коммутатора 421, с вторым входом коммутатора 42и с входами регистров 40-; 40-общегоназначения. Вход регистра 40 общегоназначения соединен с выходом коммутатора 421,второй вход которого соединен с информационным входом блока 3регистров, третий управляющий входкоторого соединен с управляющим входом коммутатора 421.20Вход стробов блока 3 регистров соединен с синхронизирующими входамирегистров 40 общего назначения, выходы которых соединены с первой и второй группами выходов 17 и 18 блока 3регистров, второй управляющий входкоторого соединен с управляющим входом коммутатора 42, выход которогосоединен с входом регистра 40общего назначения, выход которого соединен с первым входом коммутатора 41адреса, второй ъход которого соединен с выходом регистра 40 общего назначения. Выход коммутатора 41 адреса соединен с входом счетчика 43 команд и с адресным выходом 22 блока 3регистров, первый управляющий вход которого соединен с управляющим входомкоммутатора 41 адреса, третий входкоторого соединен с выходом регистра 40 О общего назначения. Выход счет 40чика 43 команд соединен с первым входом коммутатора 42.Блок 4 режимов (Фиг. 3) содержитдвухразрядный сдвиговый регистр 45,трехразрядный сдвиговый регистр 46,двухразрядный сдвиговый регистр 47,триггер 48, дешифратор 49 признакаадресации, элементы И 50-54, элемент ИЛ 1 55, инверторы 56-58, элемент И 59, элементы ИЛИ 60-64 и эле вмент И 65, образующий выход 66. Элементы ИЛИ 63 и 64 образуют соответственно выходы 67 и 68. Первый и второйразряды сдвигового регистра 45 образуют выходы 45 и 45, Первый, вто- .551рой и третий разряды сдвигового регистра 46 образуют выходы 461 - 46 Ъ.Первый и второй разряды сдвигового 10регистра 47 образуют выходы 471 и 47, Выход триггера 48 образует выход 481. Синхронизирующие входы сдвиговых регистров 45-47 и триггера 48 соединен с тактовым входом блока 4 режимов, вход конца команды которого соединен с вторыми входами элементов И 50-53, 65 и третьим входом элемента ИЛИ 61, выход которого соединен с вторым выходом 25 блока 4 режимов, первый выход 24 которого соединен с выходом элемента ИЛИ 60 и элемента И 59, второй вход которого соединен с выходом инвертора 58, вход которого соединен с входом признака блока 4 режимов, третий выход 26 кото- рого соединен с выходом элемента ИЛИ 62. Входы дешифратора 49 признака адресации соединены с двухразрядным полем признака адресации кодового входа блока 4 режимов. Входы элементов И 54 соединены с разрядами кодового входа блока 4 режимов, за исключением младшего разряда, соответствующими полю 2 в командном слове. Входы элемента ИЛИ 55 соединены с разрядами кодового входа блока 4 режимов, соответствующими полю 2 в командном слове. Входы элемента ИЛИ 55 соединены с разрядами кодового входа блока 4 режимов, за исключением младшего разряда, соответствующими полю 2 в командном слове. Входы элемента ИЛИ 55 соединены с разрядами кодового входа блока 45 режимов, соответствующими полю 2 в командном слове. Первый вход элемента И 65 соединен с первым выходом дешифратора 49 признака адресации, второй выход которого соединен с первыми входами элементов И 52 и 53. Третий вход дешифратора 49 признака адресации соединен с первыми входами элементов И 50 и 51, Выход элемента И 54 соединен с третьим входом элемента И 53 и через инвертор 57 с третьим входом элемента И 52, Выход элемента ИЛИ 55 соединен с третьим входом элемента И 51 и через инвертор с третьим входом элемента И 50, Выходы элементов И 50-53 соединены соответственно с последовательиьвж входами сдвиговых регистров 45-47 и входом триггера 48. Входы элемента ЕЛИ 60 соединены с выходами 45, 46 и 47Первый вход элемента И 59 соединен с выходом 481. Первый и второй входы элемента ИЛИ 61 соединены с выходами 45, и 46. Входы элемента ИЛИ 62 соедийены с выходами 451, 45, 461,8904046, 4/ и 48. Входы элемента ИЛИ 63оединены с выходами 48и 4 . Входыэлемента .Уд 64 соединены с выходами 45, 46, 47 и 48, Выходы 471,46 и 67 образуют четвертый выход 27блока 4 режимов. Выходы 451, 461, 46,47 и 67 образуют шестой выход 29блока 4 режимов. Выходы 46 и 68 образуют седьмой выход 30 блока 4 режимов.Блок 5 триггеров кодов операций(фиг,4) содержит дешифратор 69 кодовопераций итриггеров 70 кодов операций и - число команд, используемойсистемы команд), выходы ВВ, которых образуют выход 32 блока 5 триггеров кодов операций, синхронизирующий вход которого соединен с синхронизирующими входами триггеров 70 кодов операций, входы которых соединены с выходами дешифратора 69 кодовопераций, входы которого соединены скодовым входом блока 5 триггеров кодов операций, соответствующим полюкодов операций в командном слове.Блок 6 подключения регистров операндов (фиг. 5) содержит регистр 71для хранения полей % и 17 командного слова, первую группу из К элементов И 72, вторую группу из Х элементов И 73, триггера 74, дна элемента И 75, элемент ИЛИ 76 и два инвертора 77,Выход 46, соединенный с управляющим входом блока 6 подключения регистров операндон, через иивертор 77 соединен с вторыми входами первой группы элементов И 72, выходы которых соединены с первым управляющим выходом 19 блока 6 подключения регистровоперандов, второй управляющий выход 20которого соединен с выходами второйгруппы элементов И 73, вторые входыкоторых соединены с выходом триггера 74, синхронизирующий вход которого соединен с выходом элемента ИЛИ 76.Выход элемента И 75 соединен с входом 4 зэлемента ИЛИ 76, с синхронизирующимвходом регистра 71 и с синхронизирующим выходом 31 блока 6 подключениярегистров операндов, вход конца команды которого соединен с первым входом элемента И 75. Выход 68, соединенный с управляющим входом блока 6 подключения регистров операндов, соединен с первым входом элемента И 75 ичерез инвертор 771 соединен с входом 55триггера 74. Первые входы первой группы элементов И 72 соединены с выходами поля 1регистра 71, выходы поля 0 2которого соединены с первыми входами второй группы элементов И 73, при этом выход младшего разряда поля регистра 1 соединен с выходом 38 признака блока 6 подключения регистров операндов, кодовый вход которого, соответствующий полям 1 и Я ко-1 0. мандного слова, соединен с входами регистра 71. Второй вход элемента ИЛИ соединен с выходом элемента И 5, второй вход которого соединен со вторым входом элемента И 75 и с тактовым входом блока 6 подключения регистров операндов.БлокФормирования стробов фиг.6) содержит коммутатор 78, дешифратор 79 записи, элемент ИЛИ-НЕ 80, элементы ИЛИ 811, 82, 81 и 2 элементовКИ 82, выходы 2 о.которых соединены с выходом 21 стробов блока 7 Формирования стробон, первый кодовый вход которого соединен с первой группой входов коммутатора 78, вторая группа входов которого соединена со вторым кодоным входом блока 7 формирования стробов, вход конца команды которого соединен с входом элемента ИЛИ-НЕ 80 и с четвертым входом элемента ИЛИ 81 1, второй и третий входы которого соединены с выходами 45. и 46, соединенными с первым управляющим входом блока 7 Формирования стробов, второй управляющий вход которого соединен с входом элемента ИЛИНЕ 80 и с четвертым входом элемента ИЛИ 81, третий и второй входы которого соединены со входами элемента ИЛИ-НЕ 80 и с выходами 46 и 47, соединенными с первым управляющим входом блока 7 формирования стробов, Выход элемента ИЛИ-НЕ 80 соединен с первым входом элемента ИЛИ 81, выход которого соединен с дополнительным входом дешифратора 79 записи, входы которого соединены с выходами коммута" тора 78, управляющий вход которого соединен со вторым входом элемента ИЛИ 81 и с выходом 67, соединенным с первым управляющим входом блока 7 Формированиястробов, третий управляющий вход и тактовый вход которого соединены со нторыми и третьими входами элементов И 82. Первый ныход дешифратора 79 записи соединен с первым входом элемента ИЛИ 811, выход которого соединен с первым входом элемента И 82,.КПервые входы элементов И 821-82 соединены с 12-2 -1) -ми выходамйК13 8дешифратора 79 записи, 2 -2 выход кокторого соединен с первым входом элемента И 82Блок 8 управления Фиг. 7) содержит сдвиговый регистр 83 управления,сборки 84 и 85, Ы сборок 86 (О - количество управляющих микроопераций операционного блока 1), сборку 87, рсборок 88 (р - определяется числомвыходов результатов операционного блока 1,таких как сумма, поразряднаясумма, поразрядный перенос и т.п.,причем 2 ) числа выходов результаКтов), элементов И 89, элементов И 90,В+с+д+е элементов И 91, элементов И 92и Ь++ и. элементов И 93.Выходы сдвигового регистра 83 управления образуют и выходов Л, гдеп определяется числом машинных цикловдля выполнения самой длинной командыиз системы команд. Числа а, в, с, де, 9, ЬС 1 определяются числом команд из системы команд, в которых вырабатываются управляющими микрооперации на выходах соответствующих сборок. Кодовый вход блока 8 управлениясоединен с выходами В 1Вп триггеров 70,1 -70 п 1 кодов операций,Выход 46, соединенный с вторымуправляющим входом блока 8 управления, соединен с входами сборок 84,861 и 86. Выход 67, соединенный,свторым управляющим входом блока 8 управления, соединен с входами сборок 86 и 86. Выход 471, соединенныйс вторым управляющим входом блока 8управления, соединен с входом сборки 86 и входом сборки 84, выход которой соединен с четвертым выходом 39блока 8 управления, тактовый вход которого соединен с синхронизнрующимвходом сдвигового регистра 83 управления, вход которого соединен с третьим управляющим входом блока 8 управления, первый управляющий вход которого соединен с входами сборок 84и 87. Выходы сборки 87 и элемента И 92соединены с первым выходом 35 блока 8управления, второй выход 36 которогосоединен с выходами сборок 861,863,Выход сборки 85 соединен с входамисборок 84 и 87, управляющим входомсдвигового регистра 83 управления ис выходом 33 конца команды блока 8управления, третий выход 37 которогосоединен с выходами сборок 88188.Первые входы элементов И 89189 соединены с выходами А,А55 мать от единицы до и для 1 и 1 и от единицы до щ для т и С и определяются алгоритмами выполнения каждой конкретной команды из системы команд.Если для выполнения некоторой коман 90400 14сдвигового регистра 83 управления,вторые входы элементов И 8989 гсоединены с выходами ВВ триггеров 70 кодов операций, а выходыэлементов И 89 89, соединеныс входами сборки 84. Первые и вторыевходы элементов И 9090 а соединены соответственно с выходами АА сдвигового регистра 33 управленияи В,В триггеров 70 кодов операций, а выходы элементов И 90,90соединены с входами сборки 85, дополнительный вход которой соединен свыходом А и последнего разряда сдвигового регистра 83 управления. Входыэлементов И 91. . .91 соединены со"ответственно с выходами АА сдвигового регистра 83 управления иВ Втриггеров 70 кодов операций,при этом выходы элементов И 91191 есоединены со входами сборки 86, выходы элементов И 911 9 о - со входами сборки 86, выходы элемеитовИ 91,91 - со входами сборки865, выходы элементов И 9 ,91 со входами сборки 86 р.Первый вход элемента И 92.1 соединен с выходом 68 элемента ИЛИ 64 блока 4 режимои, подключенного черезседьмой выход 30 блока 4 режимов кчетвертому управляющему входу блока 8управления, Второй вход элемента И 921подключен к выходу Ве триггера 70 ркода операции, соответствующему ко- манде "Запись" в "Память". Первые ивторые входы элементов И 9292соединены соответственно с выходами А;А сдвигового регистра ВЗуправления и выходами Вг,..,В 4триггеров 70 кодов операций, в выходы40элементов И 9292 соединены совходами сборки 87.Первые и вторые входы элементовИ 93193соединены соответственно с выходами А;А сдвигового45 регистра 83 управления и с выходамиВгВ триггеров 70 кодов операций, при этом выходы элементовИ 93193 соединены со входамисборки 8888, выходы элемен 50 тов И 93 93 соединены с входами сборки 88 р,Индексы 1, 1, г и й - переменные, значение которых может приниСборка 84 обеспечивает разрешение записи информации в регистры 40 общего назначения. Сборка 87 служит для выработки сигнала обращения к блоку 2 памяти, а элемент И 921 служит для выработки сигнала записи в блок 2 памяти. Сборка 85 служит для выработки сигнала в конце выполнения каждой ко 30 манды. Соединение выхода А сдвигового регистра 83 управления непосредственна со входом сборки 85 служит дляисключения прекращения работы центрального процессора при ошибках при программировании, когда программист35 потребует выполнения команды, отсутствующей в системе команд, при которой не включится ни один из триггеров 70 кодов операций.Сдвиговый регистр 83 управления40(Лиг. 8) содержит элемент ИЛИ 94,й триггеров 95, Ъ элементов И 96, элемент ИЛИ-НЕ 97 и инвертор 98,. выход которого соединен с вторым входом элемента И 96, первый вход которого 45 соединен с выходом элемента ИЛИ 94, первый вход которого соединен с выходом бб, соединенным с входом сдвигового регистра 83 управления, синхронизирующий вход которого соединен с 50синхронизирующими входами триггеров 951-95, входы которых соединены с выходами элементов И 96-96.Второй вход элемента ИЛИ-НЕ 97 соединен со вторым входом элемента ИЛИ 9455 и с выходом 68, соединенным с входом сдвигового регистра 83 управления, управляющий вход которого соединен ды в соответствующем машинном цикле ее выполнения необходимо выработать определенную микрооперацию, то на выходе соответствующей сборки устанавливается элемент И, на входы которых поступают выходы триггера кода операции и соответствующего разряда сдвигового регистра 83 управления.Сборка 86 обеспечивает подачу в операционный блок 1 первого операнда прямым кодом, сборка 86 обеспечивает подачу в операционный блок 1 второго операнда прямым кодом, сборка 86 обеспечивает подачу единицы переноса в младший разряд для операционного блока 1 и т.д,Сборки 88188 обеспечивают настройку коммутатора 12 результата на пропускание результата в блок 3 регистров с соответствующего выхода операционного блока 890400с первым входом элемента ИЛИ-НЕ 97,выход которого соединен со вторымивходами элементов И 961-96, первыевходы которых соединены соответственно с выходами триггеров 951-95Выходы триггеров 95-95 образуют выходы А-А сдвигового регистра 83 управления.Коммутатор 41 адреса (фиг. 9) со 1 О держит дешифратор 99 и элементИ-ИЛИ 100, выход которого соединен свыходом коммутатора 41 адреса, первый,второй и третий входы которогосоединены с первыми входами соответственно первого, второго и третьеговентилей элемента И-ИЛИ 100, вторыевходы которых соединены соответственно с первым, вторым и третьим выходами дешифратора 99, входы которого соединены с входом коммутатора 41 адреса.Триггер 48 ( 70, 74, 95) (фиг. 10) сосодержит элементы И-ИЛИ 101 и 102 иинверторы 103 и 104. Выход триггера 48 соединен с выходом элементаИ-ИЛИ 101 и с первым входом первоговентиля элемента И-ИЛИ 101, второйвход которого соединен с синхронизирующим входом триггера 48 и с входоминвертора 104, выход которого соединен с входом инвертора 103 и с вторыми входами вторых вентилей элементов И-ИЛИ 1 О 1 и 102, первые входы которых соединены с выходом элемента И-ИЛИ 102, второй вход первого вентиля которого соединен с выходом инвертора 103. Вход триггера 48 соединен с первым входом первого вентиляэлемента И-ИЛИ 102.Сдвиговые регистры 45-47 выполнены на триггерах аналогичных триггеру 48, причем вход последующего разряда регистров 45-47 соединен с выходом их предыдущего разряда.Регистры 40 и 71 выполнены на триггерах аналогичных триггеру 48 (70,74, 95).Триггер 48 (70, 74, 95) работаетследующим образом.При появлении. сигнала на его синхронизирующем входе элемент И-ИЛИ 101запоминает состояние своего выхода,являющегося выходом триггера 48. Навыходе инвертора 104 сигнал пропадает, поэтому вторые вентили элементов И-ИЛИ 101 и 102 закрыты, а сигналом, образуемым на выходе инвертора 103, первый вентиль элемента И-ИЛИ 102 открыт, при этом выход эле890400 40 мента И-ИЛИ 102 повторяет состояниевхоца триггера 48,При пропадании сигнала на синхронизирующем входе триггера 48 первыйвентиль элемента И-ИЛИ 101 закрыва 5ется, а на выходе инвертора 104 появляется сигнал, который открываетвторые вентили элементов И-ИЛИ 102и 101, при этом элемент И-ИЛИ 102запоминает состояние его выхода, аэлемент И-ИЛИ 101 передае это состояние на выход триггера 48, Такимобразом, триггер 48 представляет собой О-триггер.Коммутатор 41 адреса работаетследующим образом.При коде "00" на входе дешифратора 99 сигнал появляется только наего первом выходе, открывая толькопервый вентиль элемента И-ИЛ( 100,связанный первым входом с первым входом коммутатора 41 адреса. При коде"01" на входе дешифратора 99 аналогичиьм образом на въход коммутатора 41адреса передается только состояниеего второго входа, а при коде "1 О"на входе дешнфратора 99 на выход коммутатора 41 адреса передается толькосостояние его третьего входа. Причемкод "ОО" на вход дешифратора 99 по 30ступает при отсутствии сигналов навыходах элементов И 59 и ИЛИ 60, код"01" - при отсутствии сигнала на вы ходе элемента ИЗ% 60 и при появлениисигнала на выходе элемента И 59, акод "10" - при отсутствии сигнала иавыходе элемента И 59 и и явлении сигнала иа выходе элемента ИЛИ 60 в блоке 4 режимов, Совместное появлениесигналов на выходах элементов И 59и ИЛИ 60 исключено.Сдвиговый регистр 83 управленияработает следующим образом.При отсутствии сигналов на входахэлемента ИЛИ-НЕ 97 (соответствует отсутствию сигналов на выходе сборки 85 в блоке 8 управления и на выходе элемента ИЛИ 64 в блоке 4 режимов)элемент И 961 закрыт, так как отсутствует сигнал на выходе инвертора 98,а элементы И 96-96 открыты сигналомс выхода элемента ИЛИ-НЕ 97,Поэтому при поступлении каждогосинхросигнала на синхронизирующем входе сдвигового регистра 83 управления,в триггер 95-1 загисывается нуль, а 55в триггеры 95 -95 и - состояние предшествующего ему триггера. При наличиисигнала на управляющем входе сдвиго 8вого регистра 83 управления, соединенного с выходом сборки 85, на выходеэлемента ИЛИ-НЕ 97 сигнал отсутствует,а на выходе пнвертора 98 вырабатывается сигнал и при появлении синхросигнала на синхронизирующем входе сдвигового регистра 83 управления в триггеры 95-95 запишутся нули, а в триггер 95 - единица, если на выходе 66элемента И 65 в блоке 4 режимов вырабатывается сигнал и запишется нуль,если этот сигнал не вырабатывается,при этом появление сигналов на первомвходе элемента ИЛИ-НЕ 97 и его второмвходе, связанном с выходом 68 элемента ИЛИ 64 в блоке 4 режимов, невозможно. При появлении сигнала на выходе 68 элемента ИЛИ 64 сигнал поступает, с одной стороны, на вход элемента ИЛИ-НЕ 97 и с другой стороны -через элемент ИЛИ 94 на вход элемента И 961, поэтому при поступлениисннхросигнала на синхронизирующийвход сдвигового регистра 83 управления в триггер 95 запишется единица,а в триггеры 95 -95 запишутся нули.По окончанию действия сигнала на управляющем входе и входе сдвиговогорегистра 83 управления он переходитв режим сдвига своего состояния, какописано выше,Центральный процессор работаетследуОщим образом,В конце выполнения очередной команды на выходе одного из элементов И 90 вырабатывается сигнал и поступает в качестве сигнала окончаниякоманды (ОК) на выходе сборки 85 исоответственно на выход 33 ОК блока 8управления. При этом сдвиговый регистр 83 переходит из режима сдвигав режим записи, на выходе сборки 84вырабатывается сигнал и поступает навыход 39 блока 8 управления, на выходе сборки 87 вырабатывается сигнал,который с выхода 35 блока 8 управления поступает на управляющий входблока 2 памяти в качестве сигнала обращения. На адресный вход блока 2 памяти подается адрес очередной команды содержимое регистра 40,), такКкак сигналы на выходах элемента И 59и элемента ИЛИ 60 отсутствуют и коммутатор 41 адреса пропускает код спервого своего входа на выход, Сигнал ОК, поступая на вход КК блока режимов, открывает по первым входам элементы И 60, 50-53 и 65 и через первыйвход элемента ИЛИ 61 поступает на вы

СмотретьЗаявка

2907173, 07.04.1980

ПРЕДПРИЯТИЕ ПЯ А-7160

СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, АЛЕКСЕЕВ ЮРИЙ ГАВРИЛОВИЧ, БЕСТАНЬ ГЕННАДИЙ СЕРГЕЕВИЧ, КОНОРЕВ БОРИС МИХАЙЛОВИЧ, НЕСТЕРЕНКО ЮРИЙ ГРИГОРЬЕВИЧ, НОВИКОВ НИКОЛАЙ ИВАНОВИЧ, ЩЕРБАЧЕНКО ВИТАЛИЙ ТРОФИМОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: процессор, центральный

Опубликовано: 15.12.1981

Код ссылки

<a href="https://patents.su/24-890400-centralnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Центральный процессор</a>

Предыдущий патент: Мажоритарное устройство

Следующий патент: Электронная клавишная вычислительная машина

Случайный патент: Устройство для загрузки легкоповреждаемых предметов в тару